题目:

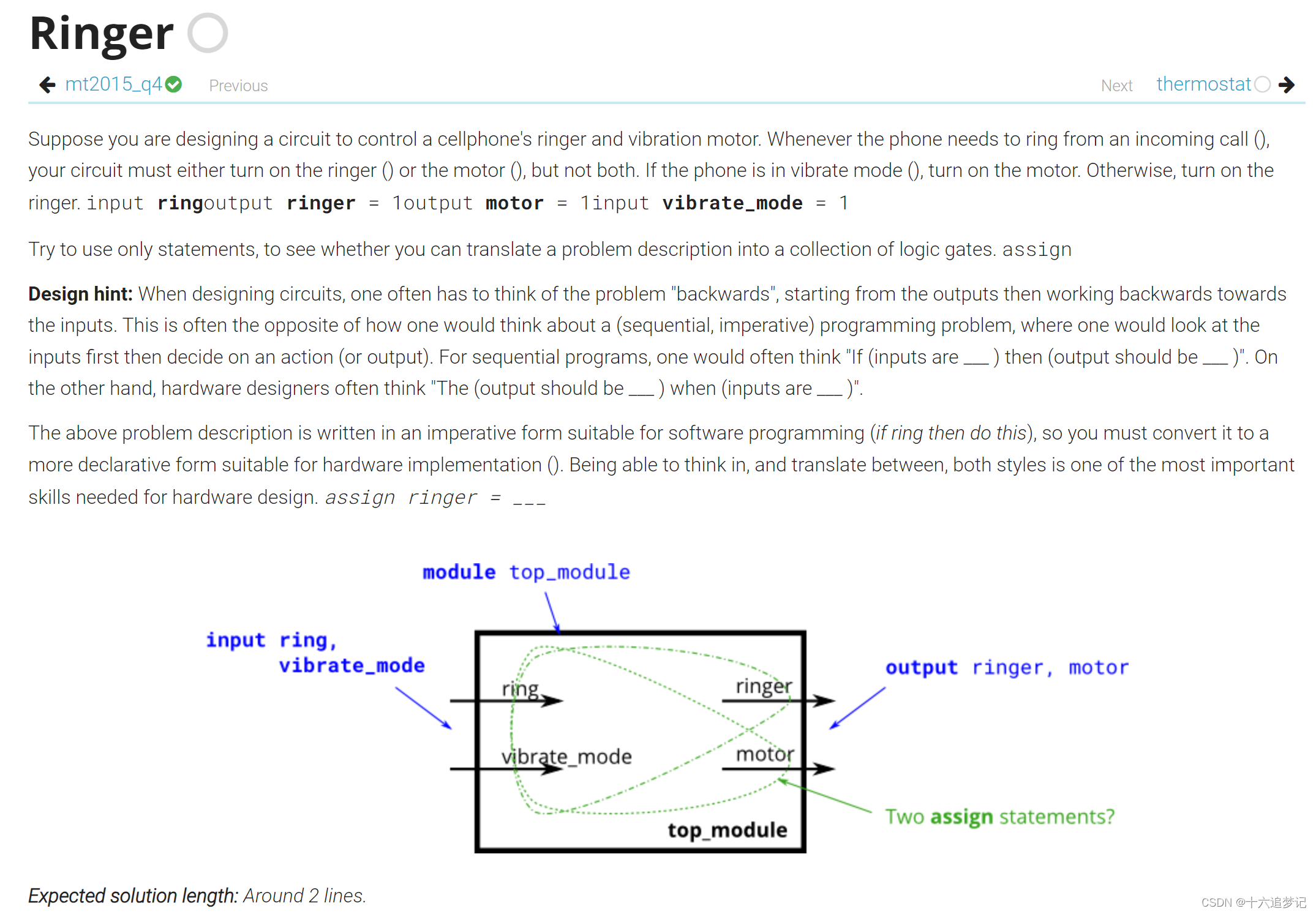

Suppose you are designing a circuit to control a cellphone’s ringer and vibration motor. Whenever the phone needs to ring from an incoming call (), your circuit must either turn on the ringer () or the motor (), but not both. If the phone is in vibrate mode (), turn on the motor. Otherwise, turn on the ringer. input ringoutput ringer = 1output motor = 1input vibrate_mode = 1

Try to use only statements, to see whether you can translate a problem description into a collection of logic gates. assign

Design hint: When designing circuits, one often has to think of the problem “backwards”, starting from the outputs then working backwards towards the inputs. This is often the opposite of how one would think about a (sequential, imperative) programming problem, where one would look at the inputs first then decide on an action (or output). For sequential programs, one would often think “If (inputs are ___ ) then (output should be ___ )”. On the other hand, hardware designers often think “The (output should be ___ ) when (inputs are ___ )”.

The above problem description is written in an imperative form suitable for software programming (if ring then do this), so you must convert it to a more declarative form suitable for hardware implementation (). Being able to think in, and translate between, both styles is one of the most important skills needed for hardware design. assign ringer = ___

我的解法:

module top_module (

input ring,

input vibrate_mode,

output ringer, // Make sound

output motor // Vibrate

);

always@(*)

begin

if(vibrate_mode==1&ring==1)

begin

ringer=0;

motor=1;

end

else if(vibrate_mode==0&ring==1)

begin

ringer=1;

motor=0;

end

else

begin

ringer=0;

motor=0;

end

end

endmodule

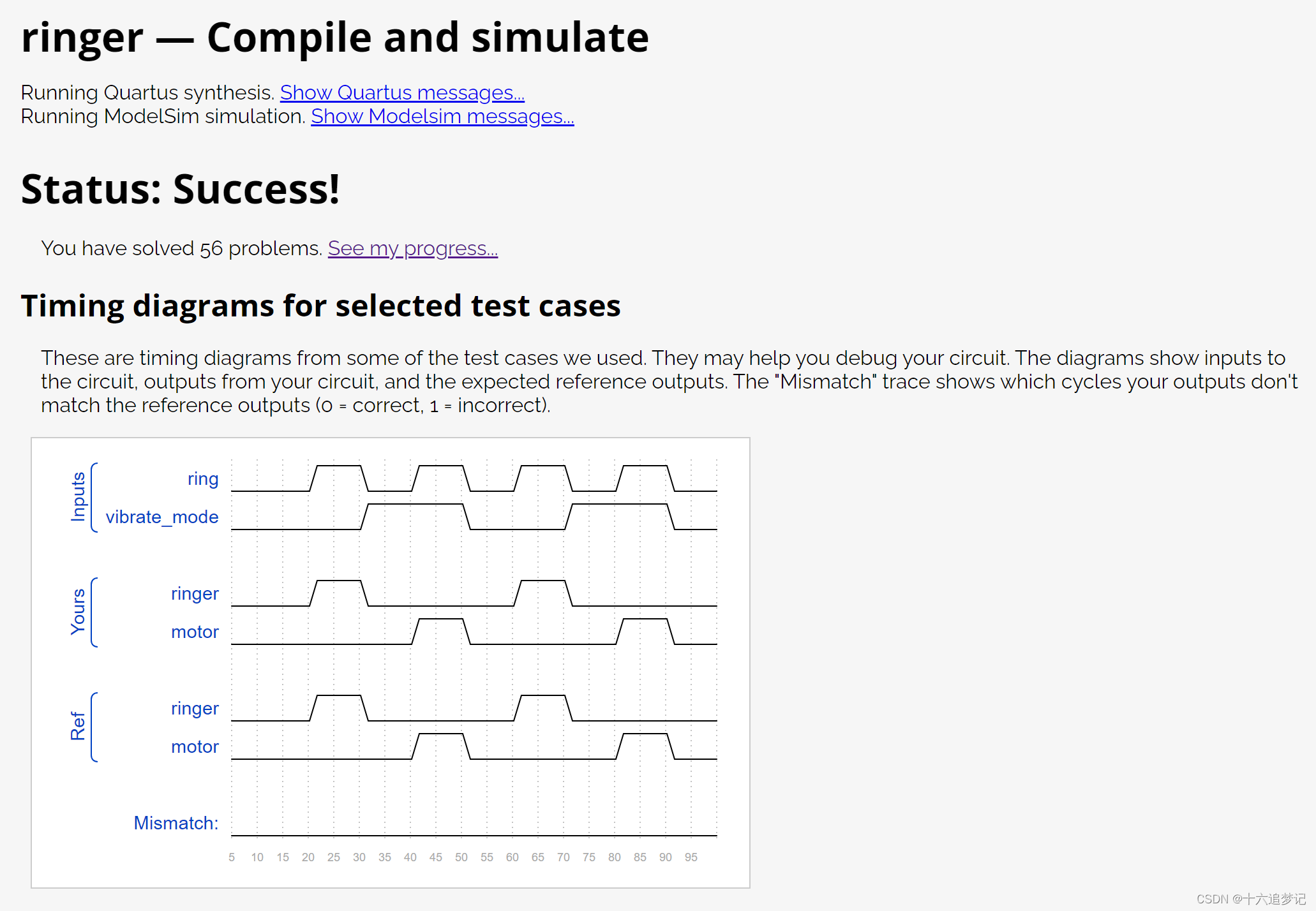

结果正确:

参考解法:

1.直接使用assign语句进行赋值:

module top_module (

input ring,

input vibrate_mode,

output ringer, // Make sound

output motor // Vibrate

);

assign ringer = ring & (~vibrate_mode);

assign motor = ring & vibrate_mode;

endmodule

2.利用always来触发:

module top_module (

input ring,

input vibrate_mode,

output ringer, // Make sound

output motor // Vibrate

);

always@(ring)begin

if(ring == 0)begin

ringer = 0;

motor = 0;

end

else begin

if(vibrate_mode ==0)begin

ringer = 1;

motor = 0;

end

else begin

ringer = 0;

motor = 1;

end

end

end

endmodule

注意点:注意两者赋值方法的不同。

161

161

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?