参考:

DDR4的刷新_ddr刷新间隔_jh你好的博客-CSDN博客

LPDDR4x 的 学习总结(2) - SDRAM array存储结构浅识 - 知乎

LPDDR4x 的 学习总结(3) - SDRAM CELL基本功能 - 知乎

LPDDR4x 的 学习总结(4) - SDRAM chip的组织结构 - 知乎

LPDDR4x 的 学习总结(5) - SDRAM chip的读写操作 - 知乎

LPDDR4x 的 学习总结(6) - initialization & training - 知乎

备注:

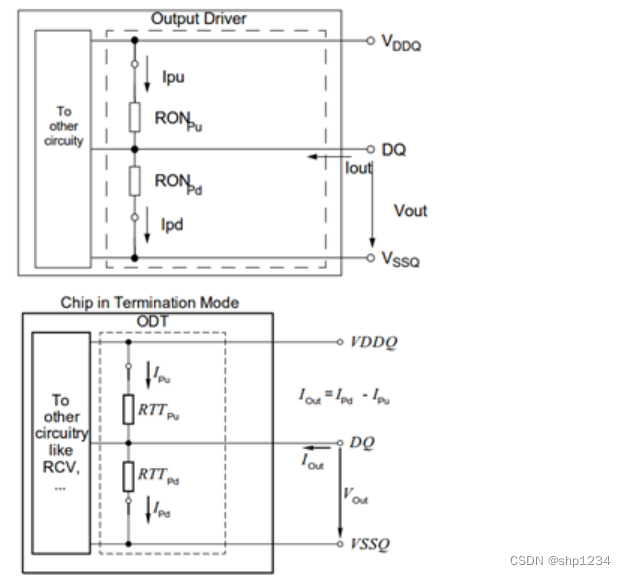

ODT:On-Die Termination,即Die上的终端电阻,Die是硅片的意思,这里也就是DDR颗粒。目的是为了让DQS、RDQS、DQ和DM信号在终结电阻处消耗完,防止这些信号在电路上形成反射,进而增强信号完整性。其允许用户通过读写MR1寄存器,来控制DDR3 SDRAM中内部的终端电阻的连接或者断开。

参考:DDR中ODT(on-die termination)_ddr odt_daizongjun的博客-CSDN博客

RTT:DDR输入结构的上下拉电阻。

RON:DDR的输出结构的上下拉电阻。

VTT: 数值上等于1/2VDDQ,需要专门的芯片同时提供,且既有驱动能力,也能吸收电流; VTT为DDR的地址线,控制线等信号提供上拉电源,上拉电阻是50Ω左右。VTT=1/2VDDQ,并且VTT要跟随VDDQ,因此需要专用的电源同时提供VDDQ和VTT。

参考:DDR,DDR2,DDR3,DDR4,LPDDR区别讲解_ddr 技术区别_夜灼华的博客-CSDN博客

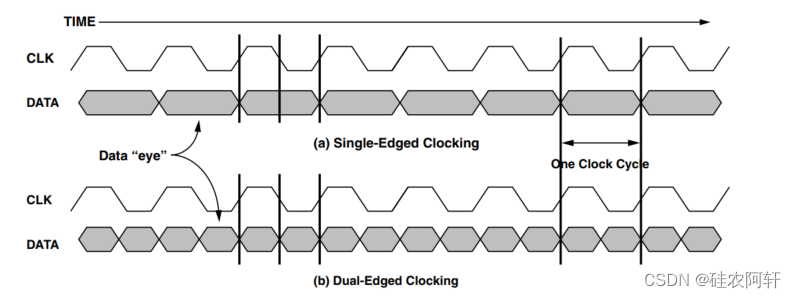

Data "eye":指一块“菱形”数据。

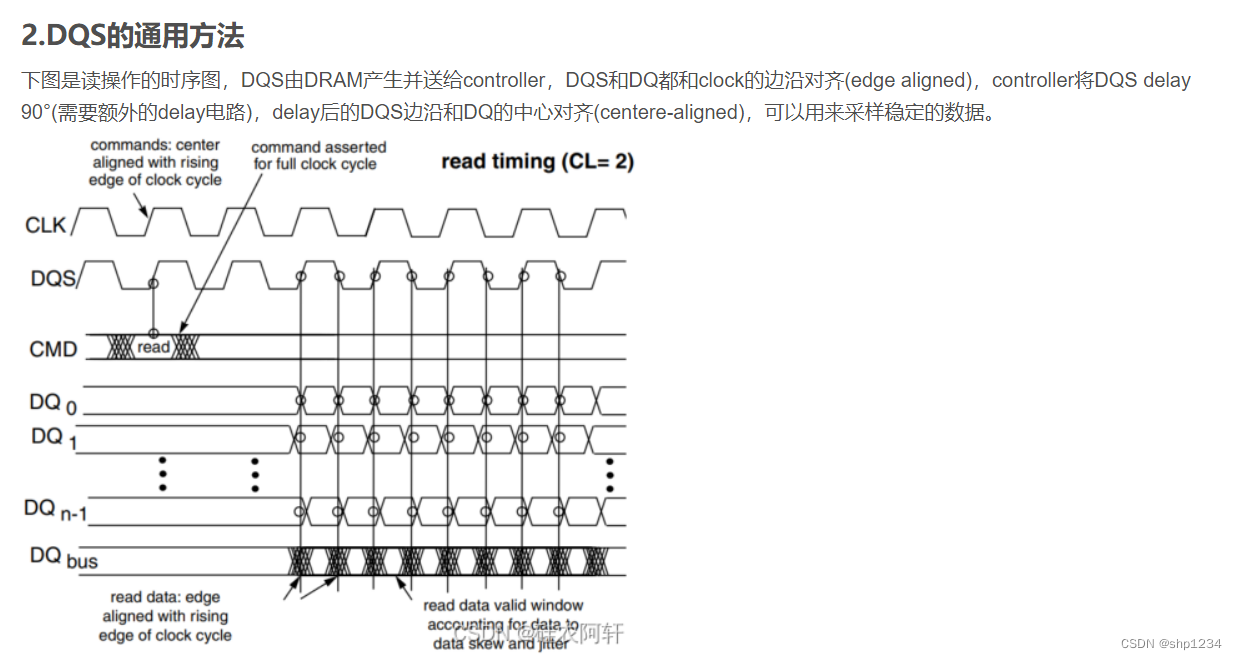

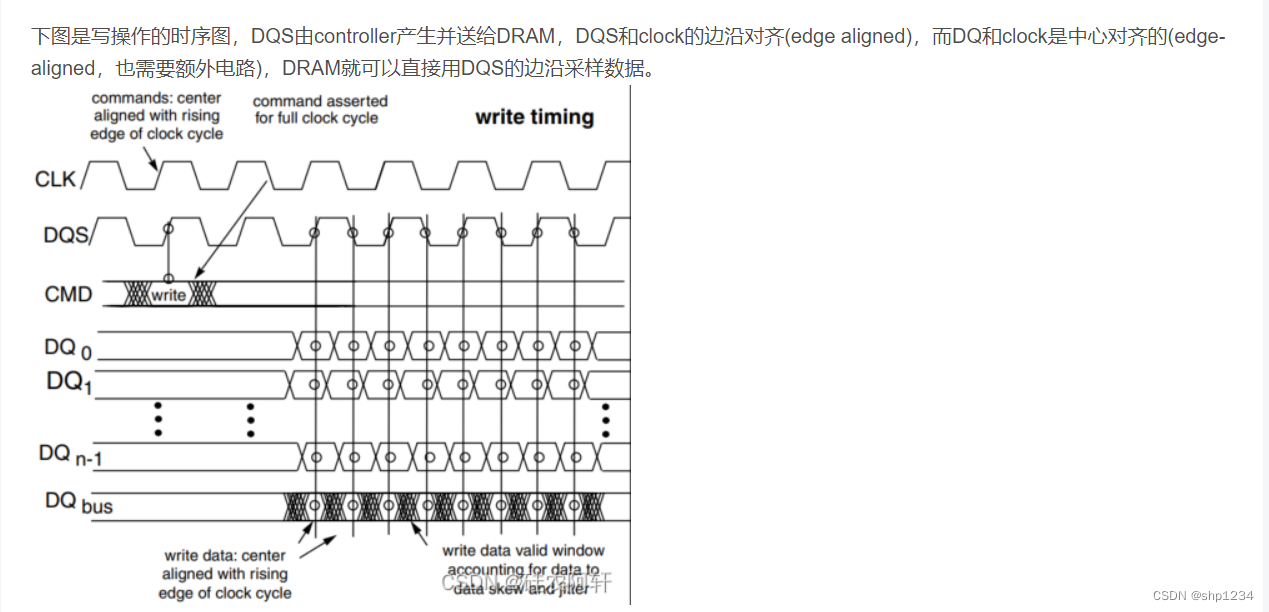

DQS delay 90°:正弦函数sinx一个周期的x范围是(0,2π),即(0,360°),延迟90°,即周期不变,相位往后移动1/4,也就是往后倒移动高电平或者低电平长度的一半。

可以看到,写操作和读操作中的DQS、DQ、clock的关系是不同的,且都需要controller提供额外的电路来保证它们的关系,原因DRAM通常是大规模生产,把额外电路的负担都放到controller一侧,可以降低DRAM的成本。

DDR信号传输时间的uncertainty(不确定性),通常由skew(时钟偏移)和jitter(时钟抖动)两部分组成。

为了减小时序收敛难度,DDR不是将所有DQ线的时序同时进行约束,而是将它们每8个bit为1组,且每一组都有自己的DQS信号。

参考:DDR为什么需要DQS信号?_硅农阿轩的博客-CSDN博客

图中左边标题栏命名怪异,不方便阅读,作如下修改:要么如“ddr_caa0”,去掉多余的一个“a”,变为“ddr_ca0”;要么如“ddr_ckea0”,去掉多余的“a0”,变为“ddr_cke”。

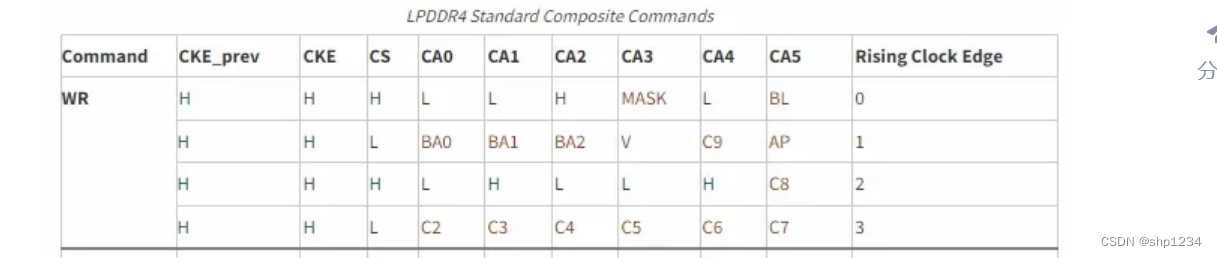

图中DDR4的“WR”命令由四个时钟组成,每个时钟上升沿时候的CKE、CS、CA0~5要设置的具体的值。

CKE 是激活sdram内部时钟电路, 是CS和CA的command的一部分。

CKE:clock enable.

CA: command/address input.

ma: mode register address

op:operation value (mode register value).

参考:LPDDR4x 的 学习总结(7)-接口读写时序 - 知乎

precharge:

如图中间部分红色单词标记处“Vref(Vcc/2)”,电压是Vcc/2,EQ拉高后, Te1、Te2、Te3 晶体管处于导通状态,位线Bitline 和 /Bitline 的电压都是Vref (= Vcc/2) 。

access:

图中左边部分,“)|”表示电容(电容的另一种表示方式),“)”表示阴极,“|-----”用于“标识说明”,这里表示电容电压Vcc/2(充电就会有电压)。

sense:

图中三极管上的小圆圈表示低电平选通。开始时,Bitline和/Bitline都是高电平, Tp1,Tp2都是低电平选通,所以不用管;而Tn1、Tn2都是高电平选通,此时由于Tn2的选通电压更高,/Bitline更快被拉低,此时Bitline还为高,由于/Bitline被拉低,Tn1截止,Tp1选通,Bitline又被拉的更高,所以Tp2一直处于截止状态。

参考:LPDDR4x 的 学习总结(3) - SDRAM CELL基本功能 - 知乎 (zhihu.com)

skew和jitter

skew:时钟偏移,如一个时钟源到达两个不同寄存器时钟端的时间便宜。

Jitter:时钟抖动, 指两个时钟周期之间存在的差值,这个误差是在时钟发生器内部产生的,和晶振或者PLL内部电路有关,布线对其没有影响。如下图所示:Jitter=T2 - T1 ;

参考:时钟偏移(Skew)和时钟抖动(Jitter)_group skew时钟_硬是要得的博客-CSDN博客

DDR内存参数:

参考:DDR内存参数笔记_51CTO博客_DDR内存主要参数

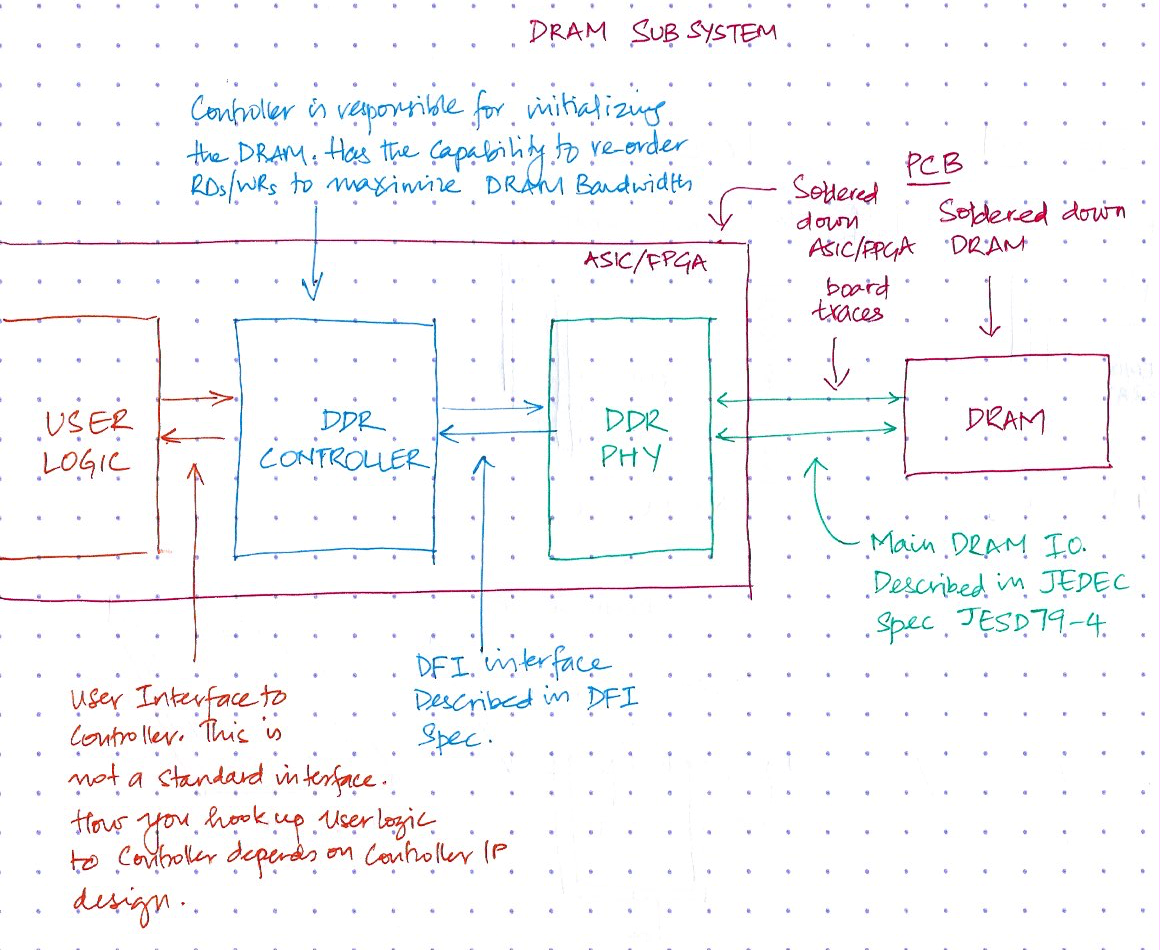

DFI:DDR phy接口。DFI是一种接口协议,用于定义DRAM之间和MC(微控制器)和PHY之间传输控制信息和数据所需的信号、时序和可编程参数。

or

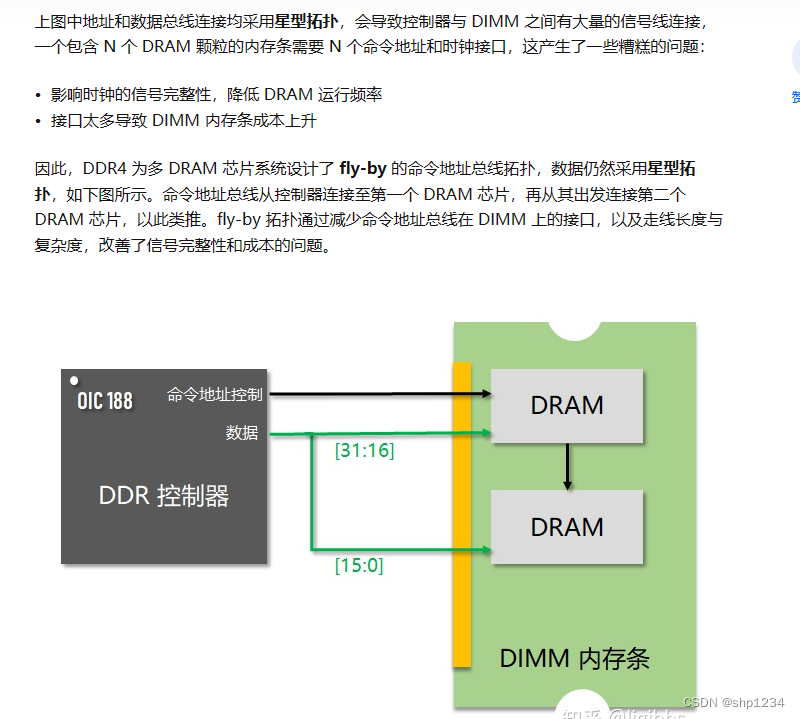

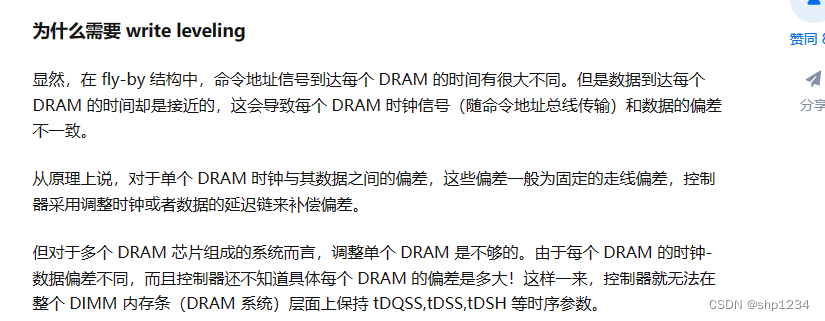

write leveling(写平衡):

参考:DDR 学习时间 (Part B - 3):Write Leveling - 知乎 (zhihu.com)

图中dqs的相位延迟时间应该是开始到t4这段时间。

参考:LPDDR4x 的 学习总结(6) - initialization & training - 知乎 (zhihu.com)

LPDDR4的规格书和其它资料:

链接:https://pan.baidu.com/s/1IiybOxzvagEgLHJJ_-yy8g

提取码:cvvj

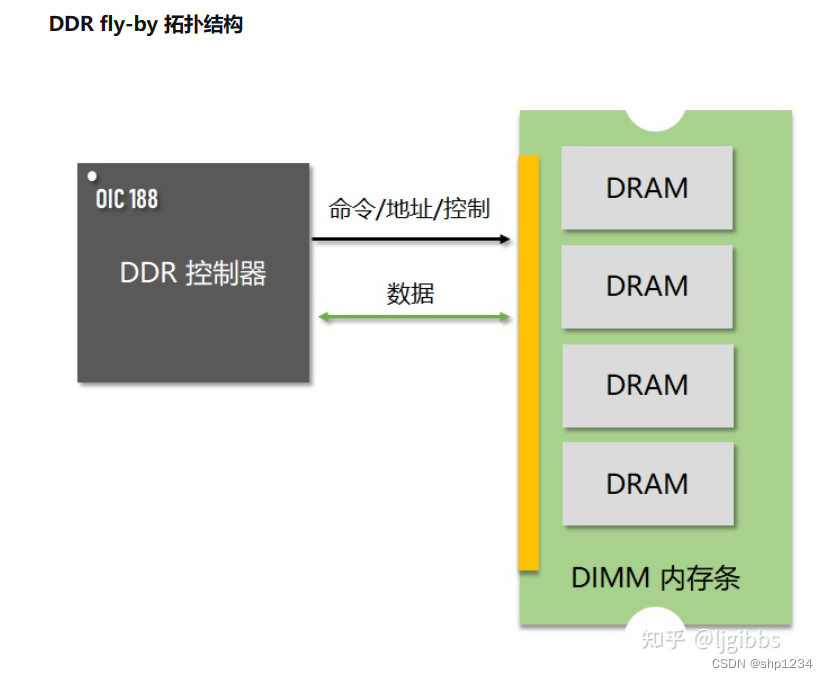

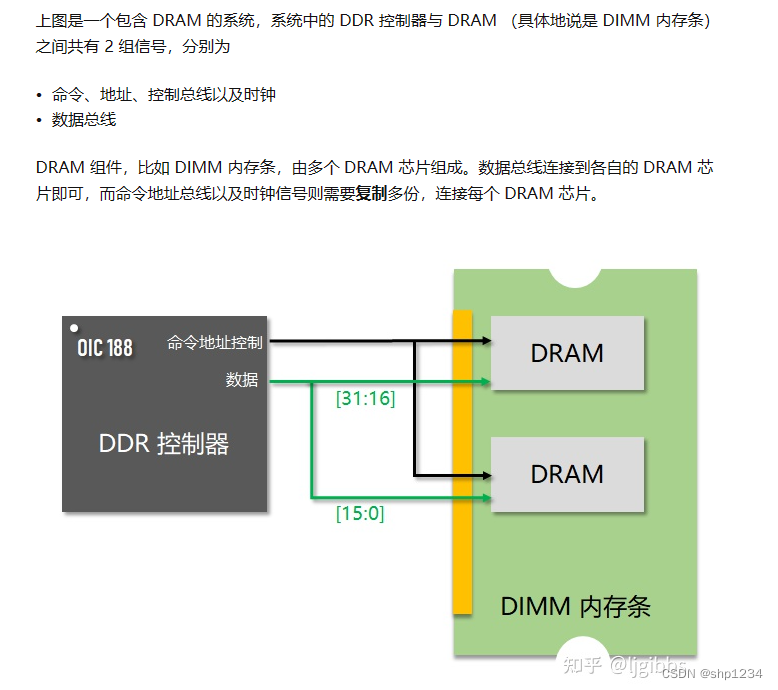

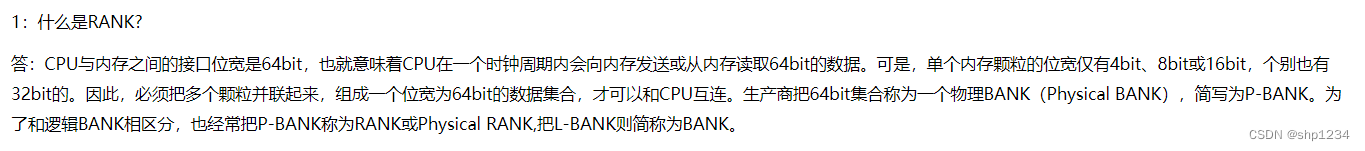

Rank的概念:

参考:

https://www.cnblogs.com/jason20/p/14699529.html

DDR的Controller、Channel、Chip、Rank、Bank、Row、Column、Sided、Dimm_ddr rank_张飞online的博客-CSDN博客

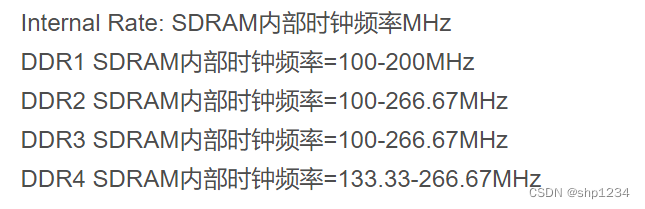

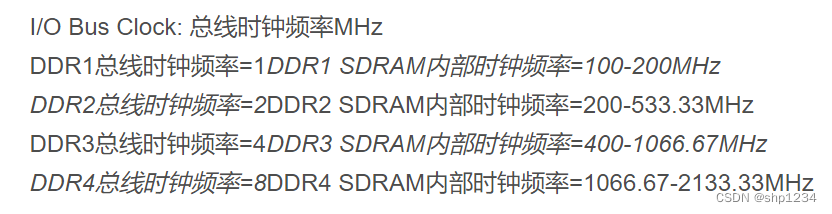

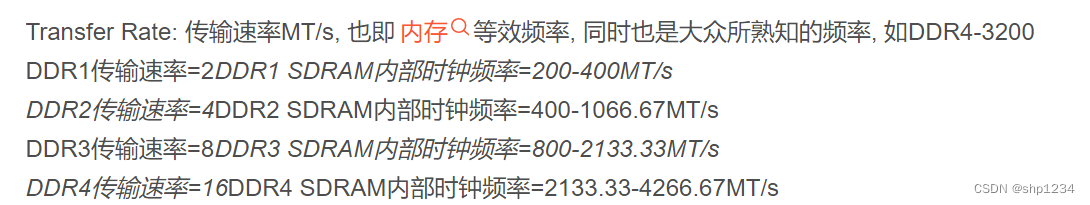

DDR4内部时钟、总线时钟、等效时钟:

等效频率是总线频率的两倍,是双边沿采样的原因。

MT/s全称 Million Transfers Per Second意为每秒百万次传输。

参考:JEDEC标准的DDR频率_jedc标准_hbcbgcx的博客-CSDN博客

行列地址:

内存地址={行地址,列地址}

列地址在低位,一个列地址对应一个存储单元,如{0010,0000}、{0010,0001}、{0010,0010}、{0010,0011},一个存储单元对应一个存储字长,总容量=存储单元个数x存储字长。

一行对应多个列,如{0001,0000~ffff}。

片选选中的是rank。

参考:DDR基础知识点杂记_ddr dbi_wqh_硬件菜鸟的博客-CSDN博客

DFI:

DDR PHY Interface (DFI) Specification - Fudan University:DDR PHY接口(DFI)规范-复旦大学 - 豆丁网

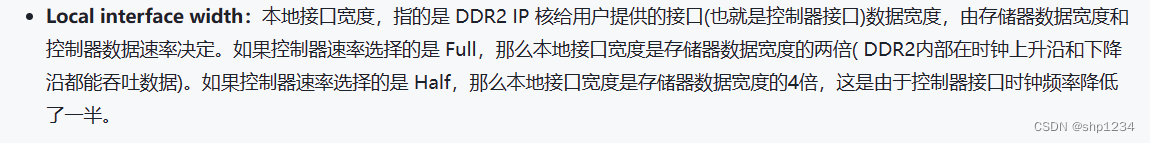

half rate和full rate:

![]()

控制器接口数据是单边沿采样,存储器(如DDR2设备)是双边沿采样数据。

Memory burst length(存储器突发长度):设置每个传输读取或写入字的数量。 单位:beats 范围:4 or 8

存储器突发长度为4 等同于半速率设计中本地突发长度为1(四分之一),也等同于全速率设计中本地突发长度为2(二分之一)。

注:DDR参数可以参考该链接。

参考:DDR2(2):Quartus DDR2 IP 官方例程仿真 - 咸鱼IC - 博客园 (cnblogs.com)

1547

1547

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?