有符号数间比较,及有符号数与常数比较

Verilog代码示例

module data_cmp#(

parameter DW = 16

)(

input signed [DW-1:0] a1,

input signed [DW-1:0] b1,

input signed [DW/4-1:0] a2,

input signed [DW/4-1:0] b2

);

// constant : Two different ways of expressing it

// 常数:不同的表示方式

localparam MAX = -4'h2;

wire signed [3:0] MIN = 4'he; // -2

// Truncate a signed variable: Truncate the high [15:12] comparison

// 截断:将输入16bits数截取高4bits,并用有符号变量表示

wire signed [DW/4-1:0] aa2, bb2;

assign aa2 = a1[DW-1:DW-1-3];

assign bb2 = b1[DW-1:DW-1-3];

// Signed number comparison : TURE/ERROR

// 有符号数比较:结果正确/错误

assign cmp0 = a1 > b1; // 16b, TURE

assign cmp1 = a2 > b2; // 4b, TURE

assign cmp2 = aa2 > bb2; // high 4b, TURE

assign cmp3 = $signed(aa2) > bb2; // TURE

assign cmp4 = $signed(aa2) > $signed(bb2); // TURE

// Signed numbers are compared with constants : TURE/ERROR

// 有符号数与常数比较:结果正确/错误

assign cmp5 = aa2 > MAX; // ERROR

assign cmp6 = $signed(aa2) > MAX; // ERROR

assign cmp7 = aa2 > MIN; // TURE

assign cmp8 = $signed(aa2) > MIN; // TURE

endmodule

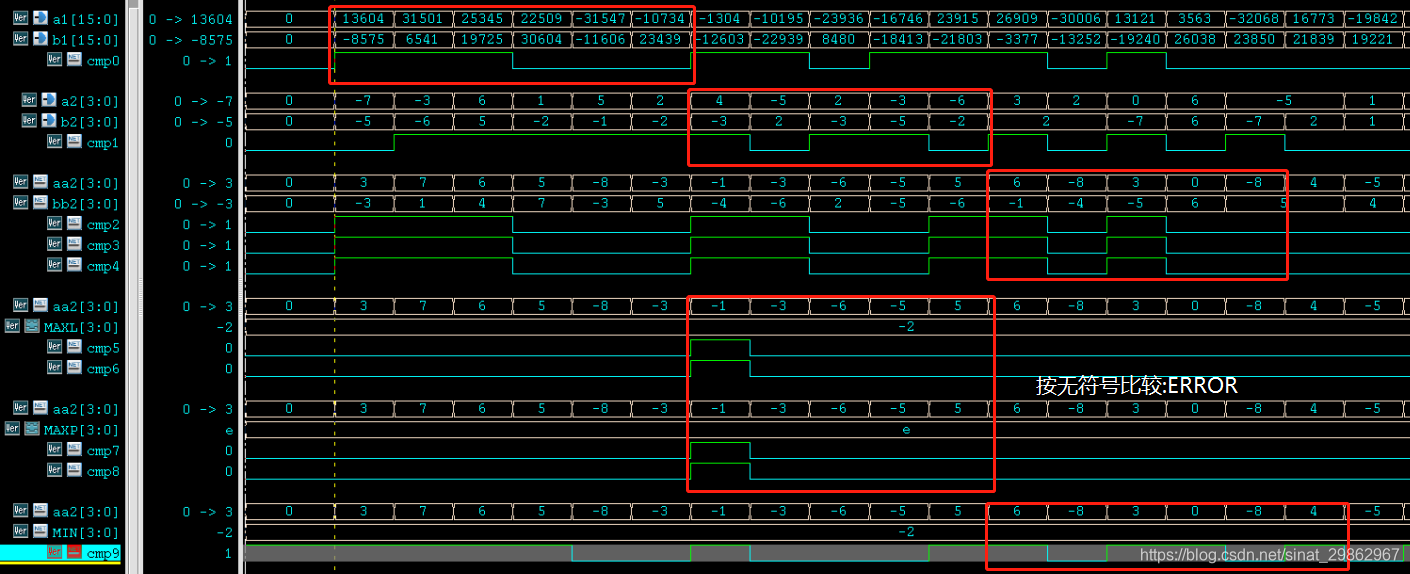

Verdi仿真波形

结论

1、有符号数之间比较:可用过signed关键字标注,可得到正确结果;

2、有符号数与常数比较:使用localparam、parameter定义的一定bit位宽的有符号常数(如4bits),依然按无符号比较;但是如果定义时不标注bit位宽(直接localparam MAX = -2),是可以比较正确的;

3、有符号数与常数比较:使用wire定义的有符号常量(其实是变量),会按照有符号数进行比较;

综上,localparam、parameter定义的一定bit位宽的常量,在常量和变量比较时按照无符号比较;而为什么wire定义的一定bit位宽的变量与变量比较,是按照变量间有符号比较;

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?