在数字IC后端,有对晶体管的偏差建模的PVT corner,以及对互连线偏差建模的RC corner。

芯片的延迟一般受到三个因素的影响:工艺(Process)、电压(Voltage)、温度(Temperature)。合起来称为PVT参数。在实际生产中,实际使用中,都会对这三个因素产生影响,从而影响晶体管性能,继而影响影响芯片性能。

process corner

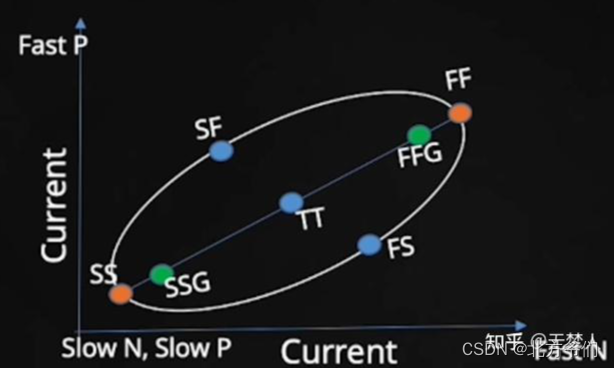

晶体管CMOS中以NMOS和PMOS的影响不同,可以分为以下五种process corner:

TT (typical nmos and typical pmos):Nominal

SS (slow nmos and slow pmos):Slow N Slow P

FF (fast nmos and fast pmos):Fast N Fast P

SF (slow nmos and fast pmos):Slow N Fast P

FS (fast nmos and slow pmos):Fast N Slow P

一般我们在后端综合的时候,需要设置几个corner case(一般是best case 和 worst case)来进行约束和分析,还有PVT(process voltage temperature)参数

best case 对应ffg、low temperature、high voltage(可以跑的最高频率)

worst case 对应ssg、high temperature、low voltage (可以跑的最低频率)

一般在二者之间

HVT LVT SVT是指工艺库中可提供的cell类型,HVT表示高阈值电压,功耗低(因为low leakage)、速度慢,LVT表示低阈值电压,功耗高但速度快,SVT(也有叫RVT)居中。一般在后端优化过程中,会根据timing情况,自动使用上述的几种cell类型,timing紧的地方就选用LVT,timing比较松的地方就是用HVT,即在满足timing的前提下,尽量使用HVT cell,降低功耗

Global 与Local

这里的SSG和FFG多出来的G,即Global variation。在非先进工艺下,local variation的影响较小,和global variation在k-lib时同时被考虑。随着工艺进步,local variation越来越重要,使用OCV对其进行补偿,对应的corner即为Global Variation。

global variation 全局工艺偏差,指的是同一器件在不同芯片间的偏差,相对的local variation局部工艺偏差,指的是同一器件在同一芯片不同区域的偏差。

voltage corner:

晶体管的速度随着电压的升高而提高。因此,sign off时需要考虑极限电压的情况,通常是在标称电压(norminal voltage)±10%的范围内,以保证芯片在整个电压范围能够正常工作。

temprature corner:

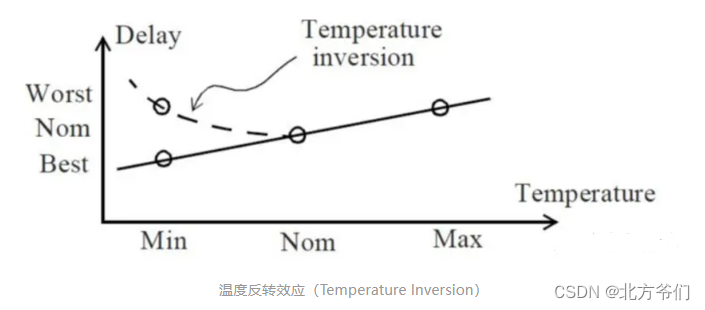

温度会影响晶体管的速度。时序签收时,需要能够保证芯片在设计的整个温度范围能够正常工作。由于结温与环境温度的差异,需保留足够的设计余量。在传统工艺下,一般来说随着温度的降低,delay也随之降低。

但是随着先进工艺的进步,随着温度降低反而会导致延迟增加,这个现象被称为温度反转效应,最差的delay可能出现在最高温,也可能发生在最低温。

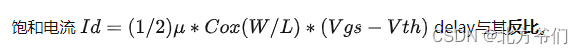

随着温度的降低,阈值电压Vth增高,晶体管的迁移率μ提高。阈值电压增加导致延迟增加,迁移率增加导致延迟减小。这应该是相互矛盾的一对影响,实际上在长沟道和短沟道不同工艺中,两者有一产生了主导的作用。

长沟道工艺的供电电压较高,即Vgs-Vth的过驱动电压较大,由于低温使Vth增大,但是Vgs-Vth总的减小的幅度不大,且迁移率μ提高,此时μ占主导因素,延迟减小。

短沟道工艺中,供电电压更低,温度降低导致的Vgs-Vth变化的幅度较大,导致饱和电流Id降低,延迟增加。

RC corner:

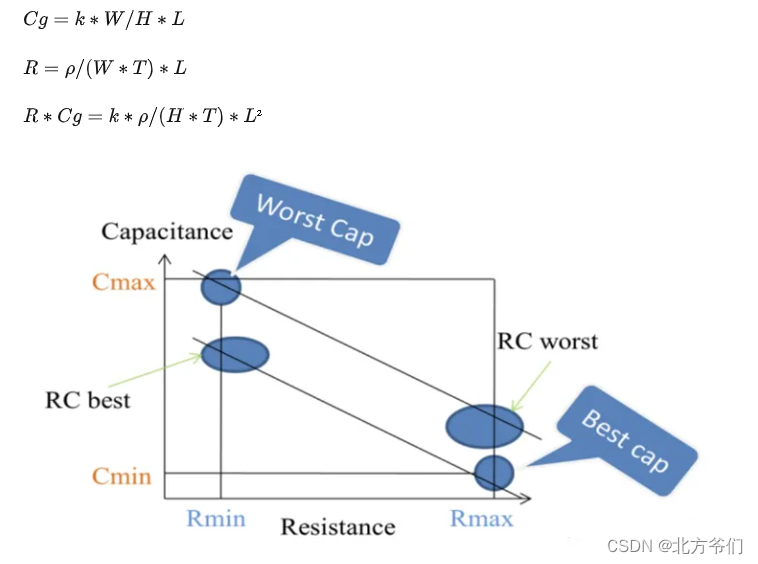

互连电阻(R)来自设计实现中各种金属层和过孔(vias)中的互连走线。可以将互连电阻视为单元的输出引脚与扇出单元的输入引脚之间的电阻。主要与线宽、线厚和温度相关。

互连电容(C)也来自金属走线,包括接地电容以及相邻信号路径之间的电容。同层相邻两条绕线之间的耦合电容coupling capacitance、不同层上下相邻的表面电容surface capacitance、边缘电容fringe capacitance。随着工艺的进步,表面电容减小,耦合电容增加。

互连电感(L)是由于电流环路而产生的,通常,电感效应在芯片内可以忽略不计,仅在封装和板级分析中考虑。

为了抽取更准确的寄生参数,在不同Corner下的RC计算直接影响STA(Static Timing Analysis)的结果。

一般在90nm之前的工艺节点,cell delay占主导,net delay可以忽略,耦合电容的影响可以忽略。

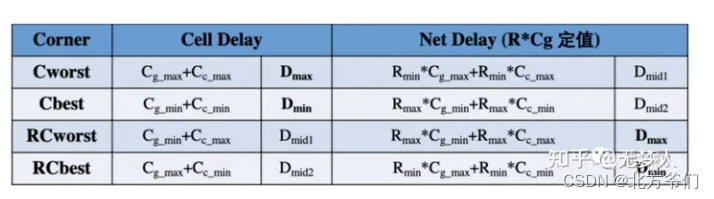

Cbest:电容最小,电阻最大,对于short nets有最小的delay,主要用于min-path-analysis即hold的分析,简称Cmin。

Cworst:电容最大,电阻最小,对于short nets有最大的delay,主要用于max-path-analysis即setup的分析,简称Cmax。

90nm之后的更先进工艺中,net delay的比重增加,耦合电容占比增大,增加两个corner。

RCbest:RC的乘积最小,对于具有长互联的路径,具有最小的延迟,用于hold分析。

RCworst:RC的乘积最大,对于具有长互联的路径,具有最大的延迟,用于setup分析。

在STA的分析过程中,总的delay是cell delay与net delay的和。cell的delay与transition、扇出有关,net的delay便是RC的影响。

Setup RC Corner:Cworst RCwosrst

需要数据最慢到达,即最大的延迟,此时Cworst和Cbest可以cover掉RCbest与RCworst的情况。

hold RC Corner:Cbest RCbest Cworst RCworst

需要数据最快到达,即最小的延迟,根据上面的表,需要在四个corner下都进行检查。

PVT三者相互组合就形成了如下的Senario。

WC:worst case slow,低电压,高温度,慢工艺 -> 一般情况下delay最大,setup 差。

WCL:worst case low-temperature,低电压,低温度,慢工艺 -> 温度反转效应时delay最大,setup差。

LT:即low-temperature,也叫bc(best case fast),高电压,低温度,快工艺 -> 一般情况下delay最小,hold差。

ML:max-leakage,高电压,高温度,快工艺 -> 温度反转效应下delay最小,hold差。

TC:typical,也叫tt,普通电压,普通温度,标准工艺 -> 各种typical。

BC:Best case。高电压,快工艺,常温0℃ or 25℃。

文章详细介绍了数字集成电路后端设计中的关键因素,包括PVT(工艺、电压、温度)对芯片性能的影响,晶体管的工艺偏差建模(如TT、SS、FF等corner),电压和温度如何改变晶体管速度,以及互连线的RCcorner在时序分析中的重要性。此外,文章还提到了不同工艺节点下,netdelay和耦合电容的影响变化,以及在STA中的应用,如setup和hold分析的corner选择。

文章详细介绍了数字集成电路后端设计中的关键因素,包括PVT(工艺、电压、温度)对芯片性能的影响,晶体管的工艺偏差建模(如TT、SS、FF等corner),电压和温度如何改变晶体管速度,以及互连线的RCcorner在时序分析中的重要性。此外,文章还提到了不同工艺节点下,netdelay和耦合电容的影响变化,以及在STA中的应用,如setup和hold分析的corner选择。

827

827

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?