本篇文章主要评估在应用DDR3接口时,SOC侧设计选择封装不同的层数对信号SI的影响,最终使得信号质量和成本的一个trade-off。

4L/6L封装基板层叠定义

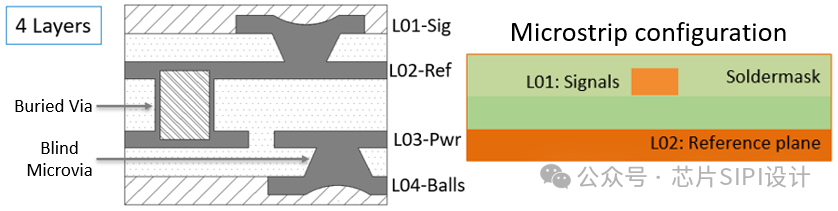

对于4层基板来说,主要金属层风别为,第一层为信号出线层,第二层为参考地平面,第三层为主电源平面,第四层为大地和ball pad层;如下图展示为一个4层封装基板的横截面结构和微带线定义。

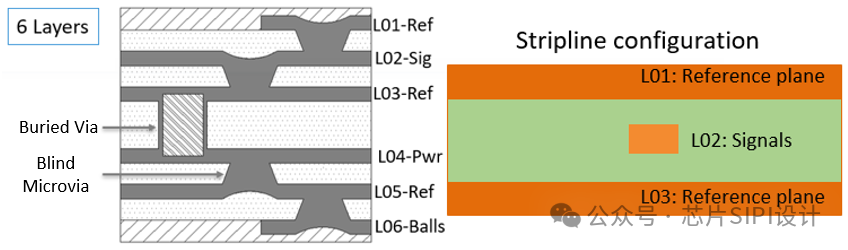

对于6层封装基板,可以用第2层来做主要的信号出线层,第1层3层为地参考平面,这是带状线走线的结构,有利于避免EMI的风险,第4层为电源平面,第5层为地平面,第6层为地平面和ball pad层;如下图是6层封装基板横截面图和带状线结构。

封装bump/ball fanout SIPI指导设计的基本原则

封装基板的bump/ball fanout的方式主要影响到信号出线的方式,当需要调整某根信号的走线时,往往需要DIE、封装、PCB进行联调,这样来保证信号没有交叉,信号之间没有相互干扰,或不连续出现;bump到ball fanout的基本原则如下:

1591

1591

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?