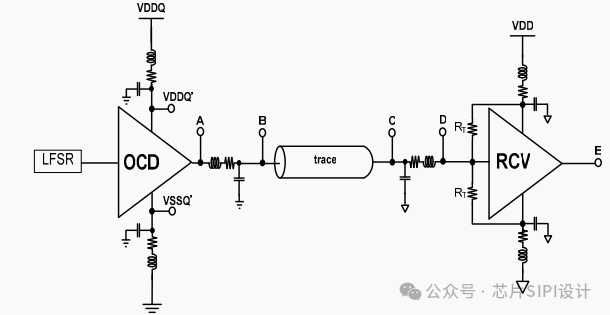

上一篇介绍了不同SOC封装叠层对DDR3接口无源性能的影响(DDR3不同SOC封装基板叠层SIPI设计对比及优化),基于此本篇文章将从量化的指导设计的角度详细地介绍芯片封装板 (CPB)寄生模型应用于不同的工艺和温度角,以研究PI/SI如何影响1.6 Gbps DDR3内存系统在电源电压为1.5 V时的输入/输出(I/O)性能,其中eye-opening(眼图开窗heye) 是主要性能指标。建立的DDR3 SIPI仿真拓扑图如下图所示。图中AB和CD之间的RLC是封装的等效模型,因为对于PCB应用端,可能拿不到芯片侧的模型,但是可以有一个RLC作为参考来评估板级应用和指导PCB设计,虽然有就偏差但是能大致评估SIPI的性能也是可取的,介于此本文也使用这种方式来做,希望给大家提供一种思路。

LFSR代表memory芯片输出并且连接到Driver电路上,LFSR产生一个2^10-1bits的PRBS码,片上的电源、地和输出信号通过封装模型连接到PCB,由于一般PCB级可能拿不到,所以如上图使用RLC代表,默认仿真值分别为300mOhm、2nH、0.27pF。图中的trace是一个FR4为介质材料的微带线结构走线,传输线默认长度为50mm,阻抗为40Ohm。信号则通过trace进入接收端,同样封装使用RLC原件代替。Rt为ODT电阻,放在接收端的前方。

根据JEDEC标准要求,DDR3关键性能指标spe

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

34

34

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?