基于大数据的机器学习技术的快速发展,需要更强大的硬件资源和高效的软件算法以寻求最优解。特别是硬件系统需支持更高频率操作以实现低延迟内部处理,这对带宽提出了更高要求。高带宽内存(HBM)因其卓越性能成为HPC应用的理想选择,其规格已从HBM2演进至HBM2e及HBM3,速率高达6.2Gbps/针脚。此外,各类神经处理单元(NPU)通过复杂算法实现高动态电流波动下的极高性能,进一步加剧了电源噪声问题。由于芯片面积限制,传统的片上MOS电容器难以应对高密度电路同时切换导致的电源噪声。为此,金属-绝缘体-金属(MIM)电容器成为先进制程(14nm及以下)中稳定晶体管性能的关键解决方案。因此,针对HPC应用的电源完整性设计方法亟待优化。若缺乏PI设计方法的早期规划,将严重影响整体设计性能,故在初期设计阶段应用系统级PI解决方案至关重要。

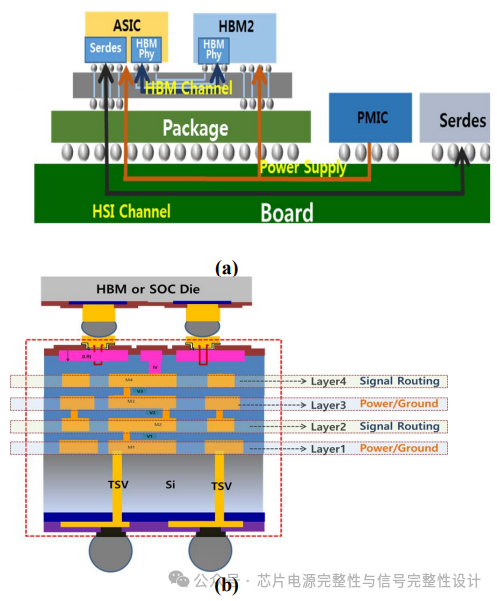

图1.(a)2.5D Si interposer封装结构示意图;(b)Si interposer的堆叠布局

高功耗应用的PI解决方案

接下来将针对HPC/AI等高功耗产品的PI分析与设计优化,涵盖电源预算评估流程以确保系统级PI性能满足片上/片外电压跌落标准。通过关键设计参数(如片上电容、封装/板级电容)的扫描分析,结合多种电容器组合确定目标电压噪声。其中,布局前PI预估对早期电源输送网络(PDN)设计目标的设定尤为重要。基于去耦电容器的可行方案,需对系统级PI性能进行优化设计。

A.系统配置

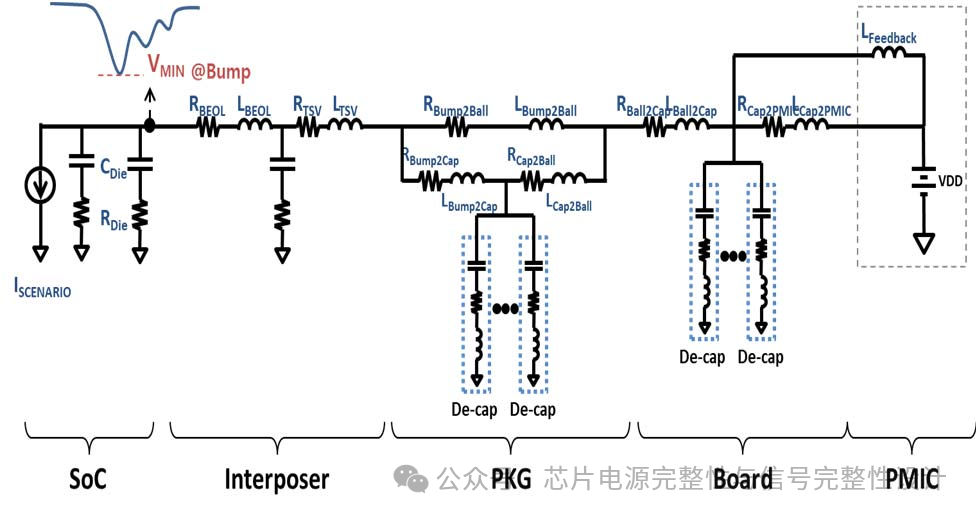

HPC平台采用多芯片配置(主处理芯片与外部存储芯片)集成于Si interposer基板。从设计角度看,SoC与HBM芯片间的高密度互连(超千数量级)需支持宽带宽(HBM2>1TB/s,多芯片组装功耗≥10W/芯片)。如图1所示,HBM芯片需尽可能靠近SoC以最小化通道损耗,芯片边缘间距需控制在100μm以内(受组装技术限制)。系统PI性能的挑战包括:(1)高功耗核心IP的PI性能需保证大电流供应与电源快速响应以维持焊点电压稳定。有限的焊点/焊球数量会因高功率密度导致PI性能下降,需提供有效的PI解决方案;(2)超大带宽下的信号完整性(SI)性能同样关键。为评估焊点电压跌落,需建立包含片上/封装/板级等效电路模型的PDN(如图2),并通过HSPICE仿真结合电流特性、PDN配置及电源管理IC(PMIC)性能分析电压表现。

图2.系统级PI估计的等效PDN电路模型示意图

B.基于高密度电容器的PI解决方案

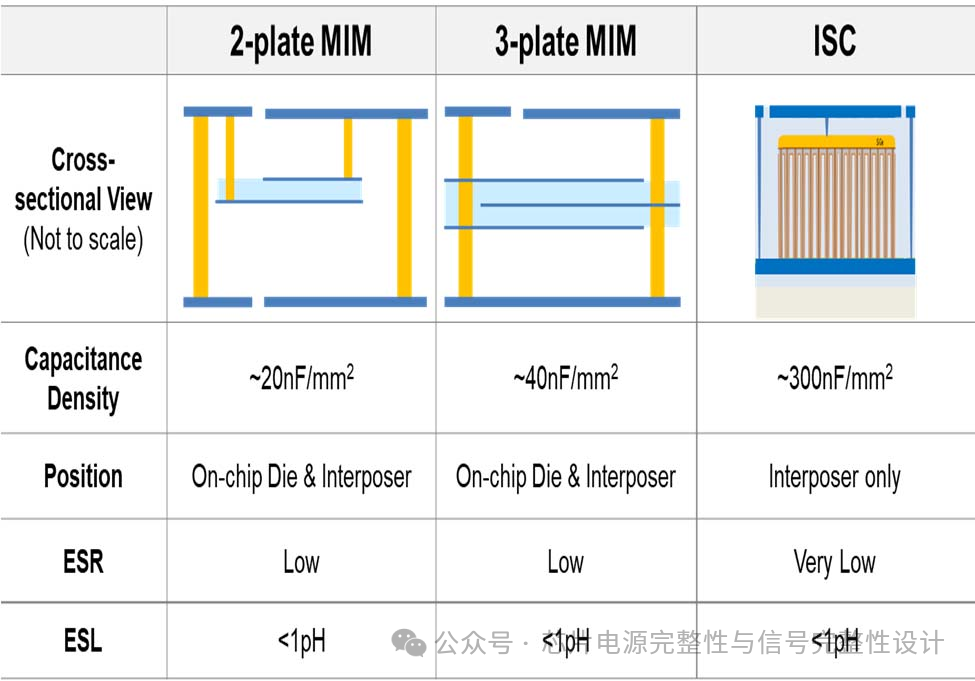

针对电源完整性,提出了多种基于高密度片上电容器的PI解决方案,包括2/3层MIM电容器与集成堆叠电容器(ISC)。MIM电容器部署于SoC或Si interposer顶部金属层。图3展示了基于高密度电容器的片上PI解决方案:多层薄金属通过高介电材料交替堆叠,金属层数决定电容密度。2/3层MIM电容密度分别约为20nF/mm²与40nF/mm²;ISC则采用圆柱形双层薄金属结构嵌入interposer金属层间,电容密度高达300nF/mm²。MIM电容器根据工艺设计规则以单元形式布局于芯片或interposer。

图3.基于高密度电容器的PI解决方案

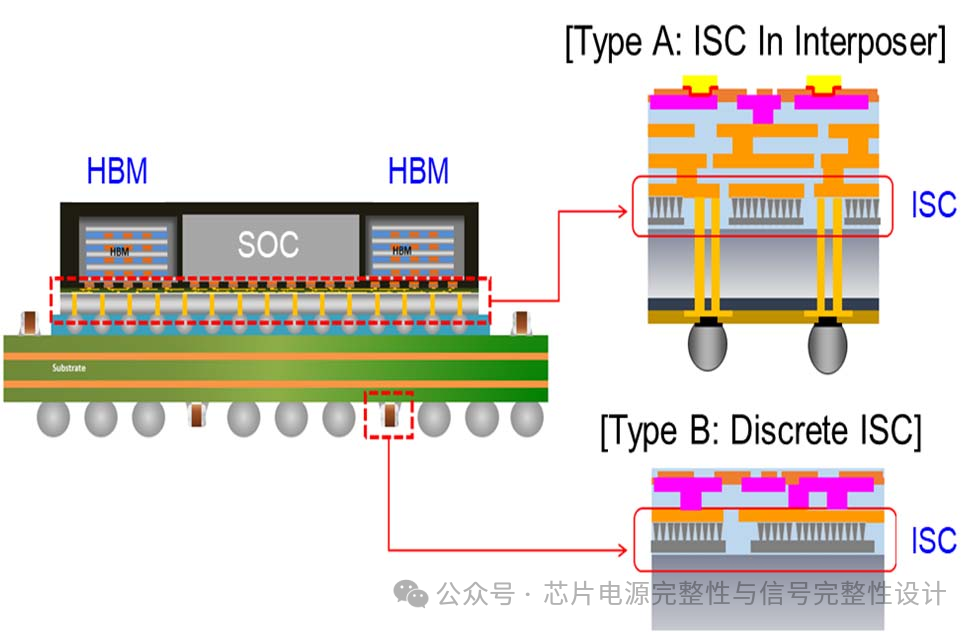

首先通过3D建模精确提取单元MIM的ESR/ESL及电容值,确定最佳制造结构。建模完成后,利用寄生参数提取工具生成interposer/系统的精确MIM电容。ISC是另一系统级PI保障方案,其电容层嵌入interposer金属层间,面积与interposer结构匹配,可实现超大电容。

图4.基于ISC的2.5D封装方案示意图

C.系统级PI仿真

为准确分析PI性能,需建立包含片上电容与封装/板级电感的等效电路模型(图2),通过去耦电容器数量与组合优化PDN阻抗。关键参数(片上电容、封装去耦电容器数量与布局、封装焊球数量、板级PDN特性)从物理布局中提取:片上电容基于IP区域,板级电感通过路径长度、过孔直径与间距估算,封装去耦电容器参数(ESR、ESL、电容值)则来自厂商器件库。基于此,通过假设分析(what-if)在初期设计阶段优化系统级PDN。电压跌落以矩阵形式通过多参数扫描计算,最终优选去耦电容器布局方案。

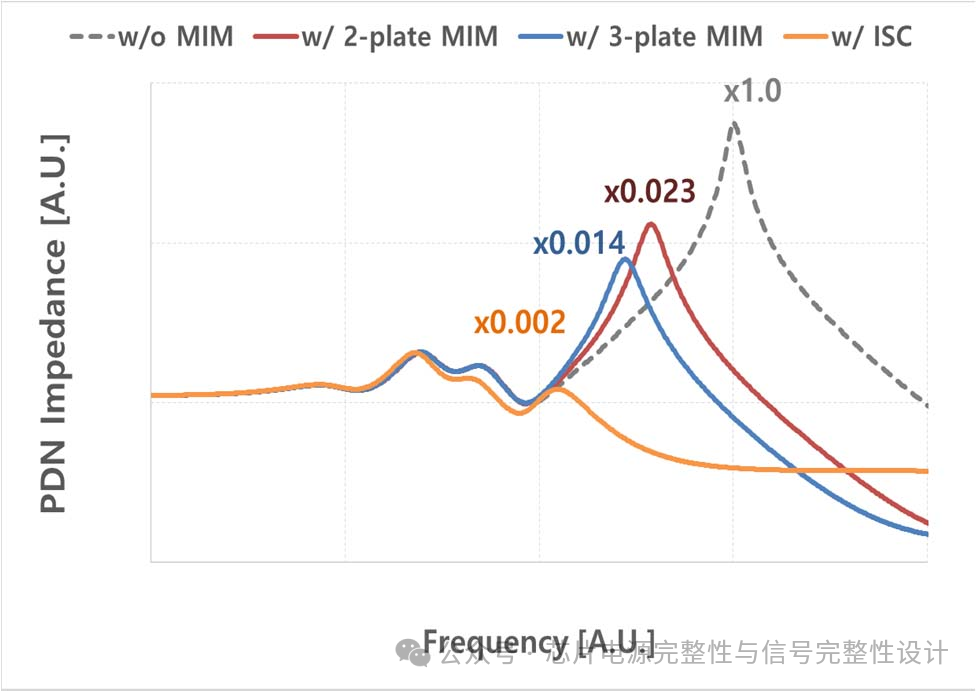

图5.不同片上PI解决方案下的PDN阻抗特性(SoC功耗密度0.5W/mm²)

将高密度电容器PI方案应用于百瓦级HPC/AI应用(对应硅片功耗密度0.5W/mm²)。在SoC与interposer允许面积内,2/3层MIM总电容分别为10μF与20μF,而ISC仅在interposer集成150μF电容。图5展示了不同PI方案下的PDN阻抗特性:相较于无额外电容的参考 Case (x1.0),MIM与ISC方案在10MHz至100MHz频段内可将PDN阻抗降低至x0.002(ISC Case )。因此,需通过系统级PDN仿真提取所需电容密度,结合成本效益选择最优PI方案。

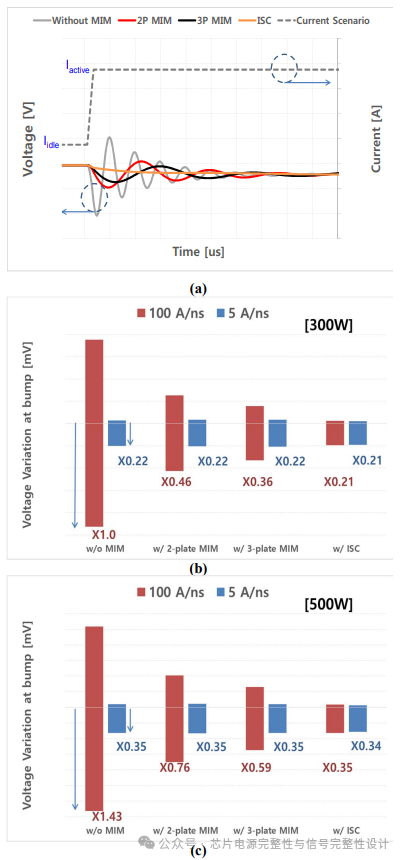

图6.不同片上去耦电容器类型对PI的影响:(a)斜率切换下的电流特性;(b)300W级PI解决方案的电压特性;(c)500W级电压特性

图6显示,在300W测试 Case (电流瞬变100A/ns)中,相较于无MIM参考 Case ,2层MIM、3层MIM及ISC的电压跌落分别改善至x0.46、x0.36与x0.21。在500W Case 中,无MIM时电压跌落增加至x1.43,而2/3层MIM与ISC分别降至x0.76/x0.59与x0.35。值得注意的是,当电流瞬变从100A/ns降至5A/ns时,片上电容器类型对焊点电压跌落的影响趋于独立(300W Case x0.21,500W Case x0.34)。这表明,在片上电容器面积受限时,通过RTL架构调整电流场景可有效优化系统级PI性能。

结论

为维持焊点电压稳定,需结合片外封装/板级去耦电容器优化PDN阻抗以满足总电容需求。作为片上解决方案,2/3层MIM(20/40nF/mm²)与ISC(300nF/mm²)展现出显著优势。此外,针对HPC/AI应用的RTL架构调整(如减缓电流斜率与峰值)可避免最终PI性能失效。随着高功耗应用需求的增长,早期PI分析与设计的重要性日益凸显。上述评估方法可以有望应用于高功耗设计场景,避免性能退化。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?