NandFlash详述

文章目录

1. Nand Flash 是什么

一种非易失性存储设备(Non-volatile Memory Device),就是断电了也不会丢失数据的设备。常见设备:U盘、MP3等。由东芝公司雇员富士雄于1986年发明。

1.1 闪存存储单元

Nand Flash按照内部存储数据单元的电压的不同层次,也就是单个内存单元中,是存储1位数据,还是多位数据,可以分为SLC、MLC和TLC。

-

SLC(single-level cell):单阶存储单元,高端SSD

-

MLC(Multi-level cell):二阶存储单元,高端SSD

-

TLC(Triple-Level Cell):三阶存储单元 ,SD卡、低端SSD

规律:单个存储单元存储的比特位越多,读写性能会越差,寿命也越短,但是成本会更低。

2. Nand Flash 内部原理

2.1 硬件实现机制

数据的表示,以所存储的电荷的电压是否超过一个特定的阈值Vth来表示,因此,Flash的存储单元的默认值,不是0,而是1。充电表示擦除,放电表示写入。

2.2 数据存储单元的整体架构

1 Nand Flash = n Chip

1 Chip = n Plane

1 Plane = n Block

1 Block = 64 Page 擦除的基本单位

1 Page = (2k + 64)B 读/写的基本单位

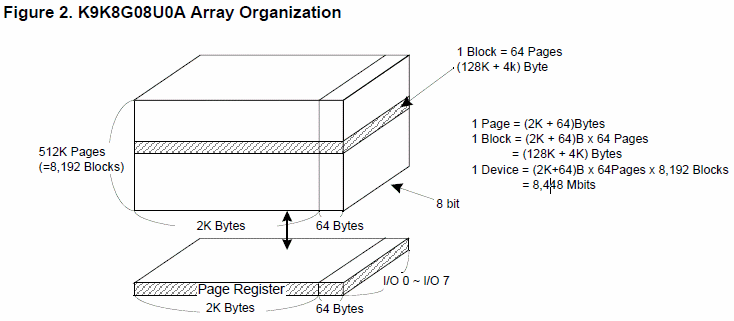

拿型号为K9K8G08U0A这块芯片举例:

1 Nand Flash = 2 × K9F4G08U0A(K9F4G08U0A是chip,1 K9F4G08U0A = 2 Plane)

= 2 × 2个Plane

= 4 Plane(1 Plane = 2048 Block)

= 4 × 2048个Block(1 Block = 64 Page)

= 4 × 2048 × 64Page(1 Page = 2KB)

= 4 × 2048 × 64Page × 2KB

= 1GB

1 Page = 2KB

1 Block = 64 Page =128KB

1 Plane =2048 Block = 256MB

1 K9F4G08U0A = 2 Plane = 512MB

1 Nand Flash = 2 K9F4G08U0A = 1GB

总结:读/写是一页一页读/写的,擦除是一块一块擦除的。

2.3 物理存储单元的阵列组织结构

-

块 (Block)

- 擦除的基本单位

-

页(Page)

- 读写操作的基本单位。

-

oob (Out Of Band)

每一个页,对应还有一块区域,叫做空闲区域(spare area)/冗余区域(redundant area),而Linux系统中,一般叫做OOB(Out Of Band),这个区域,是最初基于Nand Flash的硬件特性:数据在读写时候相对容易错误,所以为了保证数据的正确性,必须要有对应的检测和纠错机制,此机制被叫做ECC(Error Code Correction 或者 Error Checking and Correcting),所以设计了多余的区域,用于放置数据的校验值。

Oob的读写操作,一般是随着页的操作一起完成的,即读写页的时候,对应地就读写了oob。

关于oob具体用途,总结起来有:

- 标记是否是坏块

- 存储ECC数据

- 存储一些和文件系统相关的数据。如jffs2就会用到这些空间存储一些特定信息,而yaffs2文件系统,会在oob中,存放很多和自己文件系统相关的信息。

2.4 引脚(Pin)的说明

| 引脚名称 | 引脚功能 |

|---|---|

| I/O0 ~ I/O7 | 用于输入地址/数据/命令,输出数据 |

| CLE | Command Latch Enable,命令锁存使能,在输入命令之前,要先在模式寄存器中,设置CLE使能 |

| ALE | Address Latch Enable,地址锁存使能,在输入地址之前,要先在模式寄存器中,设置ALE使能 |

| CE# | Chip Enable,芯片使能,在操作Nand Flash之前,要先选中此芯片,才能操作 |

| RE# | Read Enable,读使能,在读取数据之前,要先使CE#有效。 |

| WE# | Write Enable,写使能, 在写取数据之前,要先使WE#有效 |

| WP# | Write Protect,写保护 |

| R/B# | Ready/Busy Output,就绪/忙,主要用于在发送完编程/擦除命令后,检测这些操作是否完成,忙,表示编程/擦除操作仍在进行中,就绪表示操作完成 |

| Vcc | Power,电源 |

| Vss | Ground,接地 |

| N.C | Non-Connection,未定义,未连接 |

在数据手册中,你常会看到,对于一个引脚定义,有些字母上面带一横杠的,那是说明此引脚/信号是低电平有效,比如你上面看到的RE头上有个横线,就是说明,此RE是低电平有效,此外,为了书写方便,在字母后面加“#”,也是表示低电平有效,比如我上面写的CE#;如果字母头上啥都没有,就是默认的高电平有效,比如上面的CLE,就是高电平有效。

2.5 特殊硬件结构

页寄存器(Page Register):

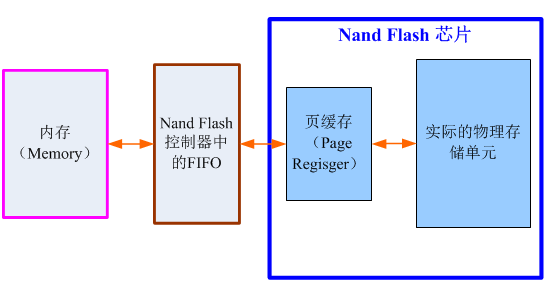

由于Nand Flash读取和编程操作来说,一般最小单位是页,所以Nand Flash在硬件设计时候,就考虑到这一特性,对于每一片(Plane),都有一个对应的区域专门用于存放,将要写入到物理存储单元中去的或者刚从存储单元中读取出来的,一页的数据,这个数据缓存区,本质上就是一个缓存buffer,但是只是此处datasheet里面把其叫做页寄存器page register而已,实际将其理解为页缓存,更贴切原意。

而正是因为有些人不了解此内部结构,才容易产生之前遇到的某人的误解,以为内存里面的数据,通过Nand Flash的FIFO,写入到Nand Flash里面去,就以为立刻实现了实际数据写入到物理存储单元中了,而实际上只是写到了这个页缓存中,只有当你再发送了对应的编程第二阶段的确认命令,即0x10,之后,实际的编程动作才开始,才开始把页缓存中的数据,一点点写到物理存储单元中去。

Nand Flash读写时的数据流向:

3. Nand Flash 怎么用

3.1 常见操作

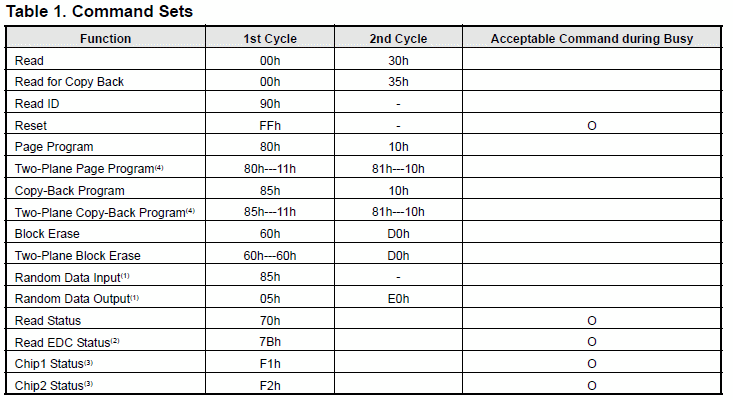

命令集合:

- 写一个页的数据(Page Program),就是先发送0x80h,然后发送要写入的地址,再发送0x10h。

- 读一个页的数据(Page Program),先发送0x00h,然后发送你所要读取的页的地址,再发送0x30h。

- 擦除(Block Erase),开始的命令0x60是擦除设置命令(erase setup comman),然后传入要擦除的块地址,然后再传入擦除确认命令(erase confirm command)0xD0。

这种完成单个操作要分两步发送命令的设计,即先开始设置,再最后确认的命令方式,是为了避免由于外部意外的/未预料因素而产生的噪音。比如,由于某种噪音,而产生了0x60命令,此时,即使被Nand Flash误认为是擦除操作,但是没有之后的确认操作0xD0,Nand Flash就不会去擦除数据,这样使得数据更安全,不会由于噪音而误操作。

3.2 读取操作的时序图

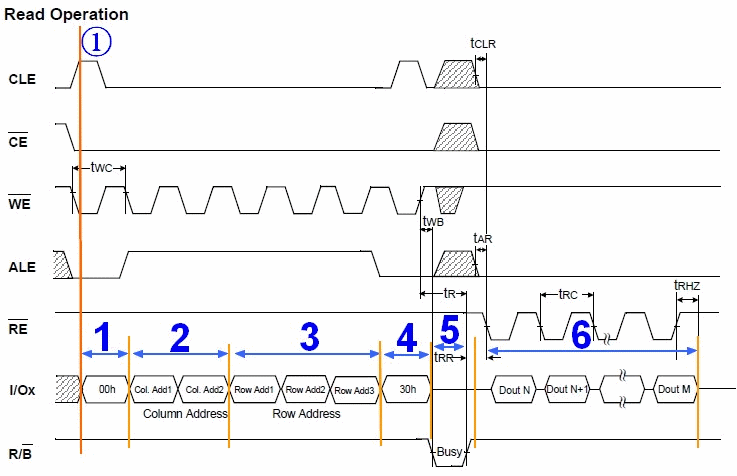

黄色竖线所处的时刻,是在发送读操作的第一个周期的命令0x00之前的那一刻。

让我们看看,在那一刻,其所穿过好几行都对应什么值,以及进一步理解,为何要那个值。

-

黄色竖线穿过的第一行,是CLE。CLE置1,就说明你将要通过I/O复用端口发送进入Nand Flash的,是命令,而不是地址或者其他类型的数据。只有这样将CLE置1,使其有效,才能去通知了内部硬件逻辑,你接下来将收到的是命令,内部硬件逻辑,才会将受到的命令,放到命令寄存器中,才能实现后面正确的操作,否则,不去将CLE置1使其有效,硬件会无所适从,不知道你传入的到底是数据还是命令了。

-

而第二行,是CE#,那一刻的值是0。这个道理很简单,你既然要向Nand Flash发命令,那么先要选中它,所以,要保证CE#为低电平,使其有效,也就是片选有效。

-

第三行是WE#,意思是写使能。因为接下来是往Nand Flash里面写命令,所以,要使得WE#有效,所以设为低电平。

-

第四行,是ALE是低电平,而ALE是高电平有效,此时意思就是使其无效。而对应地,前面介绍的,使CLE有效,因为将要数据的是命令(此时是发送图示所示的读命令第二周期的0x30),而不是地址。如果在其他某些场合,比如接下来的要输入地址的时候,就要使其有效,而使CLE无效了。

-

第五行,RE#,此时是高电平,无效。可以看到,知道后面低6阶段,才变成低电平,才有效,因为那时候,要发生读取命令,去读取数据。

-

第六行,就是我们重点要介绍的,复用的输入输出I/O端口了,此刻,还没有输入数据,接下来,在不同的阶段,会输入或输出不同的数据/地址。

-

第七行,R/B#,高电平,表示R(Ready)/就绪,因为到了后面的第5阶段,硬件内部,在第四阶段,接受了外界的读取命令后,把该页的数据一点点送到页寄存器中,这段时间,属于系统在忙着干活,属于忙的阶段,所以,R/B#才变成低,表示Busy忙的状态的。

对于上面的从1到6,每个阶段所表示的含义,再简单解释一下:

- 此阶段,是读命令第一个周期,发送的命令为0x00。

- 此阶段,依次发送列地址,关于这些行地址,列地址等是如何计算出来的,后面的内容会有详细解释。

- 此阶段是发送对应的行地址

- 此阶段是发送读命令第二周期2nd cycle所对应的命令,0x30

- 此阶段是等待时间,等待Nand Flash硬件上准备好对应的数据,以便后续读出。

- 此阶段,就是一点点地把所需要的数据读出来。

3.3 计算传入的行地址和列地址

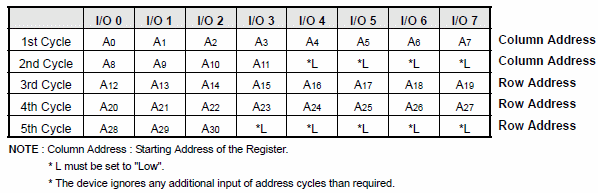

Nand Flash的地址周期组成:

*L,意思是地电平,由于未用到那些位,datasheet中强制要求设为0,所以,才有上面的2nd周期中的高4位是0000.其他的A30之后的位也是类似原理,都是0。

结合操作的时序图中的2,3阶段,我们可以看出,此Nand Flash地址周期共有5个,2个列(Column)周期,3个行(Row)周期。

-

对应地,列地址A0~A10,就是页内地址,地址范围是从0到2047。

细心的读者可能注意到了,为何此处多出来个A11呢?

这样从A0到A11,一共就是12位,可以表示的范围就是02^12,即04096了。

实际上,由于我们访问页内地址,可能会访问到oob的位置,即2048-2111这64个字节的范围内,所以,此处实际上只用到了2048~2111,用于表示页内的oob区域,其大小是64字节。

-

对应地,A12~A30,称作页号,页的号码,可以定位到具体是哪一个页。

A18~A30,表示对应的块号,即属于哪个块。

例子:还是拿K9K8G08U0A来说,它一共有8192个块,每个块内有64页,每个页是2K+64 Bytes。假设,我们要访问其中的第7000个块中的第64页中的1208字节处的地址,此时,我们就要先把具体的地址算出来:

物理地址 = 块大小×块号 + 页大小×页号 + 页内地址

=128K×7000 + 2K×64 + 1208

=0x36B204B8 = 11 0110 1011 0010 0000 ***0***100 1011 1000

分别分配到5个地址周期就是:

| 周期 | 位置 | 地址 |

|---|---|---|

| 1st周期 | A7 ~ A0 | 1011 1000 = 0xB8 |

| 2nd周期 | A11~ A8 | 0100 = 0x04 |

| 3rd周期 | A19~A12 | 0010 0000 = 0x20 |

| 4th周期 | A27~A20 | 0110 1011 = 0x6B |

| 5th周期 | A29~A28 | 11 = 0x03 |

上述计算方法为何是错误的呢?那是因为上面计算过程中,把第11位的值,本来是属于页号的位A11,给算成页内地址里面的值了。

应该是这样计算,才是对的:

0x36B204B8 = 11 0110 1011 0010 0000 ***0***100 1011 1000

| 周期 | 位置 | 地址 |

|---|---|---|

| 1st周期 | A7 ~ A0 | 1011 1000 = 0xB8 |

| 2nd周期 | A10~ A8 | 100 = 0x04 |

| 3rd周期 | A18~A11 | 010 0000 0 = 0x40 |

| 4th周期 | A26~A19 | 110 1011 0 = 0xD6 |

| 5th周期 | A29~A27 | 11 0 = 0x06 |

那有人会问了,上面表中,不是明明写的A0到A30,其中包括A11,不是正好对应着此处地址中的bit0到bit30吗?

其实,我开始也是犯了同样的错误,误以为我们要传入的地址的每一位,就是对应着表11中的A0到A30呢,实际上,表11中的A11,是比较特殊的,只有当我们访问页内地址处于oob的位置,即属于20482111的时候,A11才会其效果,才会用A0-A11用来表示对应的某个属于20482111的某个值,属于oob的某个位置。

而我们此处的页内地址为1208,还没有超过2047呢,所以A11肯定是0。

11 0110 1011 0010 0000 0 = 448064

2^18 = 262144

2^19 =524288

说白了,我们就是要访问第7000个块中的第64页中的1208字节处,对应着

页内地址

=1208

=0x4B8

页号 = 块数×页数/块 + 块内的页号

= 7000×(128K/2K) + 64

= 7000×64 + 64

= 448064

=0x6D640

也就是,我们要访问0x6D640页内的0x4B8地址

然后对应的:

页内地址=0x4B8

分成两个对应的列地址,就变成

0x4B8 :列地址1=0xB8,列地址2=0x04

页号=0x6D640,分成三个行号就是:

0x6D640:行号1=0x40,行号2=0xD6,行号3=0x06。

4. Nand Flash 的优缺点

4.1 NOR Flash与NAND Flash的比较

左边是NAND,右边是NOR

| 属性 | NOR | NAND |

|---|---|---|

| 容量 | 较小 | 很大 |

| XIP(可执行Code) | 可以 | 不行 |

| 读取速度 | 很快 | 快 |

| 写入速度 | 慢 | 快 |

| 擦除速度 | 很慢(5s) | 快(4ms) |

| 可擦除次数 | 10K-100K | 10K-100K |

| 可靠性 | 高 | 较低 |

| 访问方式 | 可随机访问 | 块方式 |

| 价格 | 高 | 低 |

NAND Flash的单元尺寸几乎是NOR器件的一半,生产过程更为简单,NAND结构可 以在给定的模具尺寸内提供更高的容量,也就 相应地降低了价格。

NOR flash占据了容量为1~16MB闪存市场的大部分,而NAND flash只是用在8~128MB的产品当中,这也说明NOR主要应用在代码存储介质中,NAND适合于数据存储,NAND在CompactFlash、Secure Digital、PC Cards和MMC存储卡市场上所占份额最大。

5. 相关技术和知识

5.1 片选无关(CE don’t-care)技术

很多Nand flash支持一个叫做CE don’t-care的技术,字面意思就是,不关心是否片选。

对此也许有人会问了,如果不片选,那还能对其操作吗?答案就是,这个技术,主要用在当时是不需要选中芯片,但是芯片内部却仍可以继续操作的这些情况:在某些应用,比如录音,音频播放等应用中,外部使用的微秒(us)级的时钟周期,此处假设是比较少的2us,在进行读取一页或者对页编程时,是对Nand Flash操作,这样的串行(Serial Access)访问的周期都是20/30/50ns,都是纳秒(ns)级的,此处假设是50ns,当你已经发了对应的读或写的命令之后,接下来只是需要Nand Flash内部去自己操作,将数据读取除了或写入进去到内部的数据寄存器中而已,此处,如果可以把片选取消,CE#是低电平有效,取消片选就是拉高电平,这样会在下一个外部命令发送过来之前,即微秒量级的时间里面,即2us-50ns≈2us,这段时间的取消片选,可以降低很少的系统功耗,但是多次的操作,就可以在很大程度上降低整体的功耗了。

总的来说就是:由于某些外部应用所需要的访问Nand Flash的频率比较低,而Nand Flash内部操作速度比较快,所以在针对Nand Flash的读或写操作的大部分时间里面,都是在等待外部命令的输入,同时却选中芯片,产生了多余的功耗,此“不关心片选”技术,就是在Nand Flash的内部的相对快速的操作(读或写)完成之后,就取消片选,以节省系统功耗。待下次外部命令/数据/地址输入来的时候,再选中芯片,即可正常继续操作了。这样,整体上,就可以大大降低系统功耗了。

如果想要操作硬件Nand Flash芯片,先要将对应的CE#(低有效)片选信号拉低,选中该芯片,然后才能做接下来的读写操作所要做的发命令,发数据等动作。Nand Flash的片选与否,功耗差别会有很大。如果数据没有记错的话,我之前遇到我们系统里面的Nand Flash的片选,大概有5个mA的电流输出呢,也许你对5mA没太多概念,给你说个数据你就知道了:当时为了针对MP3播放功耗进行优化,整个系统优化之后的待机功耗,也才10个mA左右的,所以节省5mA已经算是很不错的功耗优化了。

5.2 Wear-Leveling 负载平衡

Nand Flash的block的管理,还包括负载平衡。

正是由于Nand Flash的block,都是有一定寿命限制的,所以如果你每次都往同一个block擦除然后写入数据,那么那个block就很容易被用坏了,所以我们要去管理一下,将这么多次的对同一个block的操作,平均分布到其他一些block上面,使得在block的使用上,相对较平均,这样相对来说,可以更能充分利用Nand Flash。

关于wear-leveling这个词,再简单解释一下,wear就是穿(衣服)等,用(东西)导致磨损,而leveling就是使得均衡,所以放在一起就是,使得对于Nand Flash的那么多的block的使用磨损,相对均衡一些,以此延长Nand Flash的使用寿命或者说更加充分利用Nand Flash。

5.3 ECC错误校验码

Nand Flash物理特性上使得其数据读写过程中会发生一定几率的错误,所以要有个对应的错误检测和纠正的机制,于是才有此ECC,用于数据错误的检测与纠正。Nand Flash的ECC,常见的算法有海明码和BCH,这类算法的实现,可以是软件也可以是硬件。不同系统,根据自己的需求,采用对应的软件或者是硬件。

相对来说,硬件实现这类ECC算法,肯定要比软件速度要快,但是多加了对应的硬件部分,所以成本相对要高些。如果系统对于性能要求不是很高,那么可以采用软件实现这类ECC算法,但是由于增加了数据读取和写入前后要做的数据错误检测和纠错,所以性能相对要降低一些,即Nand Flash的读取和写入速度相对会有所影响。

其中,Linux中的软件实现ECC算法,即NAND_ECC_SOFT模式,就是用的对应的海明码。

而对于目前常见的MLC的Nand Flash来说,由于容量比较大,动辄2GB,4GB,8GB等,常用BCH算法。BCH算法,相对来说,算法比较复杂。

笔者由于水平有限,目前仍未完全搞懂BCH算法的原理。

BCH算法,通常是由对应的Nand Flash的Controller中,包含对应的硬件BCH ECC模块,实现了BCH算法,而作为软件方面,需要在读取数据后,写入数据之前,分别操作对应BCH相关的寄存器,设置成BCH模式,然后读取对应的BCH状态寄存器,得知是否有错误,和生成的BCH校验码,用于写入。

5.4 Copy-Back(Copy-Back Operation with EDC & Sector Definition for EDC)

Copy-Back功能,简单的说就是,将一个页的数据,拷贝到另一个页。

如果没有Copy-Back功能,那么正常的做法就是,先要将那个页的数据拷贝出来放到内存的数据buffer中,读出来之后,再用写命令将这页的数据,写到新的页里面。

而Copy-Back功能的好处在于,不需要用到外部的存储空间,不需要读出来放到外部的buffer里面,而是可以直接读取数据到内部的页寄存器(page register)然后写到新的页里面去。

而且,为了保证数据的正确,要硬件支持EDC(Error Detection Code)的,否则,在数据的拷贝过程中,可能会出现错误,并且拷贝次数多了,可能会累积更多错误。

而对于错误检测来说,硬件一般支持的是512字节数据,对应有16字节用来存放校验产生的ECC数值,而这512字节一般叫做一个扇区。对于2K+64字节大小的页来说,按照512字节分,分别叫做A,B,C,D区,而后面的64字节的oob区域,按照16字节一个区,分别叫做E,F,G,H区,对应存放A,B,C,D数据区的ECC的值。

Copy-Back编程的主要作用在于,去掉了数据串行读取出来,再串行写入进去的时间,所以,而这部分操作,是比较耗时的,所以此技术可以提高编程效率,提高系统整体性能。

5.5 交错页编程(Interleave Page Program)

多片同时编程,是针对一个chip里面的多个Plane来说的,

而此处的交错页编程,是指对多个chip而言的。

可以先对一个chip,假设叫chip1,里面的一页进行编程,然后此时,chip1内部就开始将数据一点点写到页里面,就出于忙的状态了,而此时可以利用这个时间,对出于就绪状态的chip2,也进行页编程,发送对应的命令后,chip2内部也就开始慢慢的写数据到存储单元里面去了,也出于忙的状态了。此时,再去检查chip1,如果编程完成了,就可以开始下一页的编程了,然后发完命令后,就让其内部慢慢的编程吧,再去检查chip2,如果也是编程完了,也就可以进行接下来的其他页的编程了。如此,交互操作chip1和chip2,就可以有效地利用时间,使得整体编程效率提高近2倍,大大提高Nand Flash的编程/擦写速度了。

6015

6015

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?