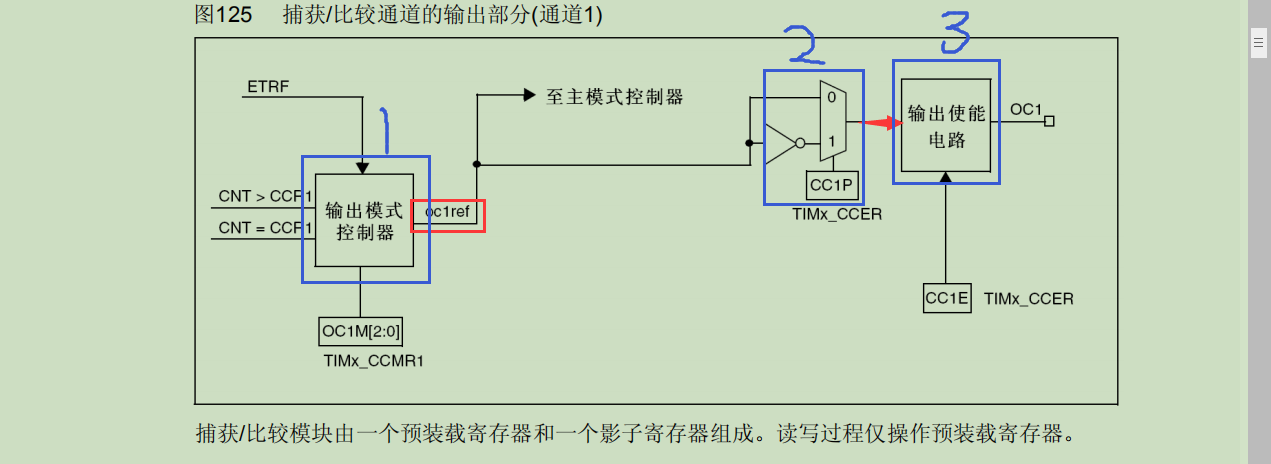

在学习STM32中的过程中,经常会遇到“高电平有效”,“低电平有效”等字眼,初看时很多时候就会从字面上理解,认为高电平有效的意思就是有效电平是高电平,低电平有效的意思就是有效电平是低电平的意思。而实际上,这样的理解是有误的。下面咱们以STM32的定时器中输出比较通道为例:

这幅图实际上就是一个pwm波产生的过程,对定时器不了解的可以去查阅相关手册,现在我们先看图中标号1的输出模式控制器,这里模式是指pwm模式,他的意思就是可以通过配置寄存器TIMx_CCMR1的OC1M两位,来选择pwm的模式,但是关于模式选择,手册中有这样一句话:在向下计数时,一旦TIMx_CNT>TIMx_CCR1时通道1为无效电平(OC1REF=0),否则为有效电平(OC1REF=1)。

红色字体告诉我们:OCREF为无效电平时为低电平,OCREF为有效电平时就是高电平。

再看标号2: 它的作用是选择输出极性。如果TIMx_CCER的CC1P位为0则高电平有效,否则低电平有效。这个高电平有效是什么意思呢?就是对于选择器来说,高电平有效,如果OCREF为高电平,那么这个选择器的门就会打开,让该信号进入 ,并“激活”该选择器, 之后选择器才会产生信号来激活后面的输出使能电路驱动OC1,让其在OC1上产生有效电平(也就是OC1上产生高电平)。

通过上面的分析机会发现,高电平有效意思是说,若信号为高电平,那么对相应的控制器来说才有效,才能激活该控制器的相关功能。

总结几个关键词:有效电平:高电平

无效电平:低电平

高电平有效:高电平可以使能相应功能

低电平有效:低电平可以使能相应功能

3045

3045

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?