-

手册

- 本文只介绍RMII模式及相关引脚

|

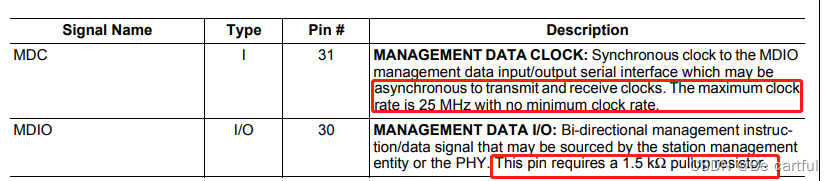

管理数据IOMDIO:需要1.5K的上拉(也是接入单片机) | |||

|

| |||

|

| |||

|

| |||

|

| |||

|

| |||

|

| |||

|

| |||

|

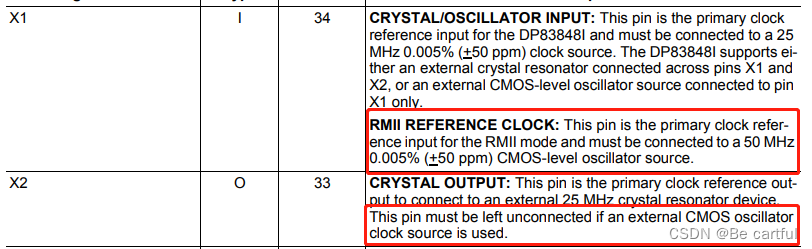

X2:如果使用外部CMOS振荡器时钟源,则此引脚必须保持未连接。 | |||

|

| |||

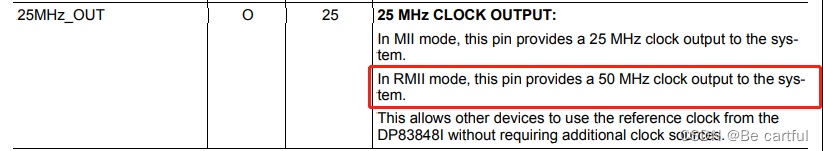

连接LED:在模式1中,此引脚指示链接的状态。链路正常时,LED将点亮。 速度指示灯:当设备处于100 Mb/s时,指示灯亮起,当设备处于10 Mb/s时指示灯熄灭。此LED的功能与所选模式无关。 活动指示灯:在模式1中,此引脚是活动指示灯,当发送或接收上存在活动时,该指示灯点亮。 连接指示灯和活动指示灯接RJ45接口,速度指示灯接LED可观察是否为100M。 | |||

|

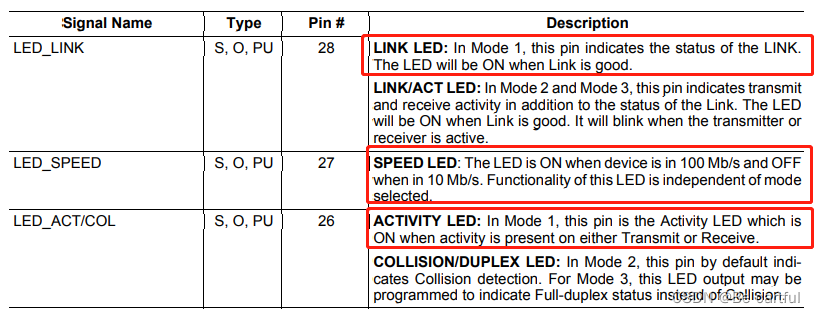

JTAG测试引脚,正常不使用,引脚内部拉力较弱 | |||

|

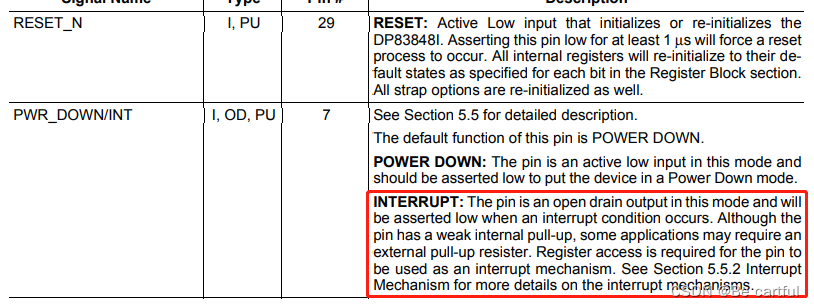

PWR——DOWN/INT引脚的默认功能为POWER DOWN(电源关闭)。 POWER DOWN(断电):在该模式下,引脚是一个有效的低输入,应该被断言为低,以将设备置于POWER DOWN(断电)模式。 中断:该引脚在此模式下为漏极开路输出,当出现中断条件时,该引脚将被断言为低电平。尽管引脚具有微弱的内部上拉,但某些应用可能需要外部上拉电阻器。将引脚用作中断机制需要寄存器访问。 一般不使用断电模式,接4.7k上拉AND单片机IO,设置为外部中断模式。 | |||

|

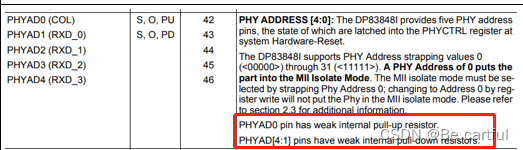

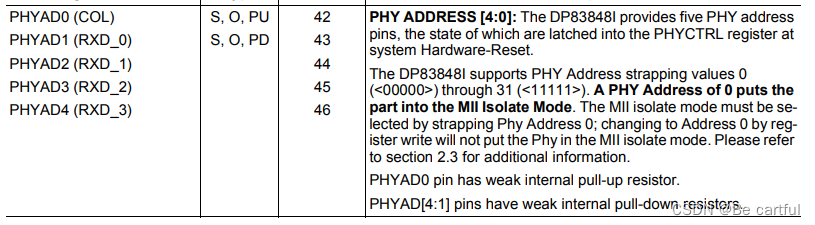

DP83848I支持PHY地址绑定值0(<00000>)到31(<11111>)。PHY地址为0将部件置于MII隔离模式。MII隔离模式必须通过绑定物理地址0来选择;通过寄存器写入更改为地址0不会将Phy置于MII隔离模式。更多信息请参考第2.3节。 PHYAD0引脚具有微弱的内部上拉电阻。 PHYAD[4:1]引脚具有较弱的内部下拉电阻。 | |||

|

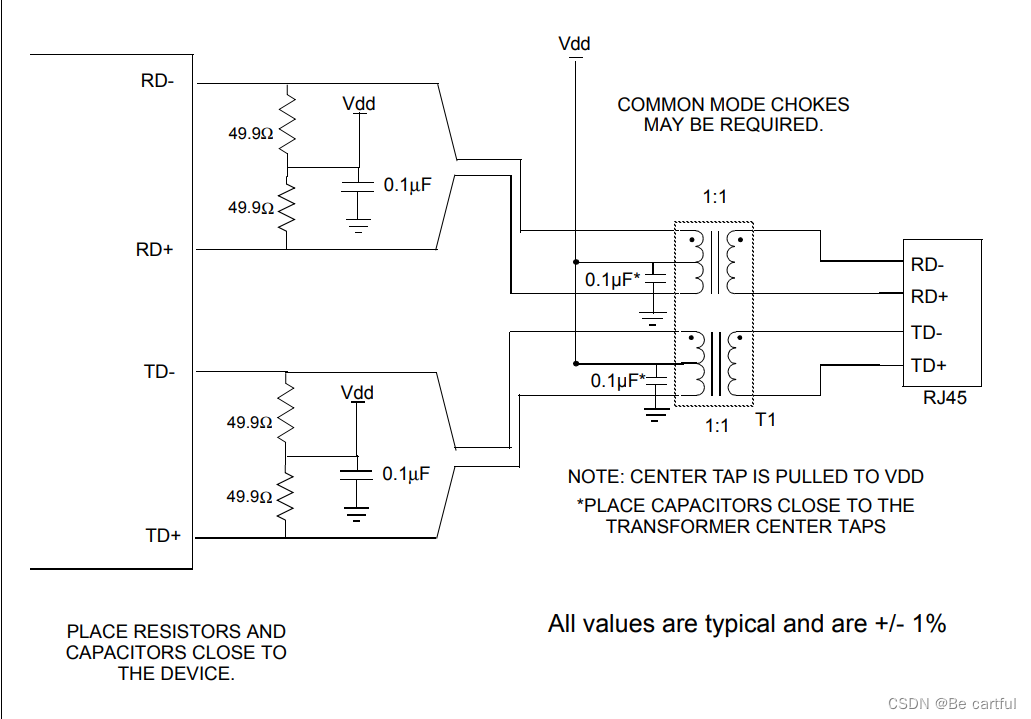

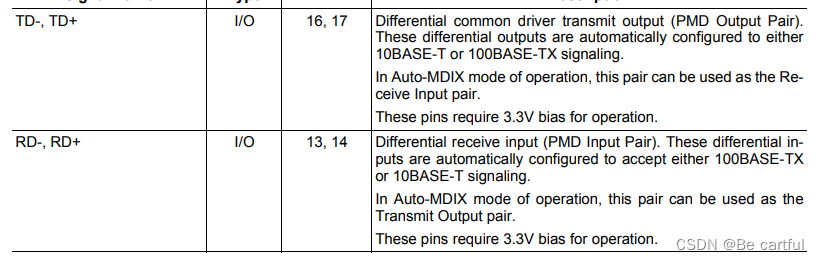

在自动MDIX操作模式下,该对可以用作接收输入对。 这些引脚需要3.3V偏压才能工作。 | |||

|

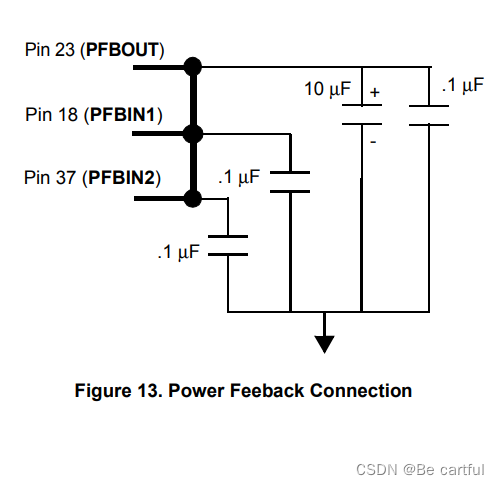

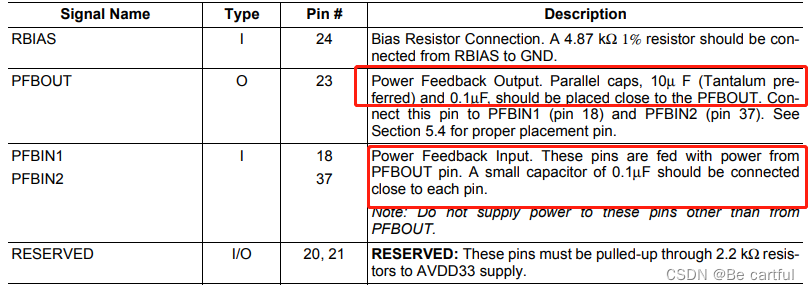

功率反馈输入:这些引脚由PFBOUT引脚供电。每个引脚附近应连接一个0.1µF的小电容器。 |

其他配置

缺省a地址配置

DP83848可设置32个地址值,由上电时5个引脚的状态决定,如下表所示。可看到,如果不在此5个引脚的外部接上拉或下拉电阻,则PHYAD0为内部上拉,其余引脚为内部下拉,所以物理地址

为1。

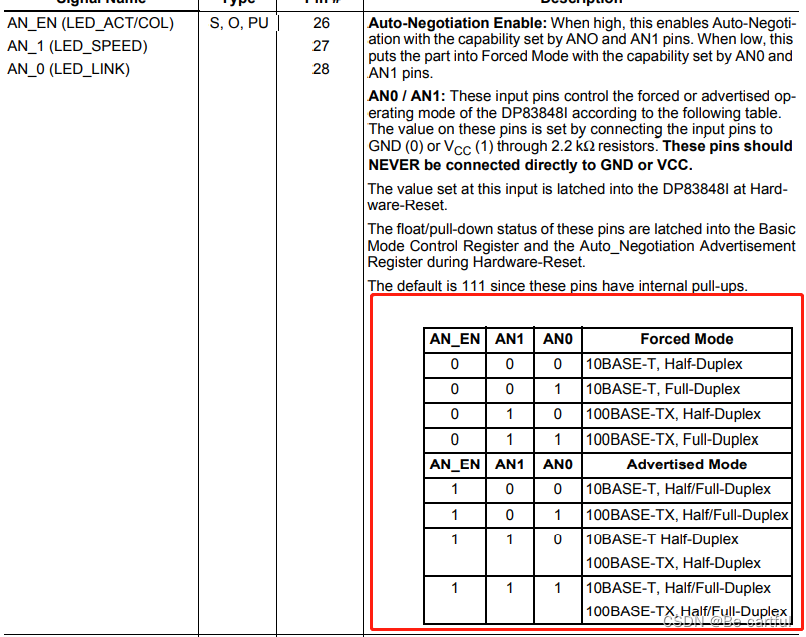

速度与双工模式的选择

可按下表确定,上电时,速度与双工模式的选择,实际上可不关心此选项,因为速度与双工模式,都可通过软件进行设置。

2

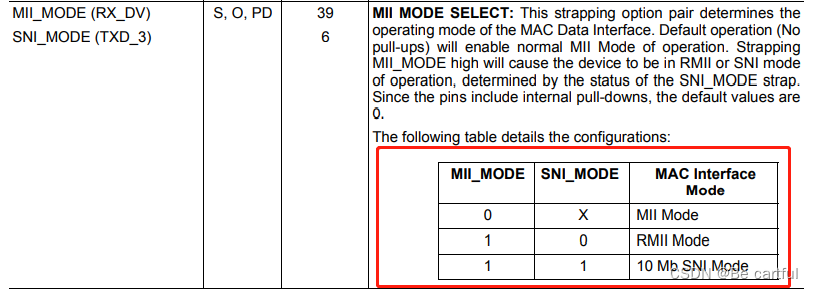

MII或RMII模式选择

可通过MII_MODE和SNI_MODE引脚进行,模式选择,如果希望运行在RMII模式,则39脚需置高,6脚需置低。39脚和6脚均有内部下拉电路,脚所以将39外部2.2K上拉,即可以让芯片工作在RMII_MODE。

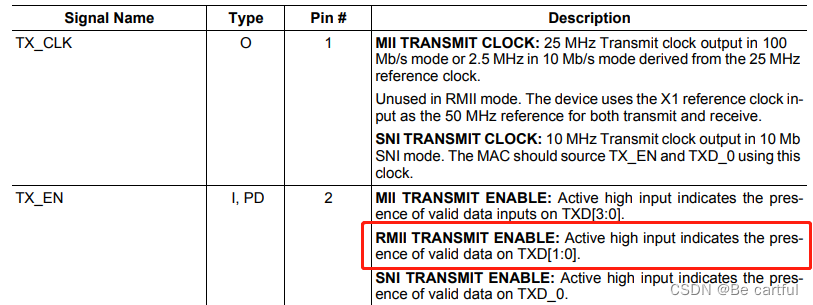

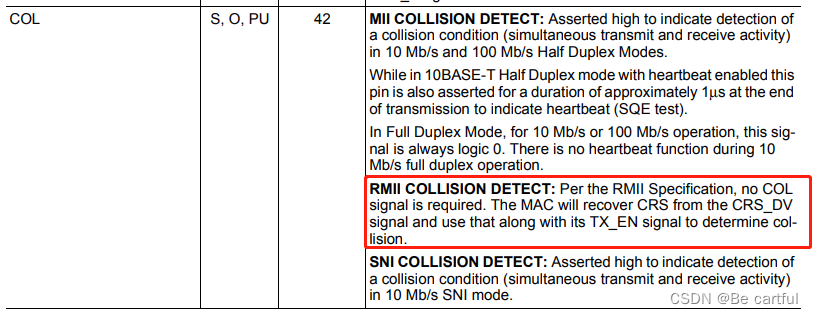

以太网的速率在100Mb/s时,MAC和PHY的交互接口就直接叫MII。对于MAC发送数据的MII,主要由TX_CLK、TXD[3:0]、TX_EN这几个信号线组成。数据信号TXD[3:0]、TX_EN在时钟下降沿变化,在时钟的上升沿时被PHY芯片有效读取。

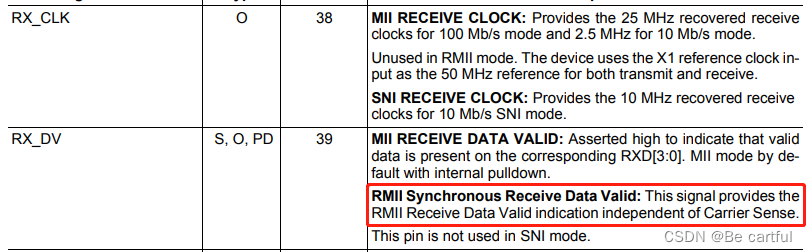

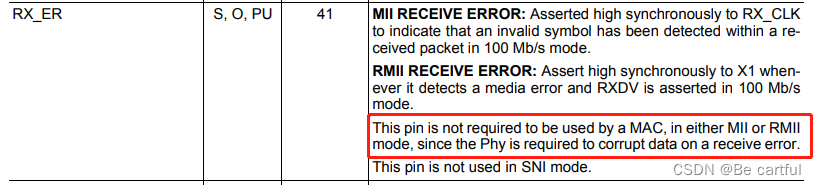

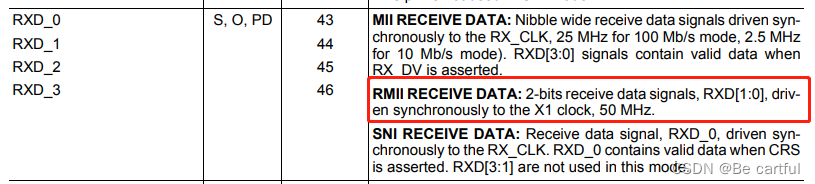

MAC接收数据的MII也跟发送的一样,只不过方向反了过来。MAC接收数据的MII主要由RX_CLK、RXD[3:0]、RX_DV、RX_ER这几个信号构成。数据是由PHY发送出来,RX_CLK下降沿时信号RX_CLK、RXD[3:0]、RX_DV、RX_ER变化,RX_CLK上升沿时MAC有效接收到数据。

RMII发送数据时MAC发送的数据和控制信号在时钟的高低电平中心变化,在时钟上升、下降沿被PHY有效读取。而且数据线跟MII相比,还少了一半,变成了TXD[1:0]。

跟MII相比,RMII的数据线少了一半,数据和控制信号在时钟的高低电平中心变化,在时钟的上升、下降沿被有效读取。

具体可以看看这篇文章MII、RMII、GMII、RGMII接口详解及硬件设计注意事项_流年過客的博客-CSDN博客

- 交叉线-直连线自动转换

按照下表所示,不加下拉电阻,则自动开启“交叉线-直连线自动转换”。

-

电源回馈电路

电源回馈电路的设计方法如下图所示,电容要贴近引

差分对接口电路设计

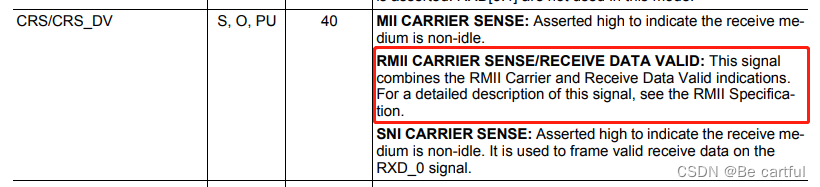

RMII的CRS_DV应接DP838348的RX_DV引脚还是接CRS_DV引脚:

按常理理解应接CRS_DV引脚,但ST公司的DEMO电路板却接的是RX_DV,网上有一段描述,当作参考:“终于搞明白了,如果RMII模式下设置全双工通讯,规范中是不用CRS信号的,因此直接用RX_DV比使用CRS_DV简单(不用从CRS_DV与TX_EN信号中恢复CRS信号)。当工作在半双工方式时,RMII需要CRS信号,因此必须使用CRS_DV信号而不能仅连RX_DV管脚;因此如果我们仅使用全双工工作,可连RX_DV管脚(那PIN39)但是如果想即支持全双工又支持半双工,那么一定要连83848的CRS_DV管脚(即PIN40)。”

管理数据时钟MDC:接入上限为25M无下限的是时钟(接入单片机提供)

管理数据时钟MDC:接入上限为25M无下限的是时钟(接入单片机提供)

1407

1407

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?