系列文章目录

分享一些fpga内使用riscv软核的经验,共大家参考。后续内容比较多,会做成一个系列。

本系列会覆盖以下FPGA厂商

- 易灵思 efinix

- 赛灵思 xilinx

-

阿尔特拉 Altera

本文内容隶属于【易灵思efinix】系列。

文章目录

前言

在efinix fpga中使用riscv是一件相对容易的事,efinix官方提供了一套集成riscv核心的应用IP,在IP catalog中可以很方便的生成、修改。裁剪IP的功能。

本文只针对其中时钟的设置进行一些说明。

一、riscv IP configuration

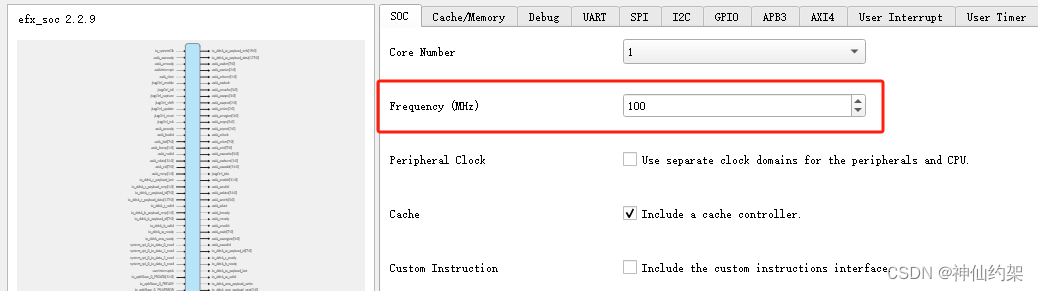

ip configuration中第一栏SOC中配置时钟。

不勾选Peripheral Clock时只配置一个时钟,默认100Mhz。

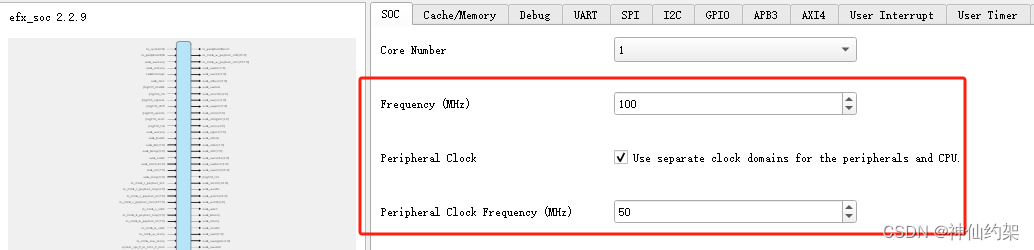

勾选Peripheral Clock后还需配置另外的时钟Peripheral Clock,一般设置为50Mhz。

查阅手册可知,Frequency用作系统时钟,外设Peripheral可使用单独的时钟。

二、软件工程中的时钟

1.soc.h

#define SYSTEM_CLINT_HZ 5000000

2.bsp.h

#define BSP_CLINT_HZ SYSTEM_CLINT_HZ

#define BSP_MACHINE_TIMER_HZ SYSTEM_CLINT_HZ

3.SPI时钟

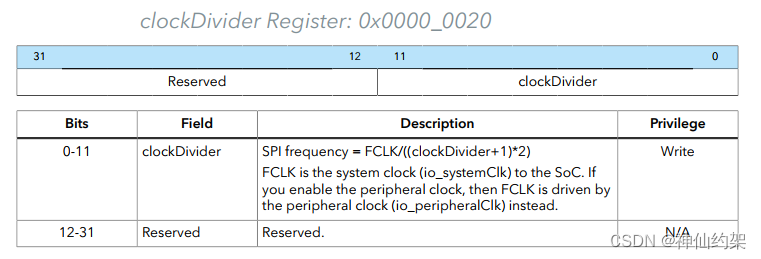

查阅手册《riscv-sapphire-ds-v3.3》,中关于spi的配置寄存器

如果clockDivider配置值10,spi频率应该是50m/22=2.27m

总结

riscv中的时钟问题是个小问题,也是大问题,一定要重视起来。给到riscv的时钟要确定,外设时钟要确定,SPI/IIC/UART的时钟频率要计算准确,避免调试过程遇到一些奇奇怪怪的问题。

233

233

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?