基于FPGA平台RISCV架构的SOC应用系统设计1

本系列文章是参加第四届“复微杯”全国大学生电子设计大赛 FPGA 赛道的作品,该平台基于 RISCV,要求在 FPGA 平台可以实现指令执行,设计思路清晰, 具体如下:

- 对所用 RISCV 的内核结构熟悉,了解其数据通路;

- 应用方案完整,设计思路清晰,能够清楚的表达设计的内容以及价值;

- 可以根据硬件上的资源实现片外启动;

- 实现串口通信功能;

- FPGA 平台实现功能;

- 提供完整设计报告及验证报告;

摘 要

信息化的时代使得物联网设备之间进行信息交换时安全成为人们非常关注的问题,物联网设备之间采用RSA加密算法进行通信时,由于自身硬件算力限制和RSA时间复杂度过高,导致加解密时间过长,不能满足快速通信的要求。为了解决这问题,本组使用RISC-V内核,设计一种带有RSA加解密加速电路的面向嵌入式领域的SoC,并能使用C语言对RSA模块寄存器进行灵活的配置,满足应用层的各种需求。最后通过FPGA开发板与电脑上位机之间通信进行验证。

关键词:RISC-V;RSA加密;硬件加速

1 概述

1.1 设计理念

物联网技术是一种通过互联网连接万物,实现万物互联的新一代网络技术,目前广泛应用于智能家居、智慧医疗、智慧城市、智能工业等领域,为人类的生活提供了便利。为了加强安全性,物联网设备之间的数据通信通常会进行加密处理。若采用对称密码进行加密,加密和解密的密钥相同,因此必须解决向接受者配送密钥这一安全问题。而使用非对称加密算法,则无需向接受者配送用于解密的密钥,解决了密钥配送问题[1]。

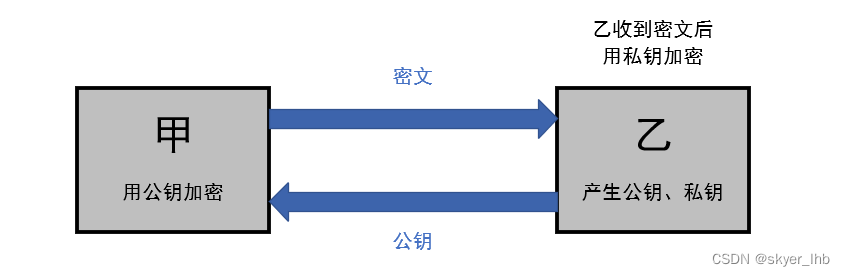

非对称密码中,密钥分为公钥和私钥两种。发送者用公钥进行加密,接收者用私钥进行解密。用非对称密码进行通信如图1所示,乙方生成公钥和私钥,公钥是公开的,任何人都可以获得,私钥则是保密的。甲方获取乙方的公钥,然后用它对信息加密。乙方得到加密后的信息,用私钥解密。

RSA 加密算法是当下较为安全的非对称加密算法[2],其算法核心为模幂运算。类似的像银行的 U 盾和身份 IC 卡等越来越多的小型硬件设备出现在银行系统、电子商务等领域中,它们通常集存储与计算为一体,数据加密与身份认证于一身,并且有结构简单,使用方便和小体积的优点。

然而如表1所示,非对称密码的解密速度非常慢,是对称密码100-1000分之一[3]。随着类似蒙哥马利模幂算法等一系列优化算法的出现[4],同时伴随着微电子水平的提高,RSA 加密算法被更加广泛的使用。如何保证信息安全的前提下实现RSA加密加速运算具有非常重要的意义。FPGA拥有丰富的硬件资源,十分适合并行和流水线技术处理数据。

| 算法 | 加密文件大小 | 加密时长 | 解密时长 | 加密后文件大小 | 加解密时长与文件大小关系 |

|---|---|---|---|---|---|

| 对称密码 | 1G | 4min | 8min | 2G | 线性 |

| 非对称密码 | 1G | 1min | 65h | 1G | 线性 |

1.2 设计思路

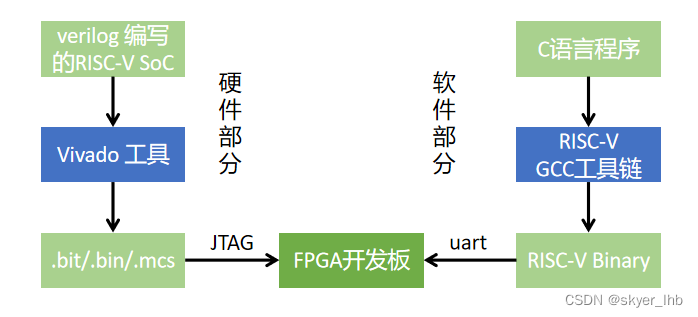

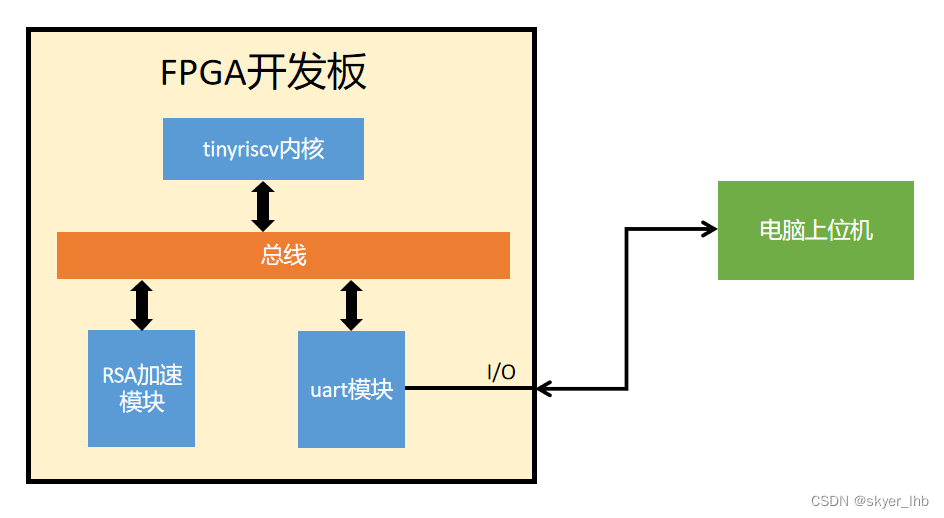

本文所设计的系统总体上可以分为两大部分,主要包含硬件和软件两部分,系统总体框图如图 2所示。硬件设计使用vivado作为开发平台[5],verilog作为开发语言,未使用任何IP核,采用tinyriscv开源内核作为处理器[6-9],在总线上添加RSA加解密模块,来加速RSA加解密这一过程。在完成SoC行为级的验证和仿真后,将代码经过编译成比特流文件下载到FPGA开发板(芯片型号XCKU060-FFVA1156-2I)。软件设计采用C语言编写设计一个uart通信函数,和RSA加解密函数,代码经过编译后通过uart将二进制数据下载rom,复位后开始程序。如图3所示,其功能为将信号从FPGA板上发送到电脑的串口调试助手上显示。电脑发送加密后的数据到FPGA中进行解密,最后返回计算机。

物联网设备在执行数据采集、处理等任务后,将数据进行加密然后传输,从而保证了设备之间通信的安全性。采用专用型的RSA硬件加速器,加速器由大量的计算单元组成,能够同一时间计算大量的数据。硬件加速器的数据并行处理能力能够极大的提高物联网芯片在数据处理方面的运行速度[10]。

对于本次RSA加速模块的设计有两个未解决难点:一个是RSA模块从ram载入数据时速度比较缓慢,一次加密用到的数据长度为1024比特,而读取一次ram最多16比特数据;第二是RSA算法中存在大数乘法(2048比特位)运算,若不进行优化,使得编译过程很复杂并且无法在FPGA上实现该运算。

1.3 设计原理

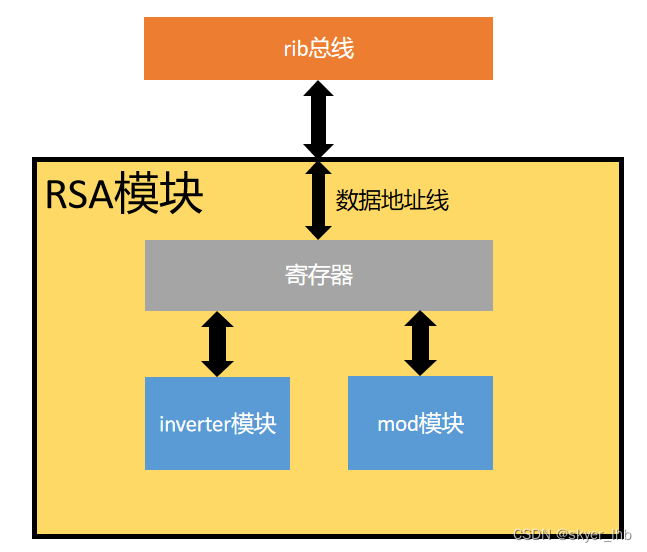

如图4所示,RSA模块的运算部分主要有inverter模块和mod模块组成,寄存器模块用来设置参数和读取参数。密钥在inverter模块中生成,其生成步骤如下:

- 通过python算法随机选择两个不相等的质数p和q;

- 计算p和q的乘积n;

- 计算n的欧拉函数φ(n)=(p-1)(q-1);

- 随机选择一个整数e(Encryption),条件是1< e < φ(n),且e与φ(n) 互质。

- 计算e对于φ(n)的模反元素d。

- 将n和e封装成公钥,n和d封装成私钥。

加解密文在mod模块中生成。加密步骤为:对代表明文的数字的E次方除以N求余数,这个余数就是密文。明文二进制数据块的长度不能大于n的二进制长度。

密

文

=

明

文

E

m

o

d

N

密文=明文^E mod N

密文=明文EmodN

解密步骤为:对表示密文的数字的D次方除以N求余数,就可以得到明文。

明

文

=

密

文

D

m

o

d

N

明文=密文^D mod N

明文=密文DmodN

其中关键参数e,n对算法的效率其关键作用。幂指数e 的巧妙选取,可以极大地改善 RSA 算法的加密速度。常见的幂指数e 如 3、17、257、4097、65537 等。幂指数e 越小,其加密速度越快。RSA密码系统的安全性取决于大数分解的困难性,即将n分解为p*q,本演示案例中p和q的长度为1024比特,n的长度为2048比特,E和D的长度和n差不多。由于生成素数p、q的产生和检测过程需要耗费一定的时间,且代码过于复杂,我们使用python语言提前生成p和q,写入到C语言中。

比特,n的长度为2048比特,E和D的长度和n差不多。由于生成素数p、q的产生和检测过程需要耗费一定的时间,且代码过于复杂,我们使用python语言提前生成p和q,写入到C语言中。

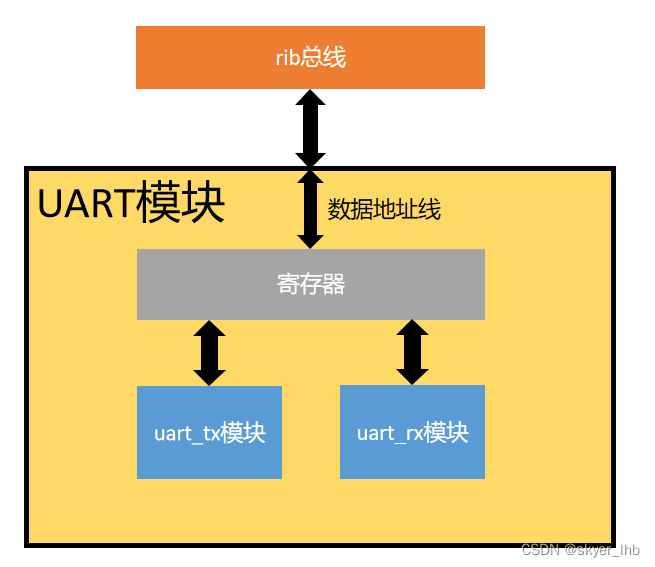

UART模块是常用的串口通信模块,此处不再赘述。

871

871

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?