SMPTE UHD-SDI IP

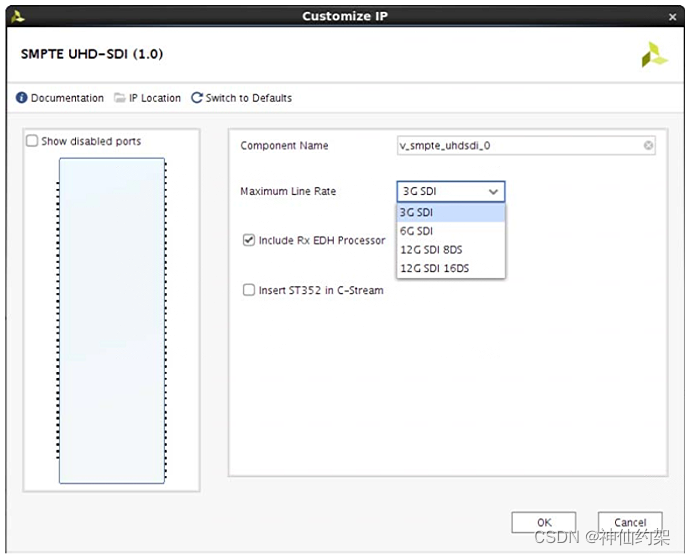

通过使用以下步骤指定与IP核心相关联的各种参数的值,可以自定义IP以在设计中使用:

1.从IP目录中选择IP。

2.双击所选IP,或从工具栏或右键单击菜单中选择“自定义IP”命令。

所需约束

rx_clk和tx_clk的周期必须根据要支持的最大线路速率进行约束。

设计中的EDH处理器还需要多周期时钟路径约束,这些约束在核心生成时自动提供。

12G时钟频率

支持12G-SDI必须将SMPTE UHD-SDI核心rx_clk和tx_clk的频率限制为297 MHz。rx_clk的源通常是串行收发器信号RXOUTCLK。tx_clk的源通常是串行收发器信号TXOUTCLK。

要在这些时钟上使用的确切约束取决于设计的分层结构,但它们类似于下面所示的约束,具有到串行收发器的TXOUTCLK和RXOUTCLK引脚的特定应用路径。

create_clock -period 3.333 -name tx0_outclk -waveform {0.000 1.667} [get_pins SDI/

GTX/gtxe2_i/TXOUTCLK]

create_clock -period 3.333 -name rx0_outclk -waveform {0.000 1.667} [get_pins SDI/

GTX/gtxe2_i/RXOUTCLK]

6G及以下时钟约束

当最大线路速率为6G-SDI或更慢时,rx_clk和tx_clk的最大时钟频率为148.5MHz,并且以下约束是适当的:

create_clock -period 6.667 -name tx0_outclk -waveform {0.000 3.333} [get_pins SDI/

GTX/gtxe2_i/TXOUTCLK]

create_clock -period 6.667 -name rx0_outclk -waveform {0.000 3.333} [get_pins SDI/

GTX/gtxe2_i/RXOUTCLK]

参考:pg205-SMPTE UHD-SDI v1.0 第四章节

本文介绍了如何根据设计需求自定义SMPTEUHD-SDIIP的rx_clk和tx_clk时钟频率,以及针对12G和6G及以下速率的时钟约束。设计者需注意约束rx_clk和tx_clk周期以匹配最大线路速率并确保多周期时钟路径的设置。

本文介绍了如何根据设计需求自定义SMPTEUHD-SDIIP的rx_clk和tx_clk时钟频率,以及针对12G和6G及以下速率的时钟约束。设计者需注意约束rx_clk和tx_clk周期以匹配最大线路速率并确保多周期时钟路径的设置。

737

737

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?