大家好,欢迎来到今天的总线学习时间!如果你对电子设计、特别是FPGA和SoC设计感兴趣,那你绝对不能错过我们今天的主角——AXI4总线。作为ARM公司AMBA总线家族中的佼佼者,AXI4以其高性能和高度可扩展性,成为了现代电子系统中不可或缺的通信桥梁。

上一课时我们了解到AXI4有五大独立通道,对他们有了初步的认识,这一课时我们再深入的了解下AXI的基础事务,进一步加深认识。

这里会有一系列的课程,和大家分享AMBA总线家族,欢迎大家一起学习,收藏点赞。

系列文章

【总线】设计fpga系统时,为什么要使用总线?-CSDN博客

【总线】AMBA总线家族的明星成员:AXI协议简介-CSDN博客

【总线】AXI4第一课时:揭秘AXI4总线的五大独立通道-CSDN博客

【总线】AXI4第二课时:深入AXI4总线的基础事务-CSDN博客

- 回顾5个通道,每一个AXI传输通道都是单方向的

- 读地址 read address

- 读数据 read data

- 写地址 write address

- 写数据 write data

- 写回复 write response

- 每个事务都有地址和控制信息在地址通道( address channel)中,用来描述被传输数据的性质。

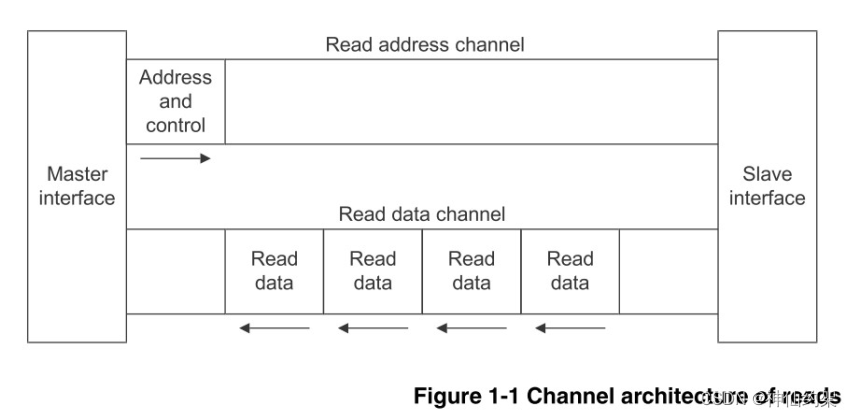

- 读事务的结构图如下。

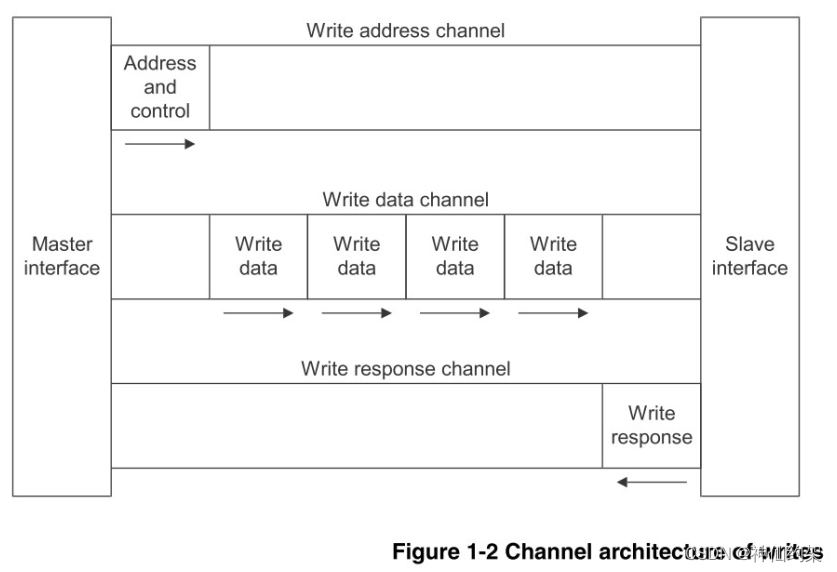

- 写事务的结构图如下

- 这 5 条独立的通道都包含一个信息信号和一个双路的 VALD、 READY 握手机制。

- 信息源通过 VALID 信号来指示通道中的数据和控制信息什么时候有效。目地源用READY 信号来表示何时能够接收数据。 读数据和写数据通道都包括一个LAST 信号,用来指明一个事物传输的最后一个数据。

- 读和写事务都有他们自己的地址通道,这地址通道携带着传输事务所必须的地址和信息。

独立的读写地址通道:每个读写事务都拥有自己的地址通道。这意味着读事务和写事务分别通过它们自己的地址通道进行通信。

地址和控制信息:每个地址通道都携带了执行事务所需的全部地址和控制信息。这包括事务的目标地址、事务的类型、大小等。

支持的机制:

- 可变长度突发:突发(Burst)是指连续的数据传输。在AXI协议中,突发的长度可以变化,从1到16个数据传输(transfers)。

- 突发传输大小:每个突发传输的大小可以是8到1024位(bits),这提供了灵活的数据传输粒度。

- 包装(Wrapping)、增量(Incrementing)和非增量(Non-incrementing)突发:

- 包装突发:在达到某个边界时,地址会“包装”回到较低的地址继续传输。

- 增量突发:地址随着每个传输而递增。

- 非增量突发:地址在突发传输中保持不变。

- 原子操作:原子操作确保在执行期间不会被其他事务中断,使用独占(Exclusive)或锁定(Locked)访问来实现。

- 系统级缓存和缓冲控制:AXI协议支持缓存和缓冲机制,以提高系统的性能和效率。这允许对数据进行缓存、合并写操作等。

总结来说,这部分强调了AXI协议在处理读写事务时,通过地址通道提供了一系列的高级特性,以支持复杂的系统设计和优化数据传输效率。

- 读数据通道传送着从设备到主机的读数据和读响应信息。读响应信息指明读事务的完成状态。

- 写数据通路传送着主机向设备的写数据。每八个数据都会有一个 byte lane ,用来指明数据总线上面的哪些 byte 有效。

- 写响应通道提供了设备响应写事务的一种方式。

写响应通道的作用:在AXI协议中,写响应通道是用于从机(Slave)向主机(Master)发送写事务响应的通信路径。这意味着,当主机向从机发起写事务请求后,从机通过写响应通道告知主机该事务是否成功完成。

完成信号的使用:所有写事务都使用完成信号(Completion Signal)来指示事务的结束。完成信号是写事务中一个重要的部分,它确保了主机知道何时写操作已经完成。

完成信号的触发时机:完成信号是针对每个突发(Burst)触发一次,而不是针对突发内的每个单独数据传输。这里的“突发”是指一系列连续的写操作,它们共享相同的地址和控制信息。

- 例如,如果一个突发包含4个数据传输,那么完成信号将在最后一个数据传输完成后触发一次,而不是在每个数据传输后分别触发。

事务完成的确认:完成信号的存在确保了主机可以准确地知道何时写事务已经完全处理完毕,从而可以继续执行后续的操作或者发起新的事务。

总结来说,这部分强调了写响应通道在AXI协议中用于指示写事务完成的重要性,以及完成信号是按突发而不是按单个数据传输来触发的机制。这有助于提高系统的效率,因为它减少了需要发送的信号数量,并且允许主机更有效地管理数据传输和事务处理。

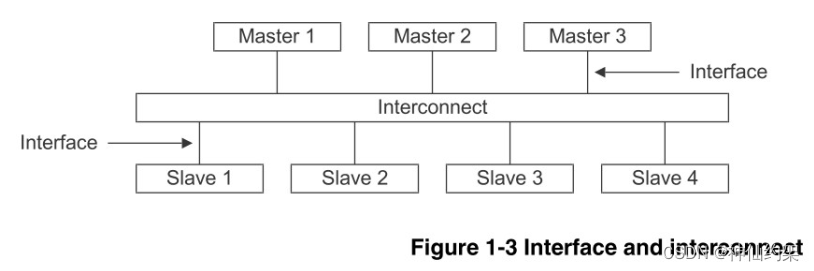

- 主机和设备的接口和互联图如下。

在AMBA AXI协议中接口定义如何支持多种不同的互连(interconnect)实现方式,以及系统设计中常见的几种互连方法。以下逐点解释:

接口定义的灵活性:AXI协议的接口定义允许实现多种不同的互连架构。这意味着设计者可以根据系统的需求和约束,选择或设计合适的互连方案。

互连的等效设备:在AXI协议中,互连在功能上等同于一个具有对称的主(master)和从(slave)端口的设备。这样,实际的主设备和从设备可以连接到这个互连设备上,就像它们直接连接到另一个AXI设备一样。

常见的互连方法:

- 共享地址和数据总线:所有设备共享相同的地址和数据总线。这是一种简单的互连方式,但可能在高负载下成为性能瓶颈。

- 共享地址总线和多个数据总线:系统中有一条共享的地址总线,但是有多条数据总线。这样可以在保持地址总线简单性的同时,提高数据传输的带宽。

- 多层互连,具有多个地址和数据总线:这是一种更复杂的互连方式,可能包含多个层次的地址和数据总线,以支持大规模或高性能的系统设计。

地址和数据通道带宽的需求差异:在大多数系统中,地址通道的带宽需求远小于数据通道。这是因为地址信息通常比数据量小得多,而且通常不需要那么高的传输速率。

系统性能与互连复杂性的平衡:通过使用共享地址总线和多个数据总线的方案,系统可以在保持较低互连复杂性的同时,实现较高的系统性能。这种方法允许并行数据传输,提高了整体的数据传输效率。

总结来说,这部分内容强调了AXI协议提供的灵活性,允许设计者根据系统的具体需求选择最合适的互连策略,并通过合理的互连设计实现高性能和适中的系统复杂性。

- 寄存器切片的使用

单向传输:每个AXI通道仅支持一个方向的信息传输,没有规定各个通道之间必须有固定的关系。

灵活性:由于通道之间没有固定的顺序要求,可以在任何通道中插入寄存器切片,而不会影响其他通道的操作。

寄存器切片的作用:寄存器切片可以被看作是一种缓冲机制,它在数据传输路径中增加了一个或多个寄存器阶段。这样做的目的是为了在设计中引入可配置的延迟,以适应不同操作频率的组件。

延迟与频率的权衡:插入寄存器切片会增加数据传输的延迟(因为数据需要通过额外的寄存器阶段),但这样做可以提高系统的最高操作频率。这是因为额外的寄存器可以用于时钟域交叉(Clock Domain Crossing, CDC),减少亚稳态的风险,并允许不同频率的组件协同工作。

互连中的寄存器切片使用:在互连(interconnect)的几乎任何位置都可以使用寄存器切片。这为设计者提供了灵活性,可以根据系统的需求在不同的位置插入寄存器切片。

性能优化:在处理器和高性能内存之间可能使用直接、快速的连接,以最小化延迟。而在通往性能要求不高的外围设备的较长路径上,可以使用简单的寄存器切片来隔离,这样可以降低对高速时钟的需求,同时减少功耗。

总结来说,寄存器切片是一种设计工具,用于在系统设计中平衡延迟和操作频率,以及适应不同性能要求的组件。通过在AXI通道中适当地使用寄存器切片,设计者可以实现更高效的系统性能和更低的功耗。

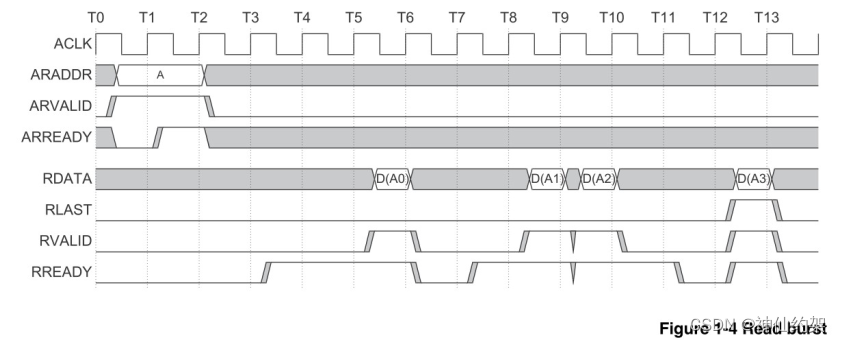

- 传输地址信息和数据都是在 VALID 和 READY 同时为高时有效。

- 突发式读的时序图如下

当地址出现在地址总线后, 传输的数据将出现在读数据通道上。 设备保持 VALID为低直到读数据有效。为了表明一次突发式读写的完成,设备用 RLAST 信号来表示最后一个被传输的数据。

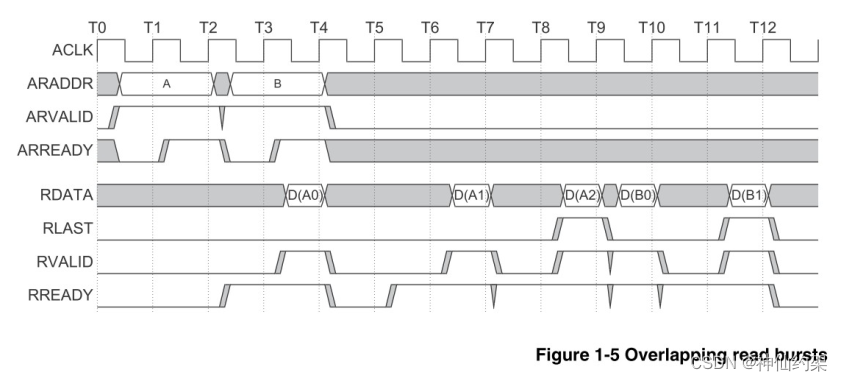

- 重叠突发式读时序图如下

设备会在第一次突发式读完成后处理第二次突发式读数据。也就意味着,主机一开始传送了两个地址给设备。 设备在完全处理完第一个地址的数据之后才开始处理第二个地址的数据。

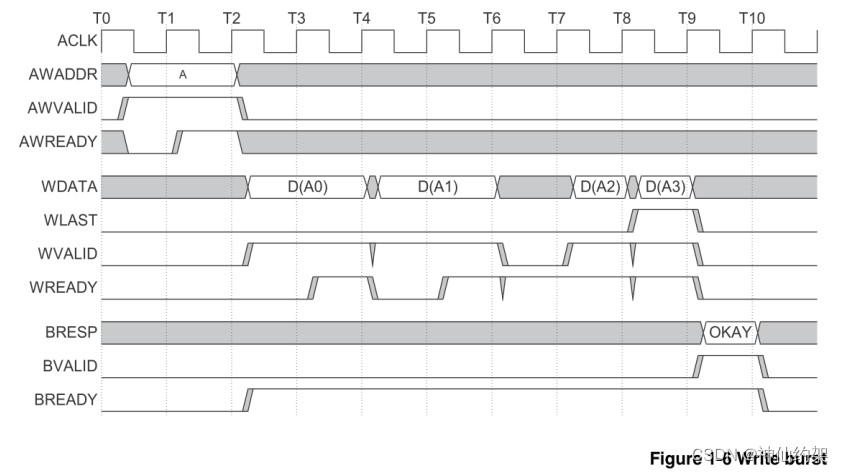

- 突发式写时序图如下

这一过程的开始时,主机发送地址和控制信息到写地址通道中,然后主机发送每一个写数据到写数据通道中。当主机发送最后一个数据时, WLAST 信号就变为高。当设备接收完所有数据之后他将一个写响应发送回主机来表明写事务完成。

- AXI 协议支持乱序传输。他给每一个通过接口的事务一个 IDtag。协议要求相同 ID tag 的事务必须有序完成,而不同 ID tag 可以乱序完成。

在AXI协议中,"无序传输"(out-of-order transactions)是一个重要的特性,它允许系统在处理多个事务时提高效率和吞吐量。这段描述提到的“复杂从机(Complex slaves)可以无序返回读取数据”可以理解如下:

复杂从机的能力:在AXI协议中,从机(Slave)可以是简单的或者复杂的。复杂从机拥有更高级的功能,比如内部缓冲(buffering)或者其他能够改善性能的特性。

无序返回数据:复杂从机在处理多个读取事务时,可能会根据其内部逻辑或优化,选择在不同顺序返回数据项。这意味着,即使某些数据项属于较早发起的读取事务,它们也可能在属于较晚事务的数据项之后被返回。

内部缓冲的影响:复杂从机可能拥有内部缓冲区,能够暂存一定量的数据。如果一个较晚发起的读取请求所需的数据已经存在于缓冲区中,那么复杂从机可以更快地提供这些数据,即使这意味着跳过了一些较早但尚未处理的请求。

对系统性能的影响:这种无序返回数据的能力可以减少等待时间和提高系统的整体性能。例如,如果系统能够快速响应对已经缓存数据的请求,那么它就可以更有效地利用资源,减少主设备(Master)的空闲时间。

事务ID的作用:尽管从机可以无序返回数据,但是每个事务都会分配一个唯一的ID,以确保每个事务的完整性和可追踪性。这样,即使数据返回是无序的,主设备也能够识别和处理每个事务的正确数据。

8026

8026

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?