目录

1.2.2. BAR(Base Address Register)

1. 简介

1.1. 配置空间简介

每个PCIe设备都有一段空间,Host软件可以读取它获得该设备的一些信息,也可以通过它来配置该设备,所以这段空间就被称为配置空间。PCie的配置空间是协议规定好的,每一个字段都是有定义的。

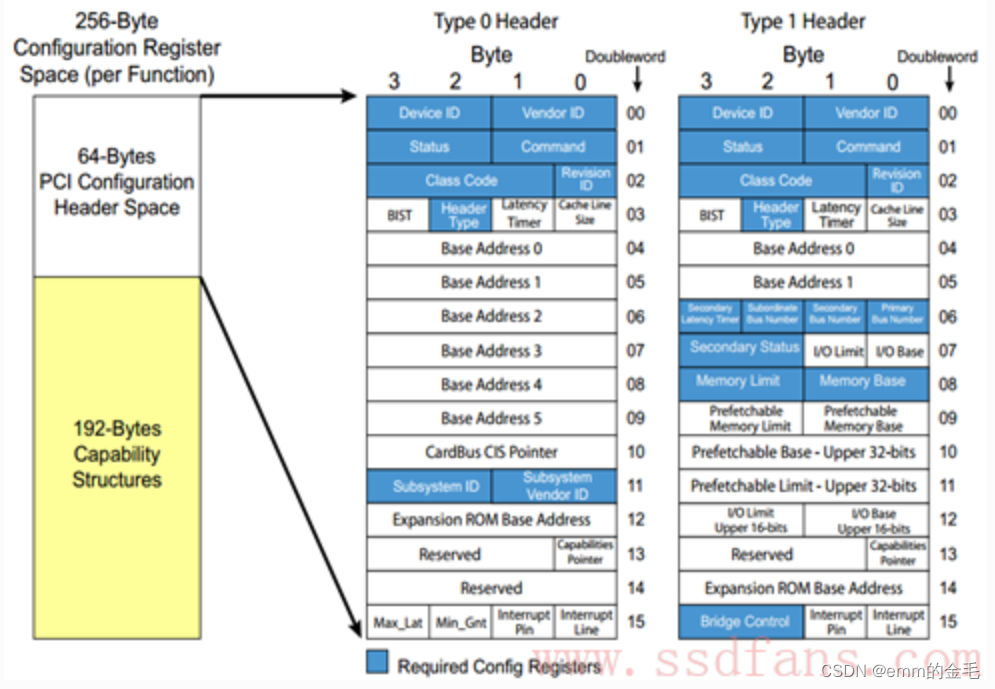

配置空间在PCI/PCI-X时代就已经出现了,只不过那时的配置空间大小为256字节。整个配置空间就是一系列寄存器的集合,其中Type 0是Endpoint的配置,Type 1是Bridge(PCIe时代就是Switch)的配置,都由两部分组成:64 Bytes的Header+192Bytes的Capability结构,后者是设备告诉Host它所具有的功能。

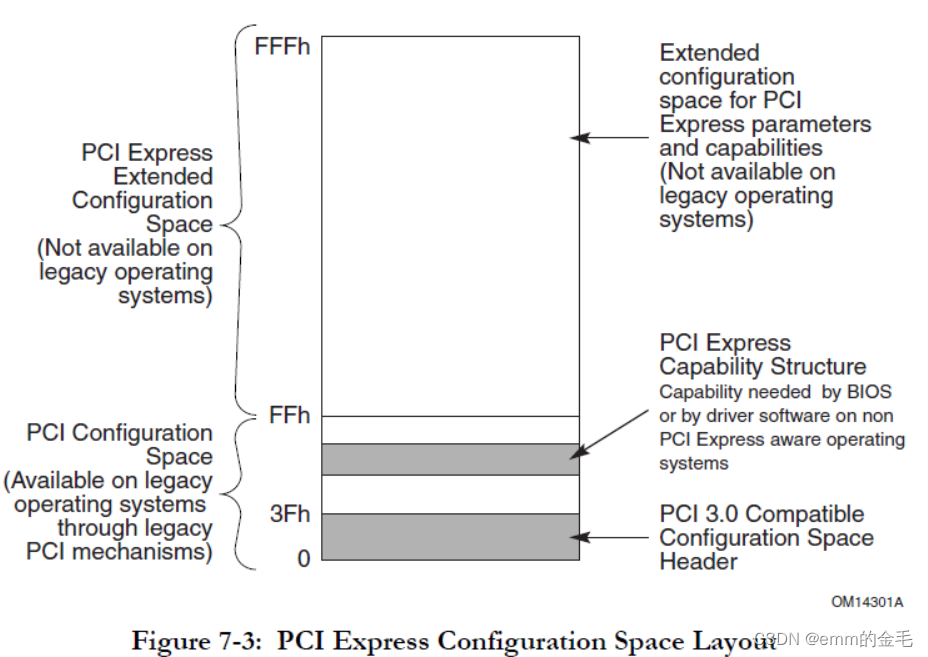

进入PCIe时代,配置空间的大小从256字节增加到4KB,但是64字节的可配置空间的头部大小没有改变。

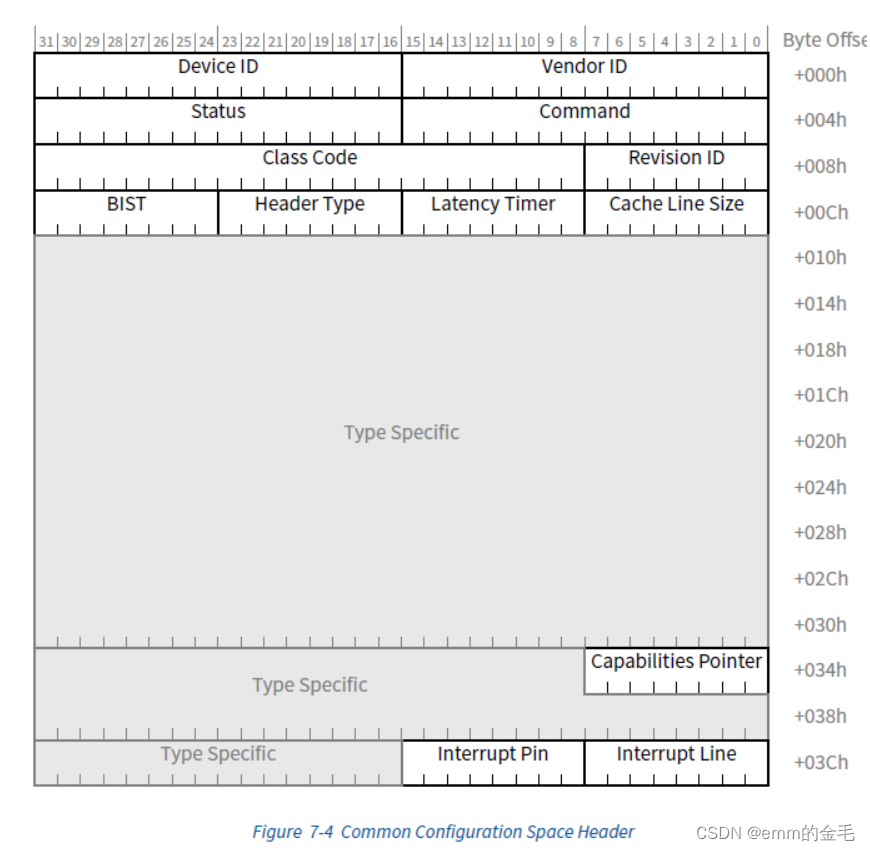

前面说到,PCIe有两种设备:Type0表示终端设备,Type1表示Switch,由于职责的不同,其配置空间的内容也不同。但是为了保持一致,方便管理,这两类设备的配置有很多相同的部分,比如配置空间的头部,如下图所示:

1.2. Type 0设备的配置空间:

1.2.1. 配置空间的结构

和公共字段相比,Type 0的配置空间多了一些字段:

- Subsystem ID和Subsystem Vendor ID:顾名思义,用来帮助每个设备厂商标识更细粒度设备信息

- Cardbus CIS Pointer Register:已经废弃,以前用于PC-Card中

- Expansion ROM Base Address Register:用于描述设备的ROM的地址,这里和我们的主要内容关系不大,就不过多展开了

1.2.2. BAR(Base Address Register)

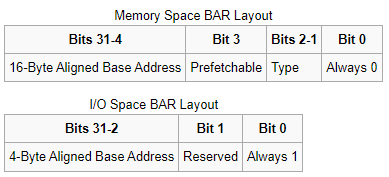

除了上面这些字段,其中最重要的就是BAR了。在Type 0的配置空间中,BAR区域有24个字节,可以保存6个指针/地址,每一个都可以用来描述一个不同的内存空间或者IO空间的地址和范围。

为了描述不同类型的地址空间,这里的指针不是单纯的指针,而有着自己的结构,如下 [1] [3] :

其中:

- 最低位Bit 0:是一个标志位,用于描述地址空间的类型,0表示内存空间,1表示IO空间

- Memory Space中的Bit [2:1] - Type:用于描述内存空间的类型,00表示32位地址空间,10表示64位地址空间

- Memory Space中的Bit 3 - Prefetchable:用于描述内存空间是否支持预取,0表示不支持,1表示支持。如果一段内存空间支持预取,它意味着读取时不会产生任何副作用,所以CPU可以随时将其预取到DRAM中。而如果预取被启用,在读取数据时,内存控制器也会先去DRAM查看是否有缓存。当然,这是一把双刃剑,如果数据本身不支持预取,那么除了可能导致数据不一致,多一次DRAM的查询还会导致速度下降。

另外也许你会觉得很奇怪,一个32位的空间,又是如何又表示地址又表示范围呢?这里其实和BAR的初始化过程有关。BAR的寄存器初始化主要有三步 [1](7.5.1.2.1 Base Address Registers):

- BIOS将全1的地址写入BAR寄存器,这样会导致BAR寄存器的值被重置,并被设备重新写入初始值。这个初始值是一个地址,表示如果将这个BAR寄存器指向的内存放在物理内存的最后,其地址为多少。比如,如果我们需要4KB的内存空间,那么这个地址就是0xFFFFF000,当然这里还需要加上最低几

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1116

1116

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?