《数字逻辑电路》实验二 组合逻辑电路设计(一)

目录

一、实验目的

通过实验,进一步熟悉使用 vivado 进行可配置 IP 核设计的方法,对各种门电路的逻辑有更加感性的认识,同时也为今后的实验以及后续的课程积累基本的门电路IP核。

二、实验内容

(1)采用Verilog HDL 程序,设计与门IP核并仿真测试;(见2.1.2)(选)

(使用 Verilog HDL 语言的数据流描述方法设计一个数据宽度可在 1~32 之间变化,输入 端口数可在 2~8 之间变化的与门 andgate,输入端 8 个,分别是 a,b,c,d,e,f,g,h,输出端为 q。 利用仿真来验证你的设计。并将该与门封装成可配置输入端口数和数据宽度的“与门”IP 核)

(以下实验采用数据流描述法)

(2)采用Verilog HDL程序,设计74LS00并下载测试;(见2.1.4)

(3)采用Verilog HDL程序,设计1位数据的2选一编码器并仿真测试;(见2.2.1)

(4)采用Verilog HDL程序,设计8选1数据选择器74LS151,并下载测试。(见2.2.2)

三、代码与截图

源代码1:test_3_204.v

`timescale 1ns / 1ps

//

module test_3_204//andgate

#(parameter Port_Num = 2, // 指定缺省的输入是 2 个输入端口

parameter WIDTH=8) // 指定数据宽度参数,缺省值是 8

(

input [(WIDTH-1):0] a,

input [(WIDTH-1):0] b,

input [(WIDTH-1):0] c,

input [(WIDTH-1):0] d,

input [(WIDTH-1):0] e,

input [(WIDTH-1):0] f,

input [(WIDTH-1):0] g,

input [(WIDTH-1):0] h,

output [(WIDTH-1):0] q

);

assign q = (a & b & c & d & e & f & g & h);

endmodule

测试代码1.1:test_3_204_sim.v

`timescale 1ns / 1ps

//

module test_3_204_sim( );

// input

reg a=0;

reg b=0;

reg c=1;

reg d=1;

reg e=1;

reg f=1;

reg g=1;

reg h=1;

//outbut

wire q;// 实例化与门的时候,设定宽度为 1

test_3_204 #(8,1) u(.a(a),.b(b),.c(c),.d(d),

.e(e),.f(f),.g(g),.h(h),.q(q));

initial begin

#100 a=1;

#100 begin a=0;b=1;end

#100 a=1;

end

endmodule

测试代码1.2:test_3_32_204_sim.v

`timescale 1ns / 1ps

//

module test_3_32_204_sim();

// input

reg [31:0] a=32'h00000000;

reg [31:0] b=32'h00000000;

reg [31:0] c=32'hffffffff;

reg [31:0] d=32'hffffffff;

reg [31:0] e=32'hffffffff;

reg [31:0] f=32'hffffffff;

reg [31:0] g=32'hffffffff;

reg [31:0] h=32'hffffffff;

//outbut

wire [31:0] q;// 实例化与门的时候,设定宽度为 32

test_3_204 #(8,32) u(.a(a),.b(b),.c(c),.d(d),

.e(e),.f(f),.g(g),.h(h),.q(q));

initial begin

#100 a=32'hffffffff;

#100 begin a=32'h00000000;b=32'hffffffff;end

#100 a = 32'h007fa509;

#100 a=32'hffffffff;

end

endmodule

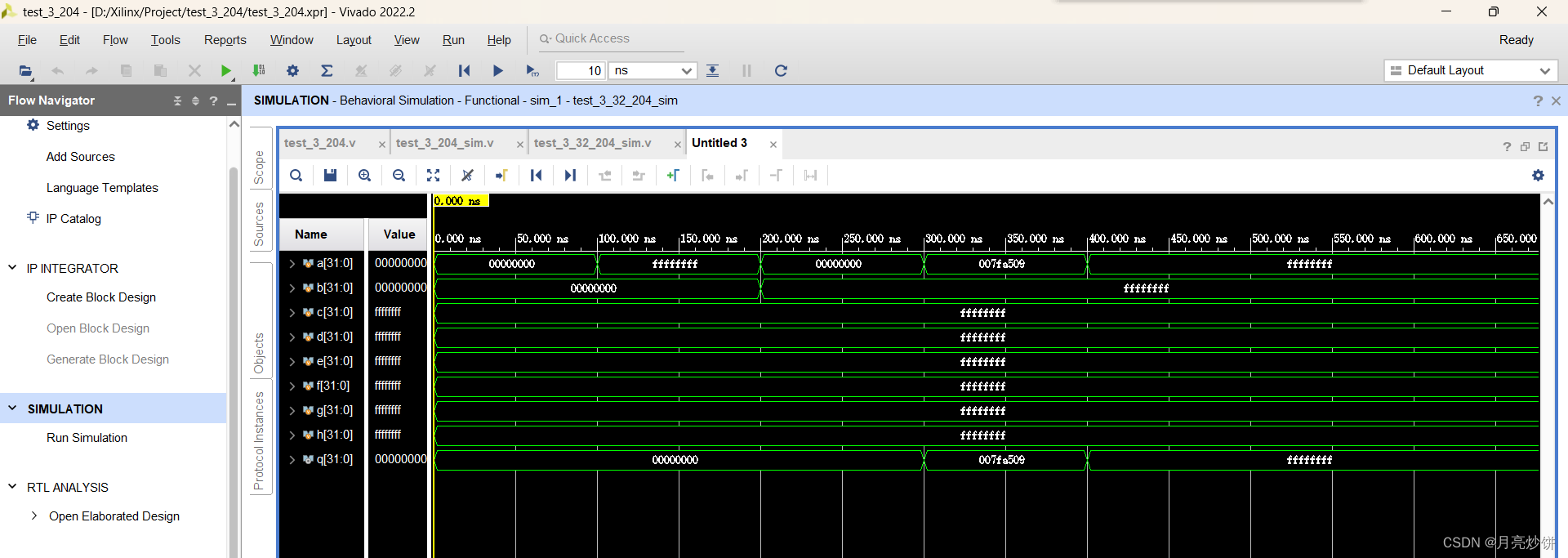

仿真截图1.1:

仿真截图1.2:

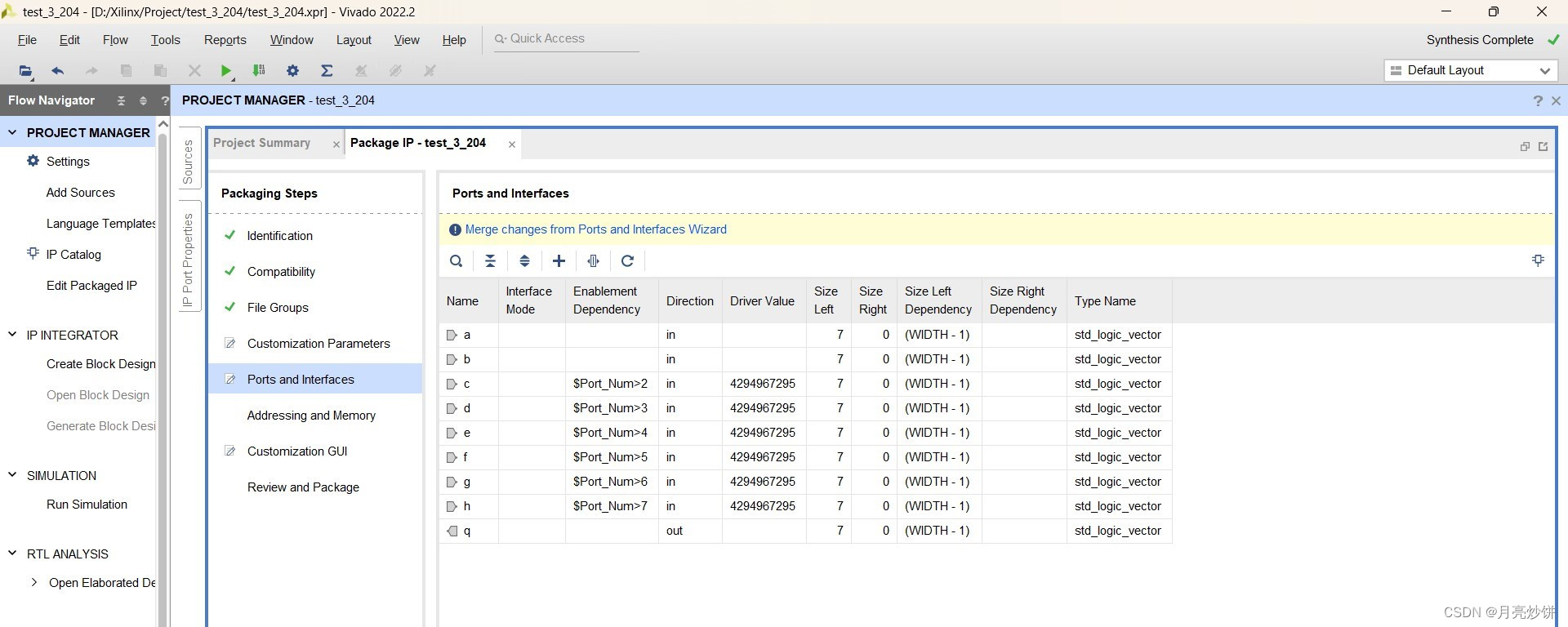

端口存在条件约束:

源代码2:LS7400_204.v

`timescale 1ns / 1ps

//

module LS7400_204(

input A1, B1,

output Y1,

input A2, B2,

output Y2,

input A3,

input B3,

output Y3,

input A4,

input B4,

output Y4

);

assign Y1 = ~(A1 & B1);

assign Y2 = ~(A2 & B2);

assign Y3 = ~(A3 & B3);

assign Y4 = ~(A4 & B4);

endmodule

测试代码2:LS7400_204_sim.v

`timescale 1ns / 1ps

//

module LS7400_204_sim();

reg A1 = 0;

reg B1 = 0;

reg A2 = 0;

reg B2 = 0;

reg A3 = 0;

reg B3 = 0;

reg A4 = 0;

reg B4 = 0;

wire Y1;

wire Y2;

wire Y3;

wire Y4;

LS7400_204 u(

.A1(A1),

.B1(B1),

.A2(A2),

.B2(B2),

.A3(A3),

.B3(B3),

.A4(A4),

.B4(B4),

.Y1(Y1),

.Y2(Y2),

.Y3(Y3),

.Y4(Y4)

);

initial begin

#100 A1 = 1;

#100 B1 = 1;

#100 A2 = 1;

#100 B2 = 1;

#100 A3 = 1;

#100 B3 = 1;

#100 A4 = 1;

#100 B4 = 1;

end

endmodule

引脚约束2:LS7400_204.xdc

set_property IOSTANDARD LVCMOS33 [get_ports A3]

set_property IOSTANDARD LVCMOS33 [get_ports A4]

set_property IOSTANDARD LVCMOS33 [get_ports Y3]

set_property IOSTANDARD LVCMOS33 [get_ports Y4]

set_property IOSTANDARD LVCMOS33 [get_ports B3]

set_property IOSTANDARD LVCMOS33 [get_ports Y1]

set_property IOSTANDARD LVCMOS33 [get_ports Y2]

set_property IOSTANDARD LVCMOS33 [get_ports A1]

set_property IOSTANDARD LVCMOS33 [get_ports B4]

set_property IOSTANDARD LVCMOS33 [get_ports A2]

set_property IOSTANDARD LVCMOS33 [get_ports B1]

set_property IOSTANDARD LVCMOS33 [get_ports B2]

set_property PACKAGE_PIN W4 [get_ports A1]

set_property PACKAGE_PIN R4 [get_ports A2]

set_property PACKAGE_PIN T4 [get_ports A3]

set_property PACKAGE_PIN T5 [get_ports A4]

set_property PACKAGE_PIN U5 [get_ports B1]

set_property PACKAGE_PIN W6 [get_ports B2]

set_property PACKAGE_PIN W5 [get_ports B3]

set_property PACKAGE_PIN U6 [get_ports B4]

set_property PACKAGE_PIN A21 [get_ports Y1]

set_property PACKAGE_PIN E22 [get_ports Y2]

set_property PACKAGE_PIN D22 [get_ports Y3]

set_property PACKAGE_PIN E21 [get_ports Y4]

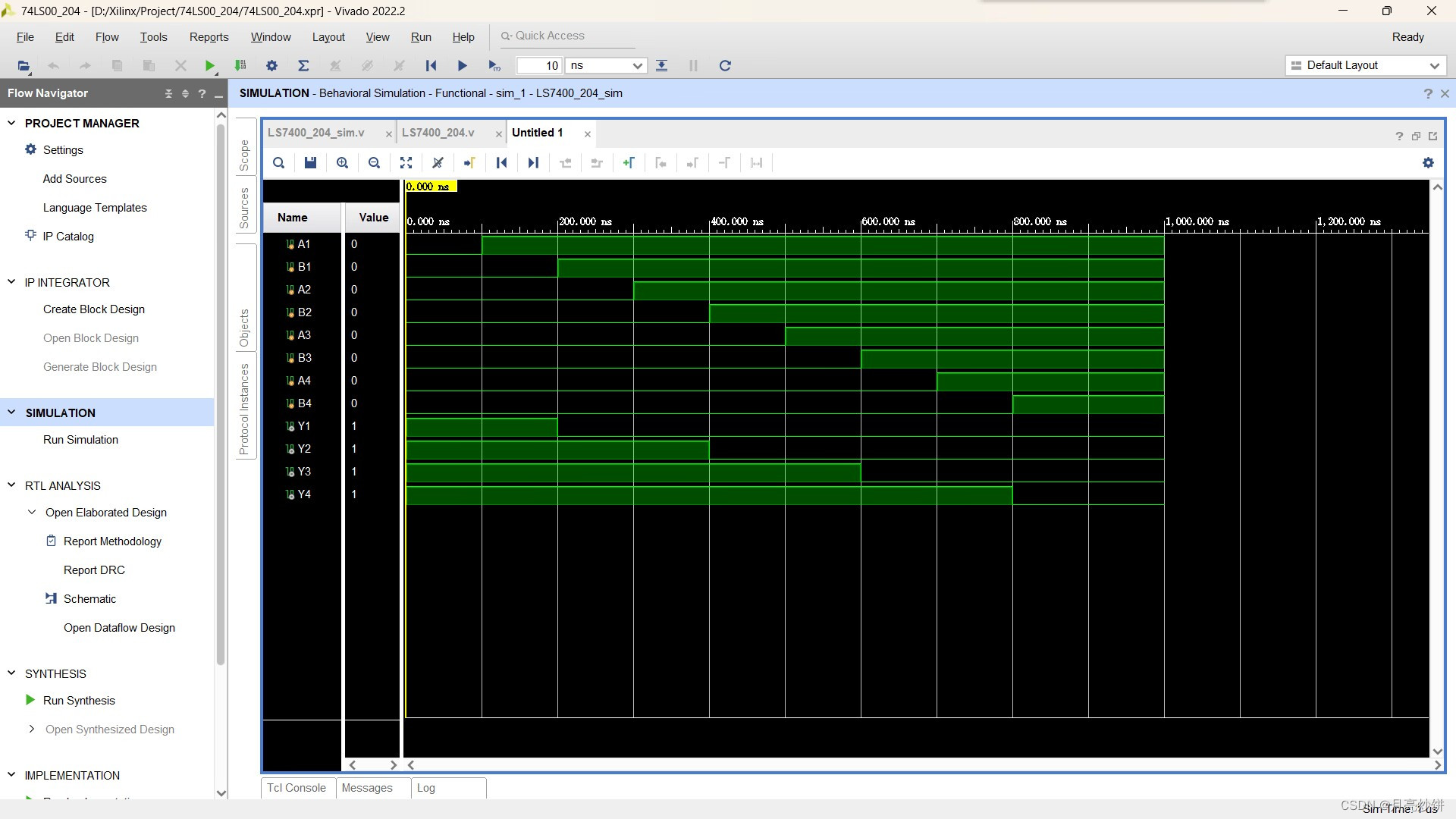

仿真截图2:

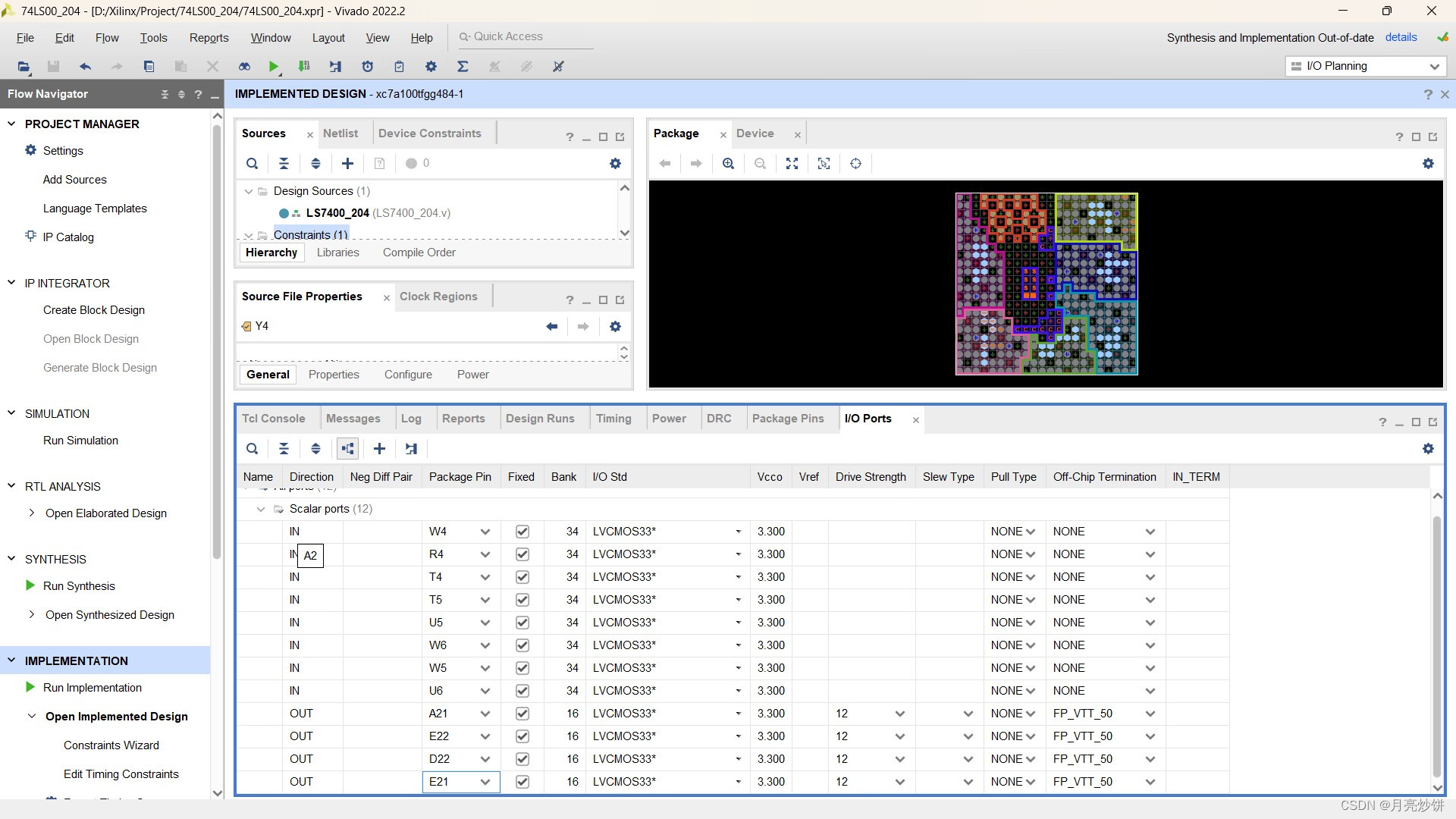

引脚锁定截图2:

源代码3:mux2x1_204.v

`timescale 1ns / 1ps

//

module mux2x1_204(

input a,

input b,

input s,

output c

);

assign c = (a & ~s) | (b & s);

endmodule

仿真代码3:mux2x1_204_sim.v

`timescale 1ns / 1ps

//

module mux2x1_204_sim();

// input

reg a=0;

reg b=1;

reg s=0;

//output

wire c;

mux2x1_204 u(

.a(a),

.b(b),

.s(s),

.c(c)

);

initial begin

# 200 s=1;

end

endmodule

引脚约束3:mux2x1_204.xdc

set_property IOSTANDARD LVCMOS33 [get_ports a]

set_property IOSTANDARD LVCMOS33 [get_ports b]

set_property IOSTANDARD LVCMOS33 [get_ports c]

set_property IOSTANDARD LVCMOS33 [get_ports s]

set_property PACKAGE_PIN A21 [get_ports c]

set_property PACKAGE_PIN R4 [get_ports b]

set_property PACKAGE_PIN W4 [get_ports a]

set_property PACKAGE_PIN Y9 [get_ports s]

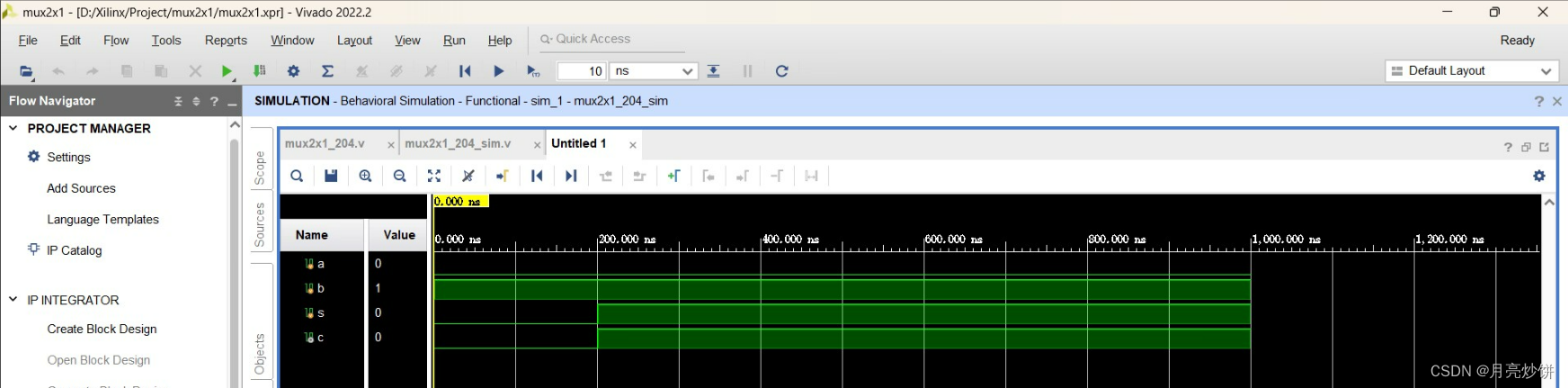

仿真截图3:

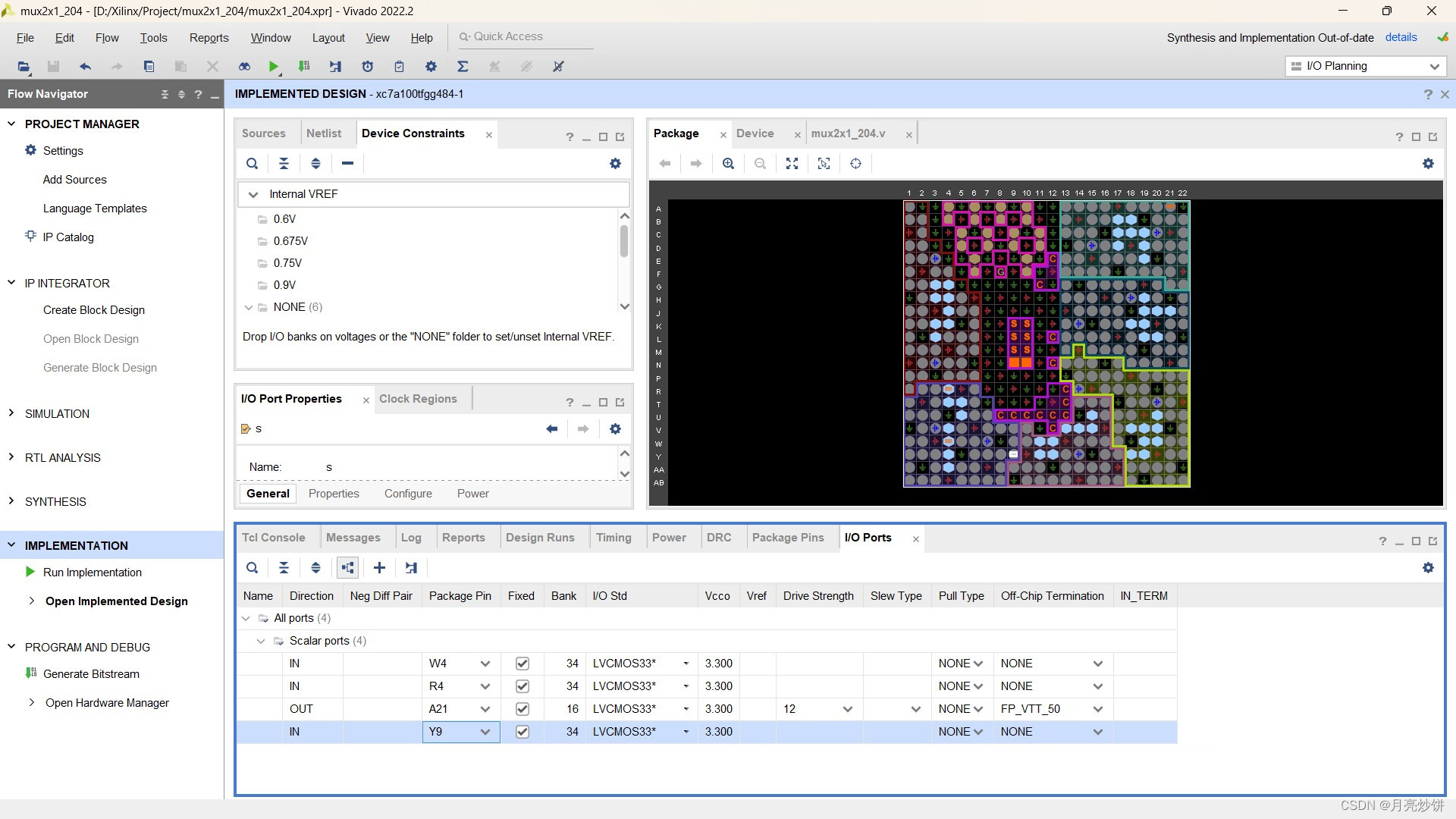

引脚锁定截图3:

源代码4:LS74151_204.v

`timescale 1ns / 1ps

//

module LS74151_204(

input D0,

input D1,

input D2,

input D3,

input D4,

input D5,

input D6,

input D7,

output reg y,

output w,

input A,

input B,

input C,

input S

);

assign w=~y;

always @(*)begin

case({S,C,B,A})

4'b0000: y<=D0;

4'b0001: y<=D1;

4'b0010: y<=D2;

4'b0011: y<=D3;

4'b0100: y<=D4;

4'b0101: y<=D5;

4'b0110: y<=D6;

4'b0111: y<=D7;

default y=0;

endcase

end

endmodule

仿真代码4:LS74151_204_sim.v

`timescale 1ns / 1ps

//

module LS74151_204_sim();

reg D0=0,D1=1,D2=0,D3=1,D4=0,D5=1,D6=0,D7=1;

reg A=1'bx,B=1'bx, C=1'bx, S=1;

reg A=0;

wire y;

wire w;

LS74151_204 u

(.D0(D0),.D1(D1),.D2(D2),.D3(D3),.D4(D4),.D5(D5),.D6(D6),.D7(D7),

.S(S),.A(A),.B(B),.C(C),.y(y),.w(w)

);

initial begin

#50 begin A=0;B=0;C=0;S=0;end;

#50 begin A=1;B=0;C=0;end;

#50 begin A=0;B=1;C=0;end;

#50 begin A=1;B=1;C=0;end;

#50 begin A=0;B=0;C=1;end;

#50 begin A=1;B=0;C=1;end;

#50 begin A=0;B=1;C=1;end;

#50 begin A=1;B=1;C=1;end;

#50 S=1;

end

endmodule

引脚约束4:LS74151_204.xdc

set_property IOSTANDARD LVCMOS33 [get_ports A]

set_property IOSTANDARD LVCMOS33 [get_ports {B}]

set_property IOSTANDARD LVCMOS33 [get_ports {C}]

set_property IOSTANDARD LVCMOS33 [get_ports {D0}]

set_property IOSTANDARD LVCMOS33 [get_ports {D1}]

set_property IOSTANDARD LVCMOS33 [get_ports {D2}]

set_property IOSTANDARD LVCMOS33 [get_ports {D5}]

set_property IOSTANDARD LVCMOS33 [get_ports {w}]

set_property IOSTANDARD LVCMOS33 [get_ports {y}]

set_property IOSTANDARD LVCMOS33 [get_ports {S}]

set_property IOSTANDARD LVCMOS33 [get_ports {D7}]

set_property IOSTANDARD LVCMOS33 [get_ports {D6}]

set_property IOSTANDARD LVCMOS33 [get_ports {D3}]

set_property IOSTANDARD LVCMOS33 [get_ports {D4}]

set_property PACKAGE_PIN Y8 [get_ports {A}]

set_property PACKAGE_PIN Y7 [get_ports {B}]

set_property PACKAGE_PIN W9 [get_ports {C}]

set_property PACKAGE_PIN W4 [get_ports {D0}]

set_property PACKAGE_PIN R4 [get_ports {D1}]

set_property PACKAGE_PIN T4 [get_ports {D2}]

set_property PACKAGE_PIN T5 [get_ports {D3}]

set_property PACKAGE_PIN U5 [get_ports {D4}]

set_property PACKAGE_PIN W6 [get_ports {D5}]

set_property PACKAGE_PIN W5 [get_ports {D6}]

set_property PACKAGE_PIN U6 [get_ports {D7}]

set_property PACKAGE_PIN Y9 [get_ports {S}]

set_property PACKAGE_PIN E22 [get_ports {w}]

set_property PACKAGE_PIN A21 [get_ports {y}]

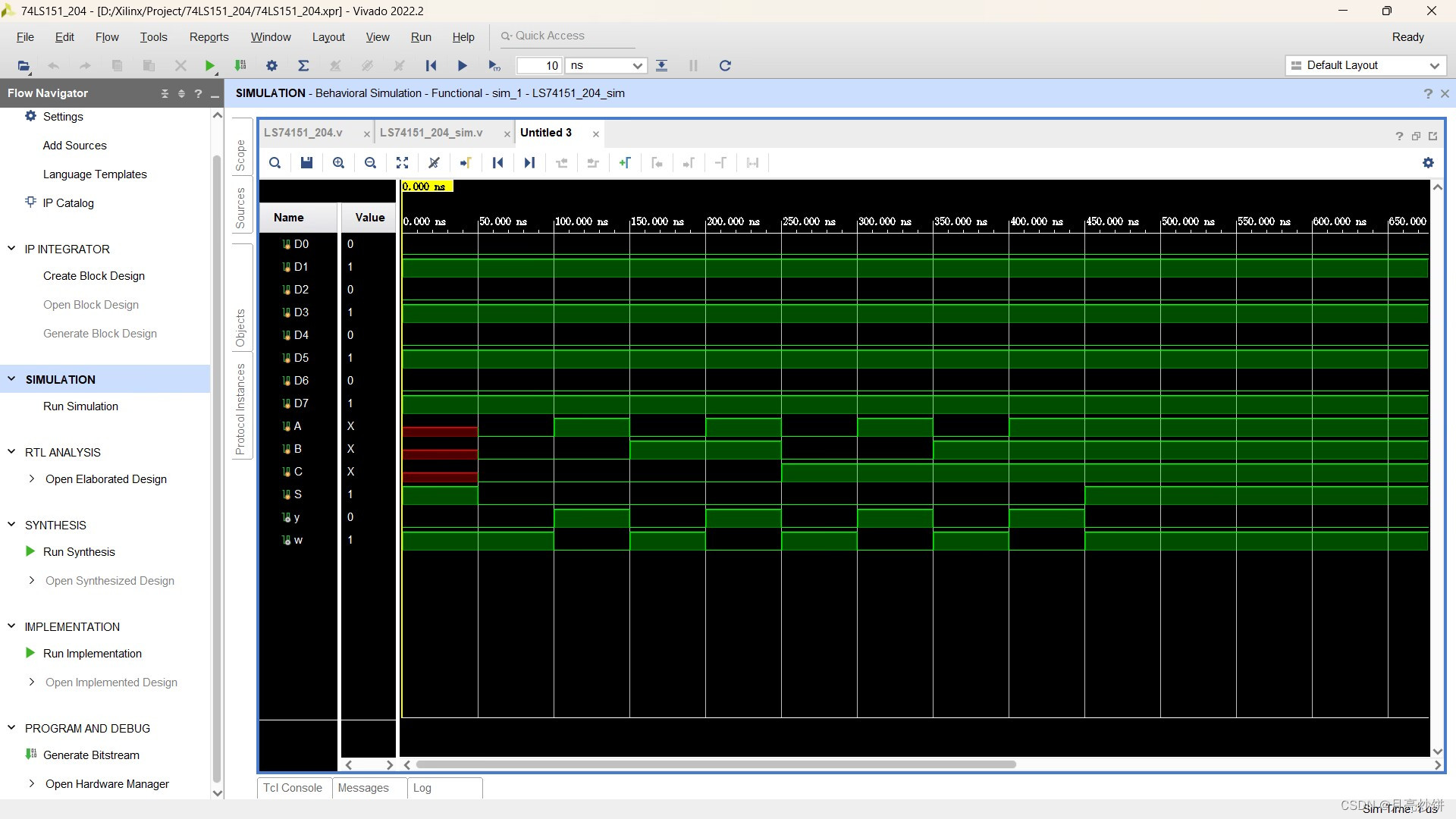

仿真截图4:

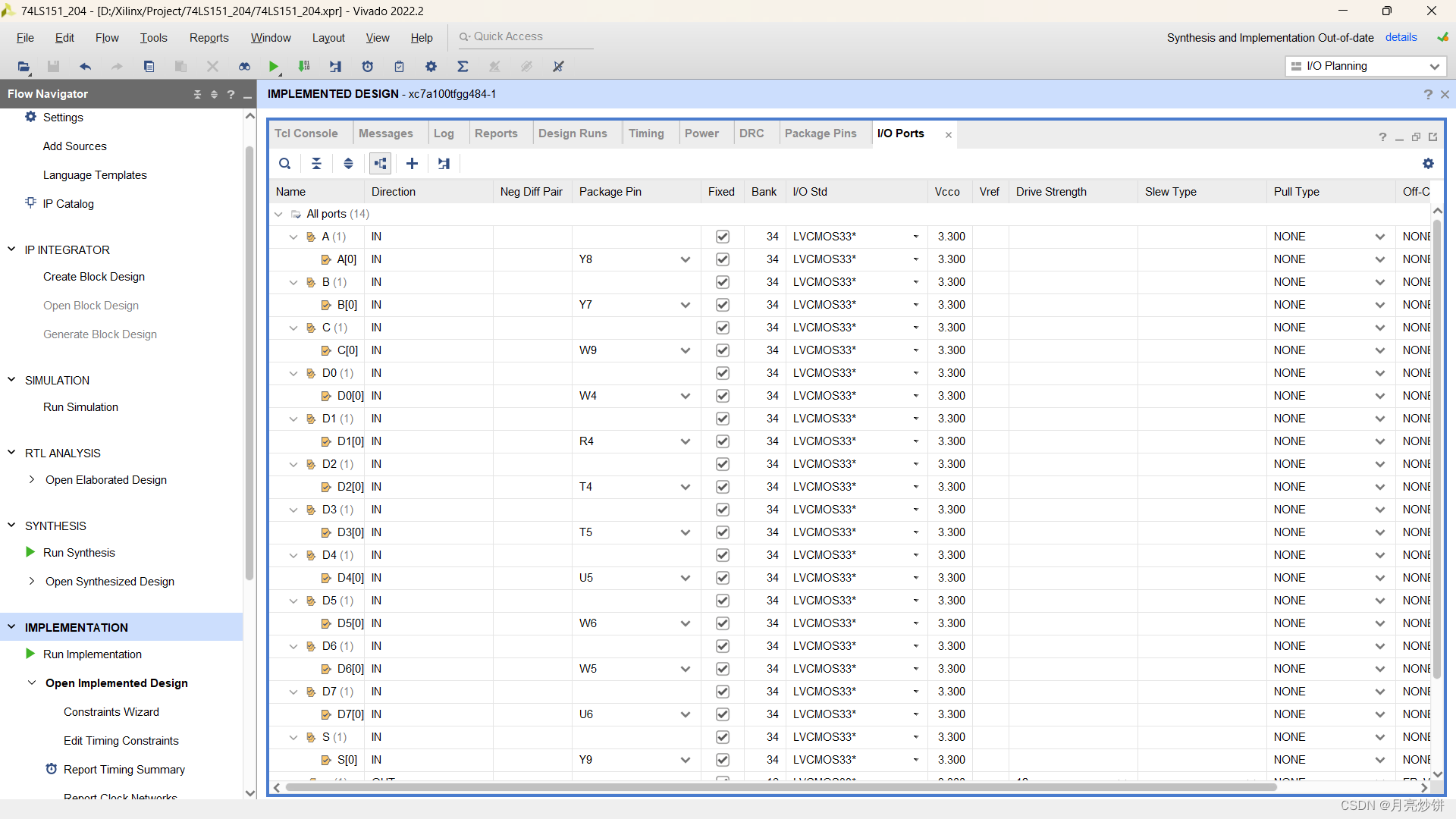

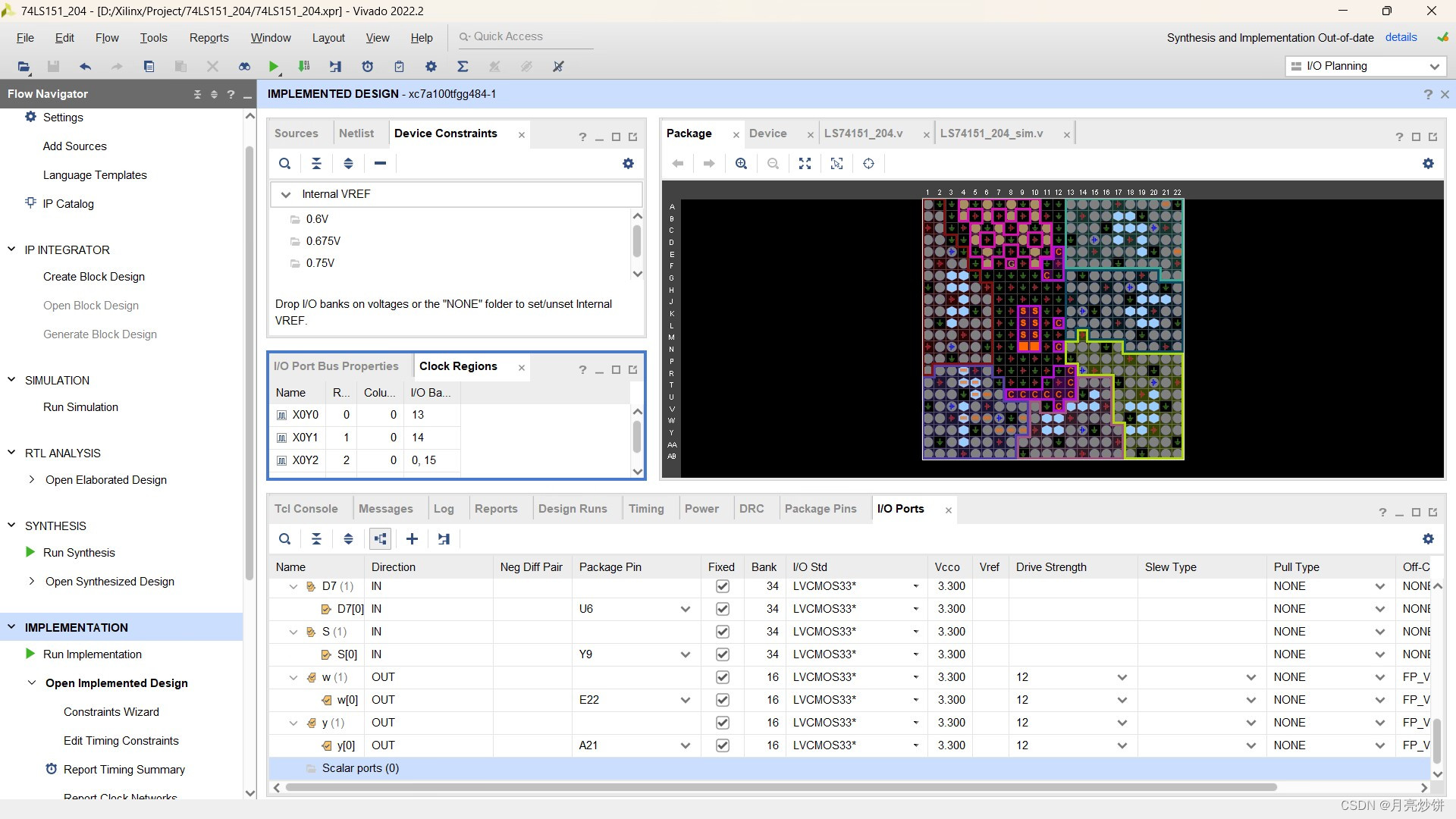

引脚锁定截图4:

四、下板验证结果

(1)封装好各类门IP核可供使用。

(2)依次拨动 SW4、SW0(即 B1、A1)为 00、01、10 和 11,只有当 A1、B1 同时为 1 时,GLD0 熄灭(为 0),其他情况 GLD0 都点亮(为 1),这与与非运算的结果相 一致; 对开关 SW5、SW1,SW6、SW2,SW7、SW3 重复 上述操作,分别观察 GLD1、 GLD2、GLD3 的变化情况。 S7400_v1、S7400_v2 和 S7400_v3 的验证操作和结果与 S7400 是相同的。

(3) 将 SW0 拨上(1)、SW1 拨下(0),将 SW23 拨下(0),GLD0 点亮,说明此时对 应 SW0 的值;将 SW23 拨上(1),GLD0 熄灭,说明此时对应 SW1 的值。

(4)拨动 SW7~0,设置 D7~D0 为 00111001;拨动 SW23 为 0(STROBEN 有效),拨动 SW22~SW20 依次为 000、001、010、011 (依次选择第 0、1、2、3 位)。<GLD1,GLD0>依次输出<0,1>、<1,0>、<0,1> ,这与 S74151 的逻辑功能相符; 拨动 SW23 为 1(STROBEN 无效),重复操作,一直保持 不变。

本文详细介绍了使用Vivado设计与门、74LS00、编码器和选择器等组合逻辑电路的实验过程,包括VerilogHDL编程、仿真测试及下板验证结果,展示了如何创建可配置的IP核并验证其功能。

本文详细介绍了使用Vivado设计与门、74LS00、编码器和选择器等组合逻辑电路的实验过程,包括VerilogHDL编程、仿真测试及下板验证结果,展示了如何创建可配置的IP核并验证其功能。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?