《数字逻辑电路》实验三 组合逻辑电路设计(二)

目录

一、实验目的

通过实验掌握译码器、比较器、编码器和加法器的设计。

二、实验内容

(1)采用Verilog HDL 程序,设计74138译码器并下载测试; (见2.3.1)

(2)采用Verilog HDL程序,设计74682比较器并下载测试; (见2.3.2)

(3)采用Verilog HDL程序,设计一个 8 位的优先编码器 priencoder并下载测试;优先编码器常用于中断 控制器中,将多个到来的中断请求(高电平有效)按照优先级排队,将最高优先级的编码输 出。(见2.3.3)(X0 的优先级最高,X7 优先级最低)

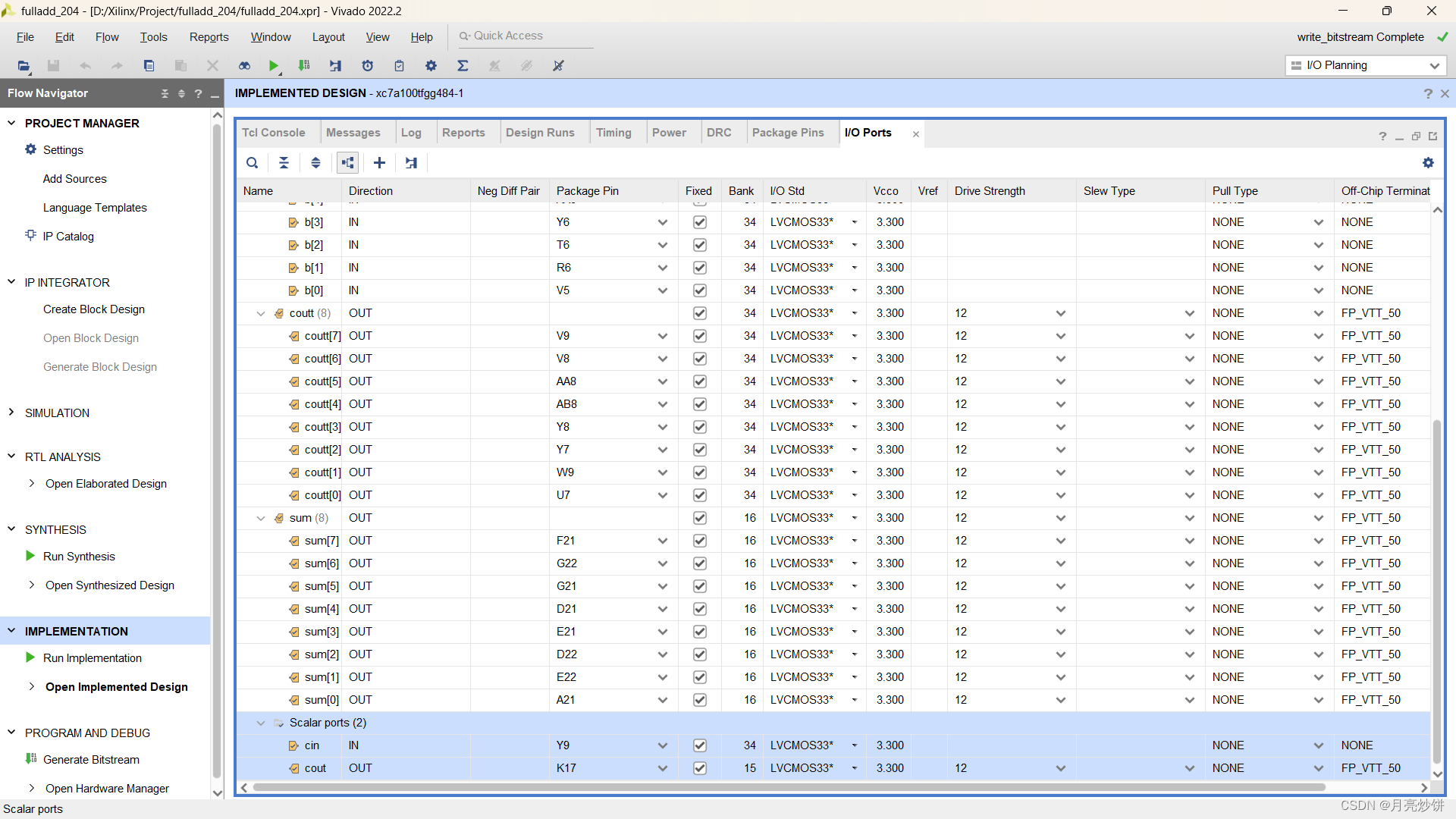

(4)采用Verilog HDL程序,设计8位加法器并下载测试。被加数 a[0]~a[7],加数 b[0]~b[7],低位进位位 cin,结果 sum[0]~sum[7], 高位进位位 cout。 (见2.4.1)

三、代码与截图

源代码1:s74138_204.v

`timescale 1ns / 1ps

//

module s74138_204(

input A,

input B,

input C,

input G1,

input G2AN,

input G2BN,

output reg Y0N,

output reg Y1N,

output reg Y2N,

output reg Y3N,

output reg Y4N,

output reg Y5N,

output reg Y6N,

output reg Y7N

);

wire[2:0] cba,G;

assign cba = {C,B,A};

assign G = {G1,G2AN,G2BN};

initial

begin

Y0N =1;Y1N= 1;Y2N =1;Y3N= 1;Y4N =1;Y5N= 1;Y6N =1;Y7N= 1;

end

always @(*)

begin

case ({cba,G})

6'b000100: begin

Y0N = 0;Y1N= 1;Y2N =1;Y3N= 1;Y4N =1;Y5N= 1;Y6N =1;Y7N= 1;

end

6'b001100: begin

Y1N = 0;Y0N= 1;Y2N =1;Y3N= 1;Y4N =1;Y5N= 1;Y6N =1;Y7N= 1;

end

6'b010100: begin

Y2N = 0;Y1N= 1;Y0N =1;Y3N= 1;Y4N =1;Y5N= 1;Y6N =1;Y7N= 1;

end

6'b011100: begin

Y3N = 0;Y1N= 1;Y2N =1;Y0N= 1;Y4N =1;Y5N= 1;Y6N =1;Y7N= 1;

end

6'b100100: begin

Y4N = 0;Y1N= 1;Y2N =1;Y3N= 1;Y0N =1;Y5N= 1;Y6N =1;Y7N= 1;

end

6'b101100: begin

Y5N = 0;Y1N= 1;Y2N =1;Y3N= 1;Y4N =1;Y0N= 1;Y6N =1;Y7N= 1;

end

6'b110100: begin

Y6N = 0;Y1N= 1;Y2N =1;Y3N= 1;Y4N =1;Y5N= 1;Y0N =1;Y7N= 1;

end

6'b111100: begin

Y7N = 0;Y1N= 1;Y2N =1;Y3N= 1;Y4N =1;Y5N= 1;Y6N =1;Y0N= 1;

end

default: begin Y0N =1;Y1N= 1;Y2N =1;Y3N= 1;Y4N =1;Y5N= 1;Y6N =1;Y7N= 1;end

endcase

end

endmodule

测试代码1:s74138_204_sim.v

`timescale 1ns / 1ps

//

module s74138_204_sim( );

reg A=0,B=0,C=0,G1=0,G2AN=1,G2BN=1;// INPUT

wire Y0N,Y1N,Y2N,Y3N,Y4N,Y5N,Y6N,Y7N;// OUTPUT

s74138_204 U(.A(A),.B(B),.C(C),

.G1(G1),.G2AN(G2AN),.G2BN(G2BN),

.Y0N(Y0N),.Y1N(Y1N),.Y2N(Y2N),.Y3N(Y3N),

.Y4N(Y4N),.Y5N(Y5N),.Y6N(Y6N),.Y7N(Y7N));

initial begin

#10 begin A=0;B=0;C=0;G1=1;G2AN=0;G2BN=1; end;

#10 begin A=0;B=0;C=0;G1=1;G2AN=0;G2BN=1; end;

#10 begin A=0;B=0;C=0;G1=1;G2AN=1;G2BN=0; end;

#10 begin A=0;B=0;C=0;G1=1;G2AN=0;G2BN=0; end;

#10 begin A=1;B=0;C=0;G1=1;G2AN=0;G2BN=0; end;

#10 begin A=0;B=1;C=0;G1=1;G2AN=0;G2BN=0; end;

#10 begin A=1;B=1;C=0;G1=1;G2AN=0;G2BN=0; end;

#10 begin A=0;B=0;C=1;G1=1;G2AN=0;G2BN=0; end;

#10 begin A=1;B=0;C=1;G1=1;G2AN=0;G2BN=0; end;

#10 begin A=0;B=1;C=1;G1=1;G2AN=0;G2BN=0; end;

#10 begin A=1;B=1;C=1;G1=1;G2AN=0;G2BN=0; end;

#10 begin A=0;B=0;C=0;G1=0;G2AN=0;G2BN=0; end;

end;

endmodule引脚约束1:s74138_204.xdc

set_property IOSTANDARD LVCMOS33 [get_ports A]

set_property IOSTANDARD LVCMOS33 [get_ports B]

set_property IOSTANDARD LVCMOS33 [get_ports C]

set_property IOSTANDARD LVCMOS33 [get_ports G1]

set_property IOSTANDARD LVCMOS33 [get_ports G2AN]

set_property IOSTANDARD LVCMOS33 [get_ports G2BN]

set_property IOSTANDARD LVCMOS33 [get_ports Y0N]

set_property IOSTANDARD LVCMOS33 [get_ports Y1N]

set_property IOSTANDARD LVCMOS33 [get_ports Y2N]

set_property IOSTANDARD LVCMOS33 [get_ports Y3N]

set_property IOSTANDARD LVCMOS33 [get_ports Y4N]

set_property IOSTANDARD LVCMOS33 [get_ports Y5N]

set_property IOSTANDARD LVCMOS33 [get_ports Y6N]

set_property IOSTANDARD LVCMOS33 [get_ports Y7N]

set_property PACKAGE_PIN F21 [get_ports Y7N]

set_property PACKAGE_PIN G22 [get_ports Y6N]

set_property PACKAGE_PIN G21 [get_ports Y5N]

set_property PACKAGE_PIN D21 [get_ports Y4N]

set_property PACKAGE_PIN E21 [get_ports Y3N]

set_property PACKAGE_PIN D22 [get_ports Y2N]

set_property PACKAGE_PIN E22 [get_ports Y1N]

set_property PACKAGE_PIN A21 [get_ports Y0N]

set_property PACKAGE_PIN W4 [get_ports A]

set_property PACKAGE_PIN R4 [get_ports B]

set_property PACKAGE_PIN T4 [get_ports C]

set_property PACKAGE_PIN Y9 [get_ports G1]

set_property PACKAGE_PIN W9 [get_ports G2AN]

set_property PACKAGE_PIN Y7 [get_ports G2BN]

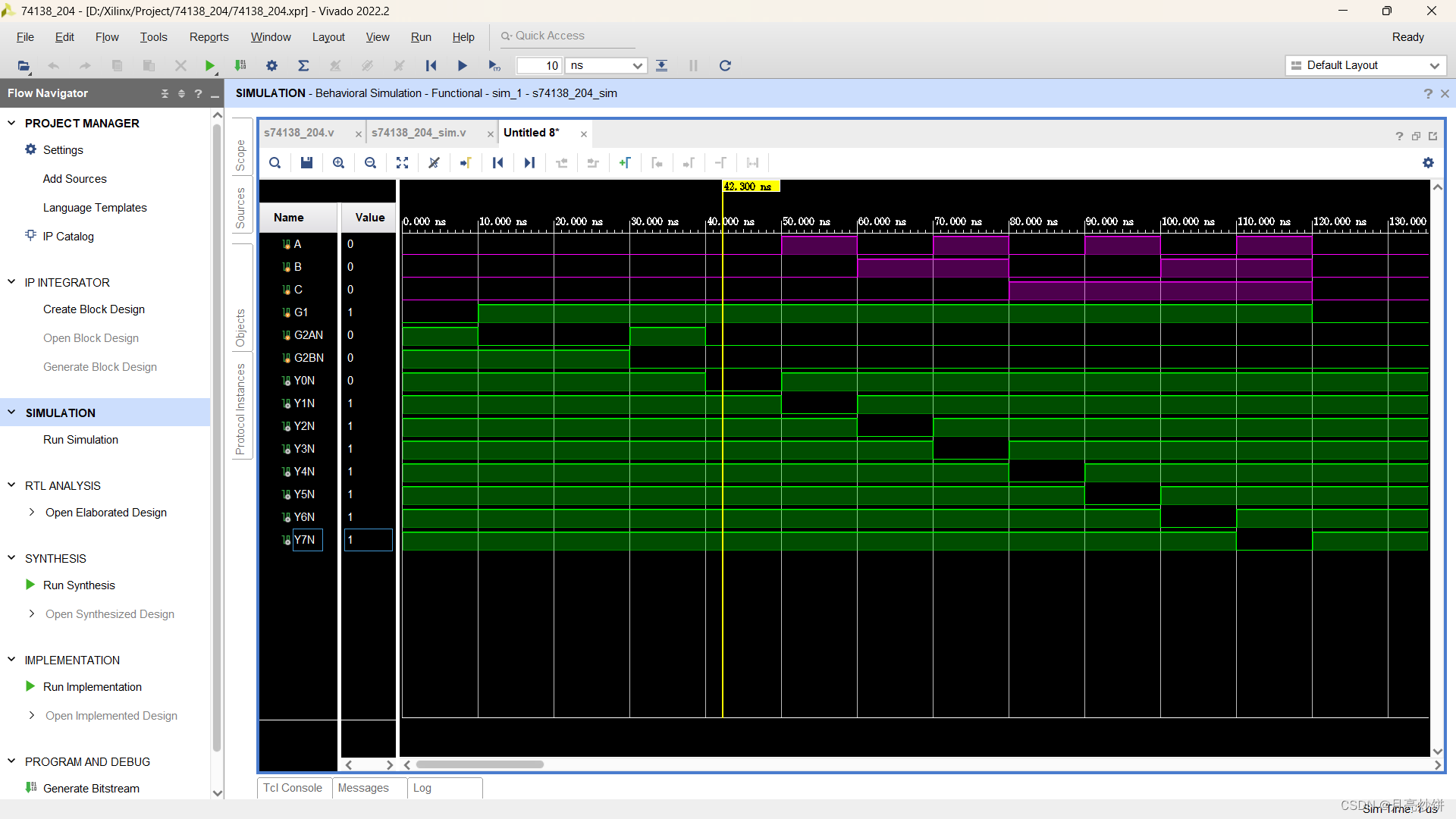

仿真截图1:

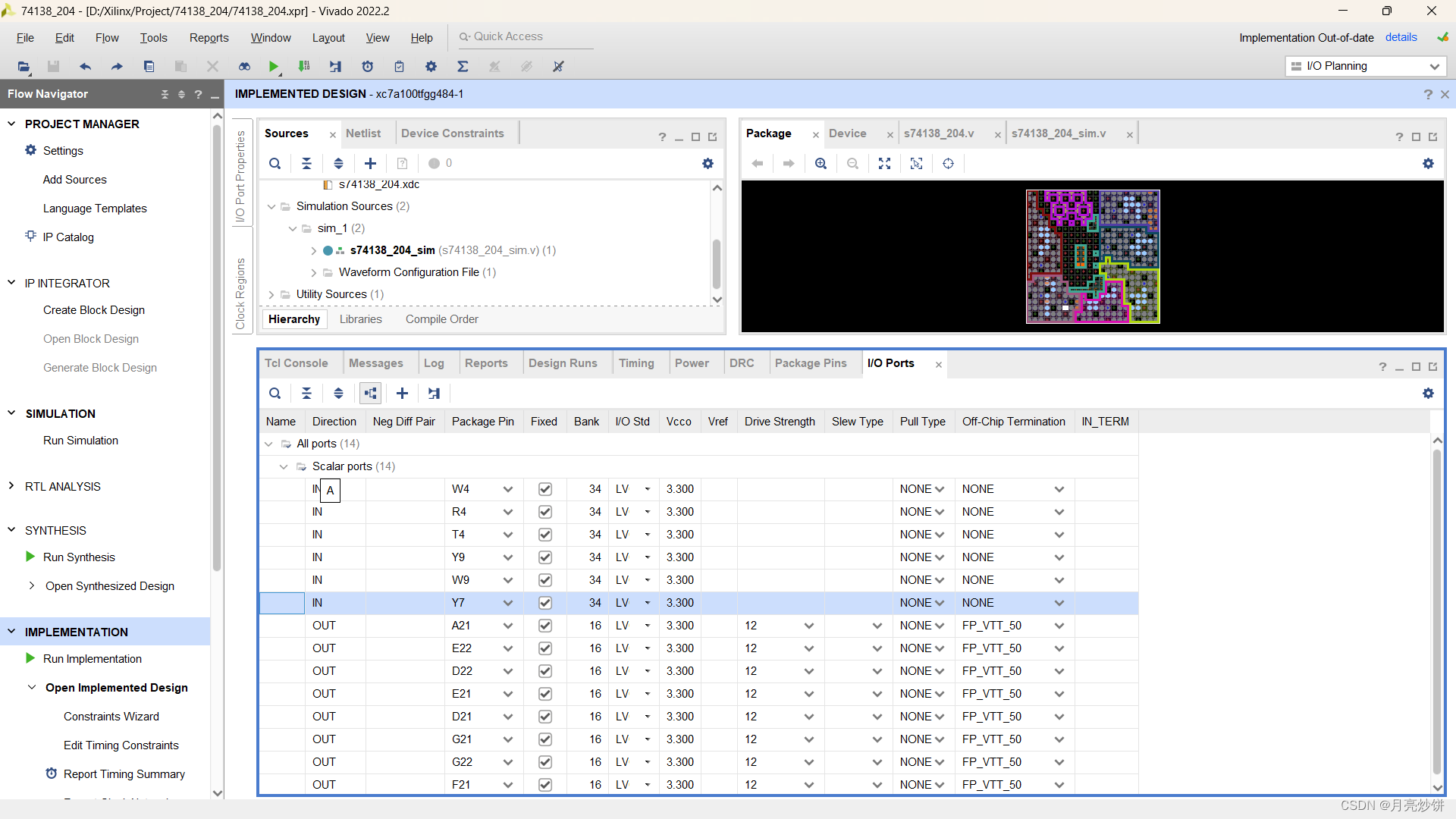

引脚锁定截图:

源代码2:s74682_204.v

`timescale 1ns / 1ps

//

module s74682_204(

input [7:0] p,

input [7:0] q,

output reg peqn,

output reg pgqn

);

always@(p or q)

if(p < q)begin

peqn = 1;

pgqn = 1;

end

else if(p == q)begin

peqn = 0;

pgqn = 1;

end

else begin

peqn = 1;

pgqn = 0;

end

endmodule

测试代码2:s74682_204_sim.v

`timescale 1ns / 1ps

//

module s74682_204_sim();

reg [7:0] p = 8'h0f,q = 8'h0f;

wire peqn,pgqn;

s74682_204 U(.p(p),.q(q),

.peqn(peqn),.pgqn(pgqn));

initial begin

#10 q = 8'h00;

#10 q = 8'hff;

end

endmodule引脚约束2:s74682_204.xdc

set_property IOSTANDARD LVCMOS33 [get_ports peqn]

set_property IOSTANDARD LVCMOS33 [get_ports pgqn]

set_property IOSTANDARD LVCMOS33 [get_ports {q[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {q[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {q[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {q[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {q[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {q[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {q[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {q[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {p[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {p[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {p[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {p[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {p[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {p[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {p[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {p[0]}]

set_property PACKAGE_PIN AB6 [get_ports {q[7]}]

set_property PACKAGE_PIN AB7 [get_ports {q[6]}]

set_property PACKAGE_PIN V7 [get_ports {q[5]}]

set_property PACKAGE_PIN AA6 [get_ports {q[4]}]

set_property PACKAGE_PIN Y6 [get_ports {q[3]}]

set_property PACKAGE_PIN T6 [get_ports {q[2]}]

set_property PACKAGE_PIN R6 [get_ports {q[1]}]

set_property PACKAGE_PIN V5 [get_ports {q[0]}]

set_property PACKAGE_PIN A21 [get_ports peqn]

set_property PACKAGE_PIN E22 [get_ports pgqn]

set_property PACKAGE_PIN W4 [get_ports {p[0]}]

set_property PACKAGE_PIN R4 [get_ports {p[1]}]

set_property PACKAGE_PIN T4 [get_ports {p[2]}]

set_property PACKAGE_PIN T5 [get_ports {p[3]}]

set_property PACKAGE_PIN U5 [get_ports {p[4]}]

set_property PACKAGE_PIN W6 [get_ports {p[5]}]

set_property PACKAGE_PIN W5 [get_ports {p[6]}]

set_property PACKAGE_PIN U6 [get_ports {p[7]}]

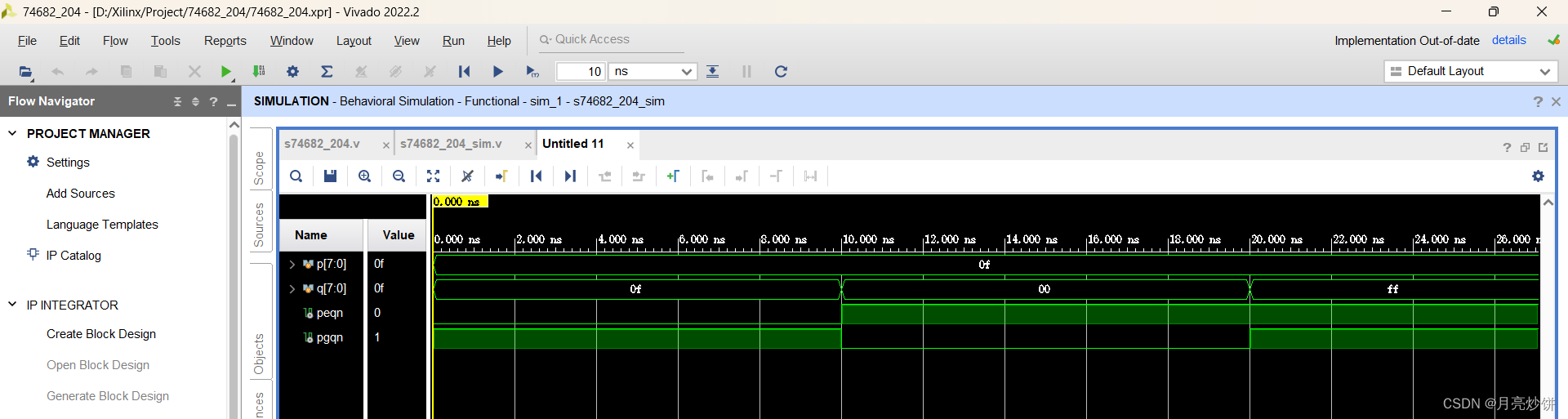

仿真截图2:

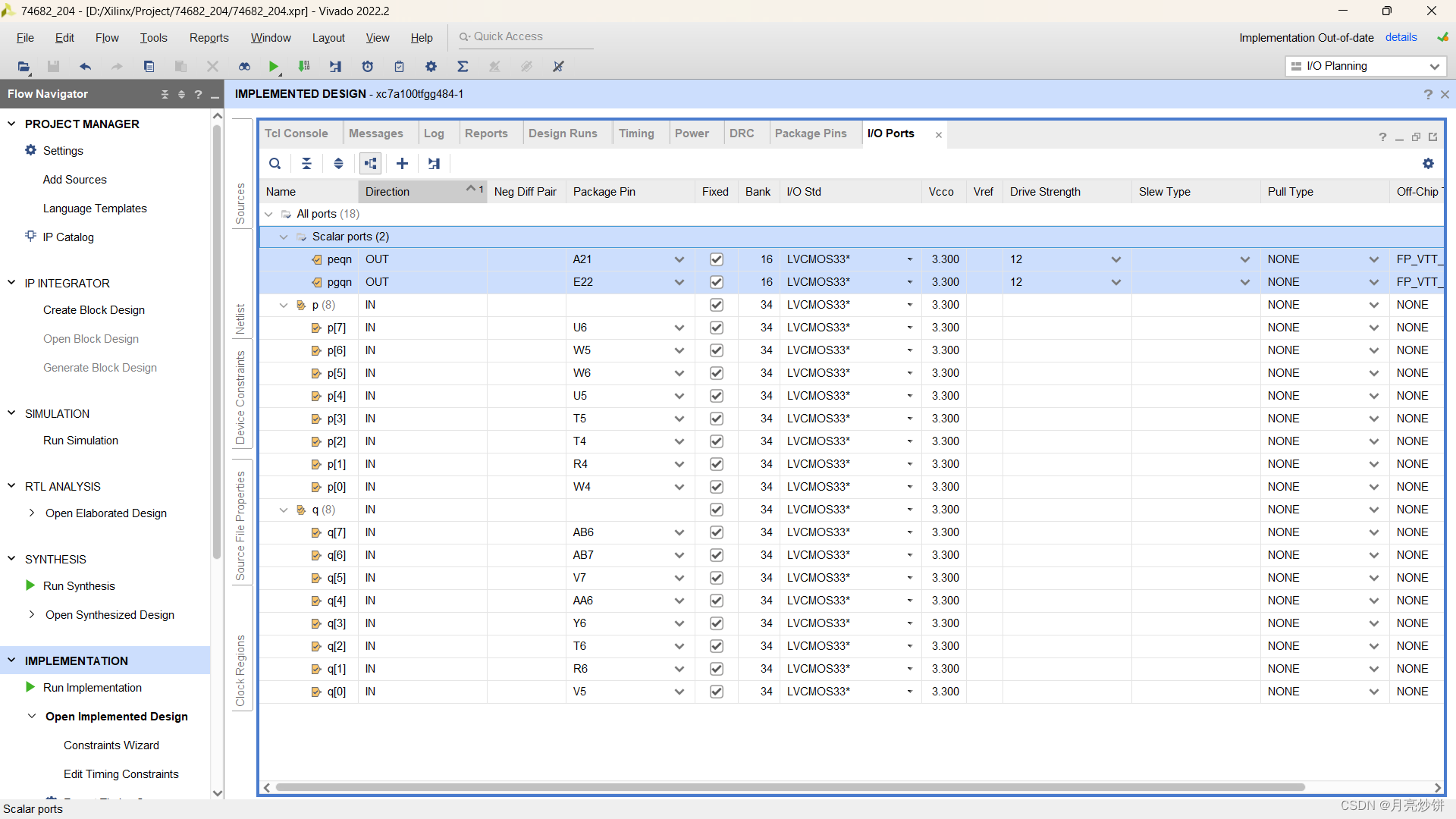

引脚锁定截图2:

源代码3:priencoder_204.v

`timescale 1ns / 1ps

//

module priencoder_204(

input [7:0] x,

output reg [2:0] y//,

);

always@(*)

begin

if(x[0]) //第一优先

y=3'b000;

else if(x[1])

y=3'b001;

else if(x[2])

y=3'b010;

else if(x[3])

y=3'b011;

else if(x[4])

y=3'b100;

else if(x[5])

y=3'b101;

else if(x[6])

y=3'b110;

else if(x[7])

y=3'b111;

else //I的每一位都为0,输出无效

y=3'b111;//高电平输出无效

end

endmodule仿真代码3:priencoder_204_sim.v

`timescale 1ns / 1ps

//

module priencoder_204_sim( );

reg [7:0] x = 8'b00101101;

wire[2:0] y;

priencoder_204 U(.x(x),.y(y));

initial begin

#20 x = 8'b01110010;

#20 x = 8'b11100100;

#20 x = 8'b11001000;

#20 x = 8'b01010000;

#20 x = 8'b10100000;

#20 x = 8'b11000000;

#20 x = 8'b10000000;

#20 x = 8'b11111111;

end;

endmodule

引脚约束3:priencoder_204.xdc

set_property IOSTANDARD LVCMOS33 [get_ports {x[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {x[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {x[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {x[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {x[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {x[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {x[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {x[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {y[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {y[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {y[0]}]

set_property PACKAGE_PIN D22 [get_ports {y[2]}]

set_property PACKAGE_PIN E22 [get_ports {y[1]}]

set_property PACKAGE_PIN A21 [get_ports {y[0]}]

set_property PACKAGE_PIN U6 [get_ports {x[7]}]

set_property PACKAGE_PIN W5 [get_ports {x[6]}]

set_property PACKAGE_PIN W6 [get_ports {x[5]}]

set_property PACKAGE_PIN U5 [get_ports {x[4]}]

set_property PACKAGE_PIN T5 [get_ports {x[3]}]

set_property PACKAGE_PIN T4 [get_ports {x[2]}]

set_property PACKAGE_PIN R4 [get_ports {x[1]}]

set_property PACKAGE_PIN W4 [get_ports {x[0]}]

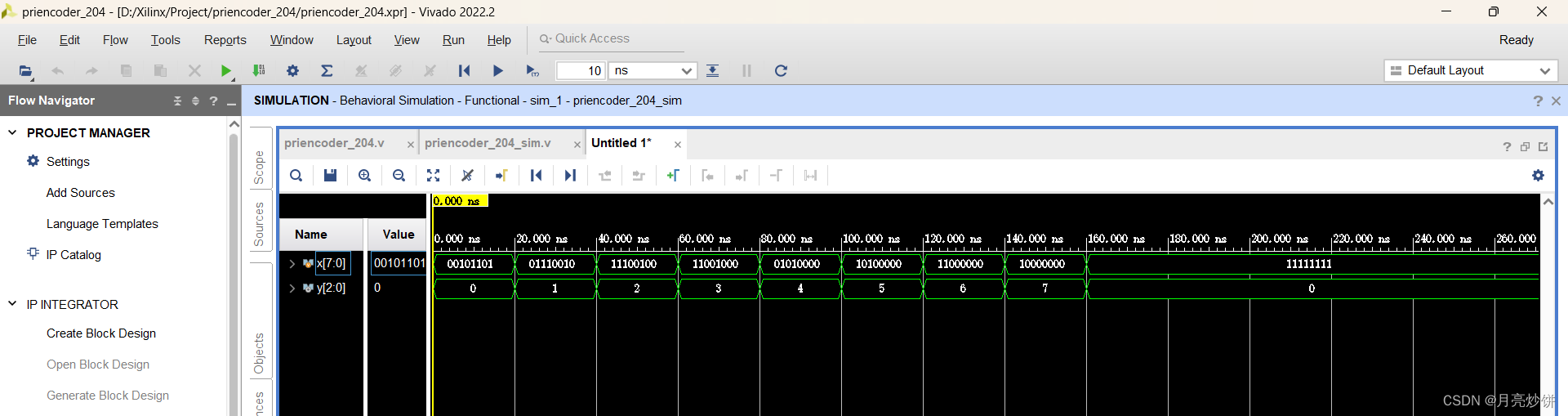

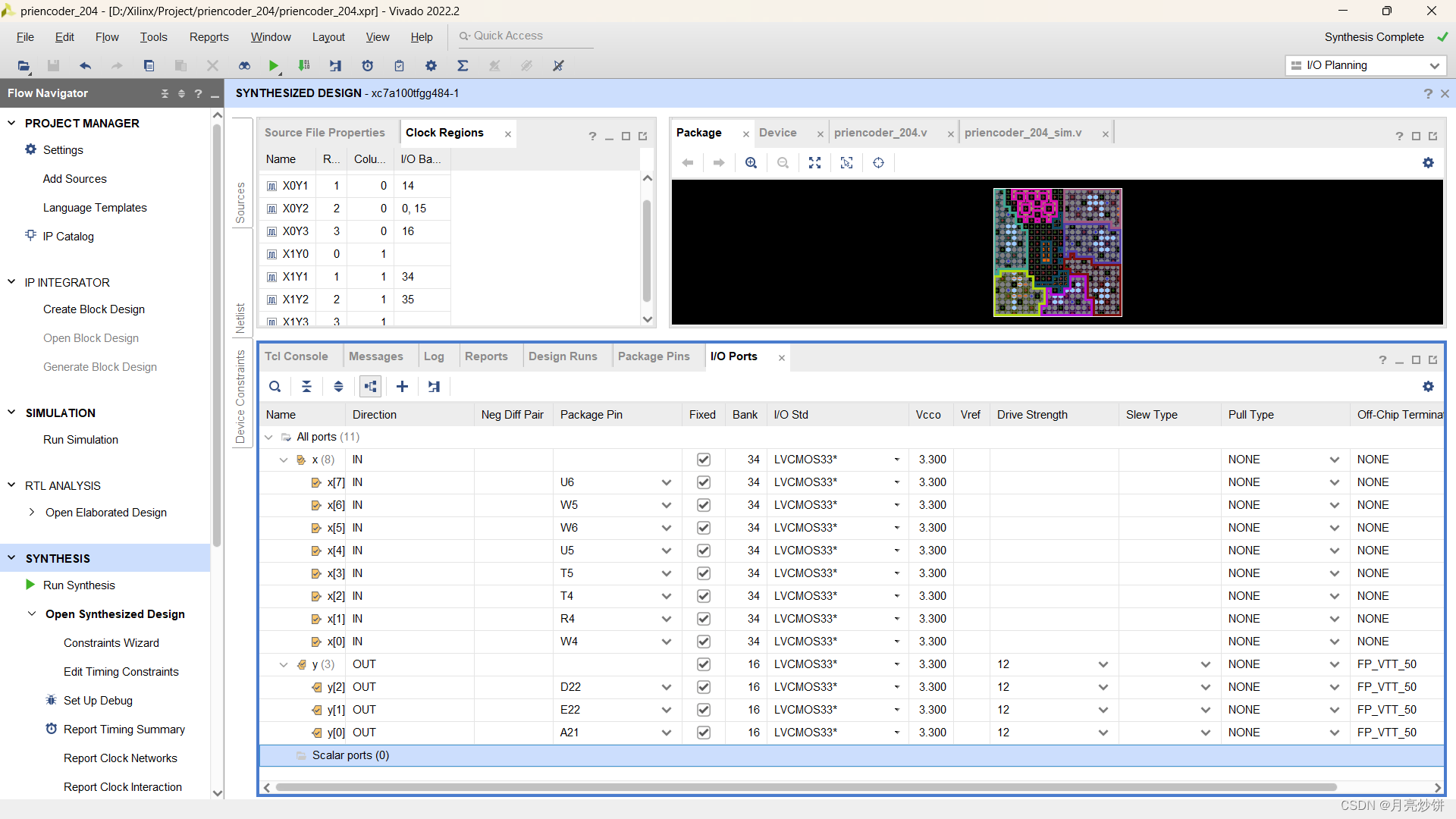

仿真截图3:

引脚锁定截图3:

源代码4:fulladd8_204.v

`timescale 1ns / 1ps

//

module fulladd_1_204(

input a,b,cin,//输入信号,ain表示被加数,bin表示加数,cin表示低位向高位的进位

output reg sum,cout//输出信号,cout表示向高位的进位,sum表示本位的相加和

);

reg s1,s2,s3;

always @(a or b or cin) begin

sum=(a^b)^cin;//本位和输出表达式

s1=a&cin;

s2=b&cin;

s3=a&b;

cout=(s1|s2)|s3;//高位进位输出表达式

end

endmodule

module fulladd_8_204(

input [7:0] a, //被加数

input [7:0] b, //加数

input cin, //低位进位

output [7:0] sum,

output cout,

wire [7:0] coutt

);

fulladd_1_204 f0(a[0],b[0],cin,sum[0],coutt[0]);

fulladd_1_204 f1(a[1],b[1],coutt[0],sum[1],coutt[1]);

fulladd_1_204 f2(a[2],b[2],coutt[1],sum[2],coutt[2]);

fulladd_1_204 f3(a[3],b[3],coutt[2],sum[3],coutt[3]);

fulladd_1_204 f4(a[4],b[4],coutt[3],sum[4],coutt[4]);

fulladd_1_204 f5(a[5],b[5],coutt[4],sum[5],coutt[5]);

fulladd_1_204 f6(a[6],b[6],coutt[5],sum[6],coutt[6]);

fulladd_1_204 f7(a[7],b[7],coutt[6],sum[7],coutt[7]);

assign cout=coutt[7];

endmodule仿真代码4:fulladd8_204_sim.v

`timescale 1ns / 1ps

//

module fulladd8_204_sim();

reg [7:0] a = 8'd7,b = 8'd6;

reg cin= 0; //必须为 0 S

wire [7:0] sum;

wire [7:0] coutt;

wire cout;

fulladd_8_204 U(.a(a),.b(b),.cin(cin),

.coutt(coutt),.sum(sum),.cout(cout));

initial begin

#20 begin a = 8'd255;b = 8'd1;end

#20 begin a = 8'd128;b = 8'd28;end

end

endmodule

引脚约束4:fulladd8_204.xdc

set_property IOSTANDARD LVCMOS33 [get_ports {a[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {a[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {a[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {a[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {a[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {a[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {a[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {a[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {b[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {b[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {b[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {b[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {b[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {b[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {b[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {b[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports cout]

set_property IOSTANDARD LVCMOS33 [get_ports {sum[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sum[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sum[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sum[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sum[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sum[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sum[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sum[0]}]

set_property PACKAGE_PIN U6 [get_ports {a[7]}]

set_property PACKAGE_PIN W5 [get_ports {a[6]}]

set_property PACKAGE_PIN W6 [get_ports {a[5]}]

set_property PACKAGE_PIN U5 [get_ports {a[4]}]

set_property PACKAGE_PIN T5 [get_ports {a[3]}]

set_property PACKAGE_PIN T4 [get_ports {a[2]}]

set_property PACKAGE_PIN R4 [get_ports {a[1]}]

set_property PACKAGE_PIN W4 [get_ports {a[0]}]

set_property PACKAGE_PIN AB6 [get_ports {b[7]}]

set_property PACKAGE_PIN AB7 [get_ports {b[6]}]

set_property PACKAGE_PIN V7 [get_ports {b[5]}]

set_property PACKAGE_PIN AA6 [get_ports {b[4]}]

set_property PACKAGE_PIN Y6 [get_ports {b[3]}]

set_property PACKAGE_PIN T6 [get_ports {b[2]}]

set_property PACKAGE_PIN R6 [get_ports {b[1]}]

set_property PACKAGE_PIN V5 [get_ports {b[0]}]

set_property PACKAGE_PIN F21 [get_ports {sum[7]}]

set_property PACKAGE_PIN G22 [get_ports {sum[6]}]

set_property PACKAGE_PIN G21 [get_ports {sum[5]}]

set_property PACKAGE_PIN D21 [get_ports {sum[4]}]

set_property PACKAGE_PIN E21 [get_ports {sum[3]}]

set_property PACKAGE_PIN D22 [get_ports {sum[2]}]

set_property PACKAGE_PIN E22 [get_ports {sum[1]}]

set_property PACKAGE_PIN A21 [get_ports {sum[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {coutt[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {coutt[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {coutt[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {coutt[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {coutt[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {coutt[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {coutt[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {coutt[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports cin]

set_property PACKAGE_PIN Y9 [get_ports cin]

set_property PACKAGE_PIN K17 [get_ports cout]

set_property PACKAGE_PIN V9 [get_ports {coutt[7]}]

set_property PACKAGE_PIN V8 [get_ports {coutt[6]}]

set_property PACKAGE_PIN AA8 [get_ports {coutt[5]}]

set_property PACKAGE_PIN AB8 [get_ports {coutt[4]}]

set_property PACKAGE_PIN Y8 [get_ports {coutt[3]}]

set_property PACKAGE_PIN Y7 [get_ports {coutt[2]}]

set_property PACKAGE_PIN W9 [get_ports {coutt[1]}]

set_property PACKAGE_PIN U7 [get_ports {coutt[0]}]

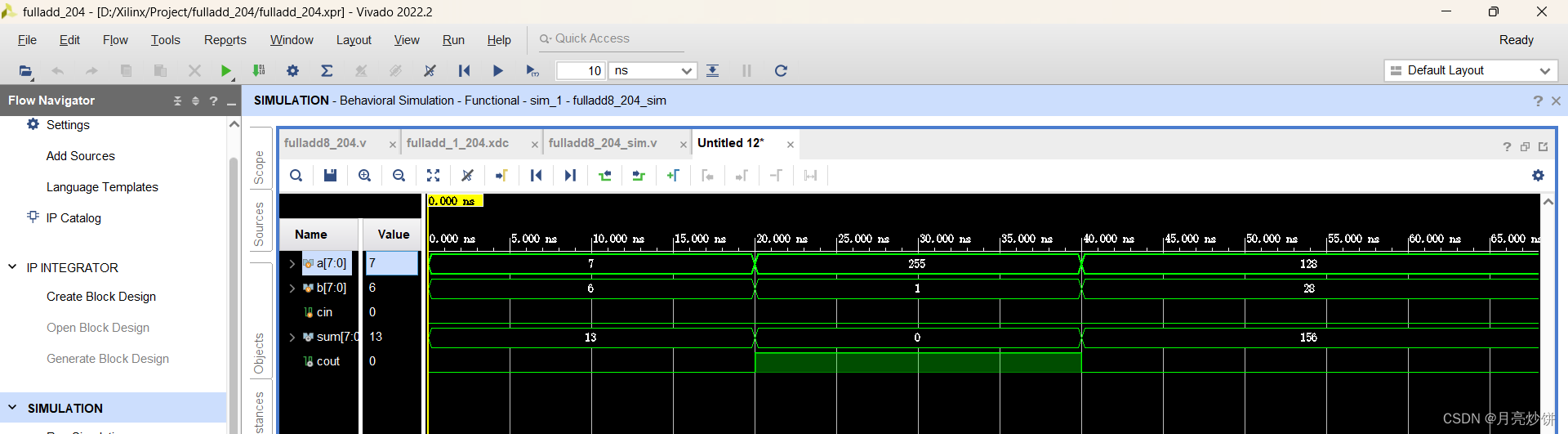

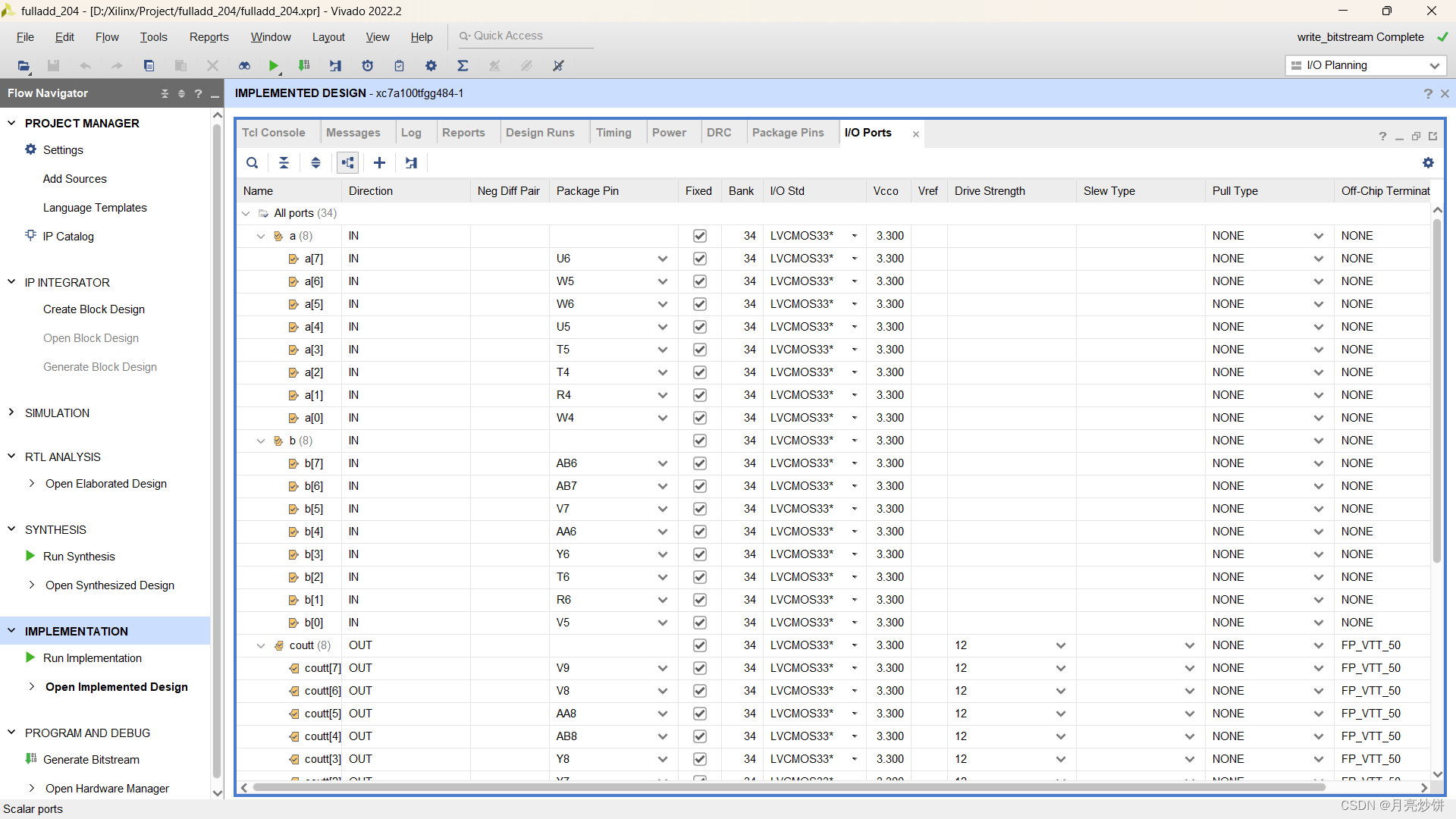

仿真截图4:

引脚锁定截图4:

四、下板验证结果

(1)1) 拨动 SW23 为 1。依次拨动 SW2~0 为 100、101、110、111。对应地,GLD7~0 的输 出依次为 11101111、11011111、10111111、01111111;

2) 拨动 SW23 为 0,重复 1)中操作,该过程中 GLD7~0 保持为 11111111;

3) 拨动 SW23~21 为 110,重复 1)中操作,该过程中 GLD7~0 保持为 11111111;

4) 拨动 SW2321 为 101,重复 1)中操作,该过程中 GLD7~0 保持为 11111111。

(2)1) 拨动 SW15~8 为 00001111(即 q=15);

2) 拨动 SW7~0 为 00001111(即 p=15),=10,说明 p 与 q 相等;

3) 拨动 SW7~0 为 00010101(即 p=21),=01,说明 p 大于 q;

4) 拨动 SW7~0 为 00001010(即 p=10),=11,说明 p 小于 q。

(3) 1) 拨动 SW3 为 1,其余开关均为 0,GLD2~0 输出为 011;

2) 随意拨动 SW7~4,GLD2~0 输出为 011 保持为 011 不变,说明 X7~4 的优先级比 X3 低,当 X3 请求有效时会被屏蔽;

3) 拨动 SW2 为 1,GLD2~0 输出为 010,说明 X3 被优先级更高的 X2 请求屏蔽。

(4)1) 拨动 SW23 为 0。拨动 SW15~8 为 00001110(14),拨动 SW7~0 为 00001011(11), GLD7~0 变为 00011001(即和为 25);

2) 拨动 SW23 为 1,GLD7~0 变为 00011010(即和为 26)。

4330

4330

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?