**

实验内容(一)

**

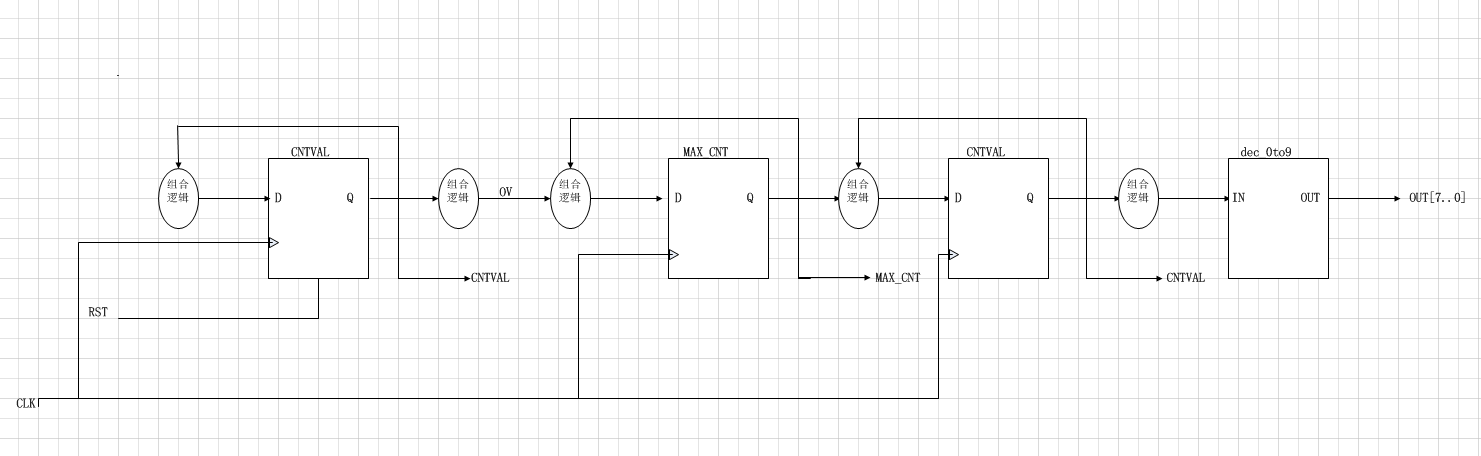

1.手工绘制的RTL结构图:

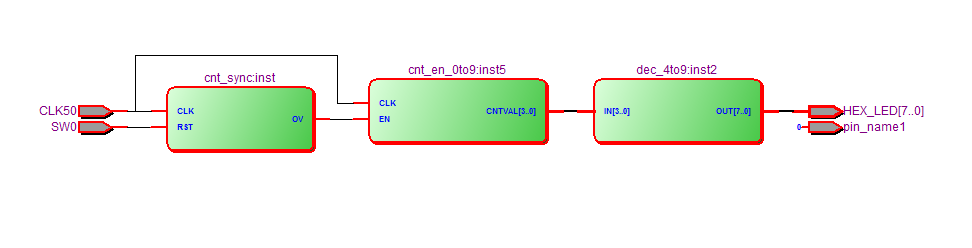

2.Quartus生成的RTL

实验原理:

整个计数器一共有3个模块组成:

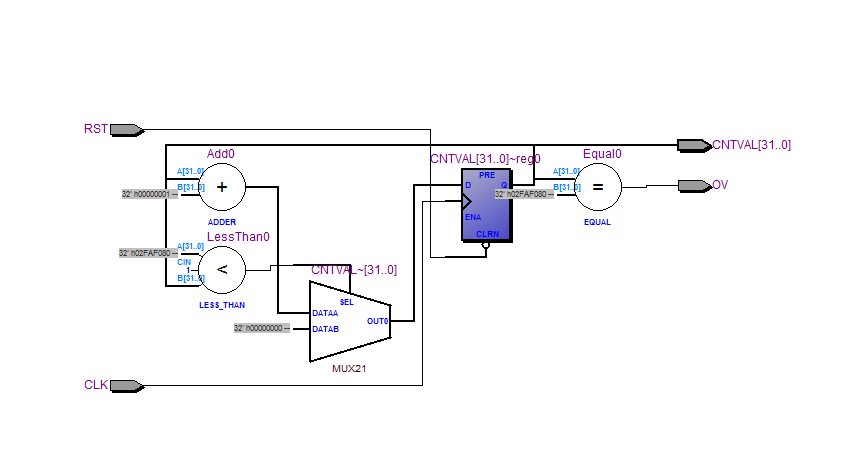

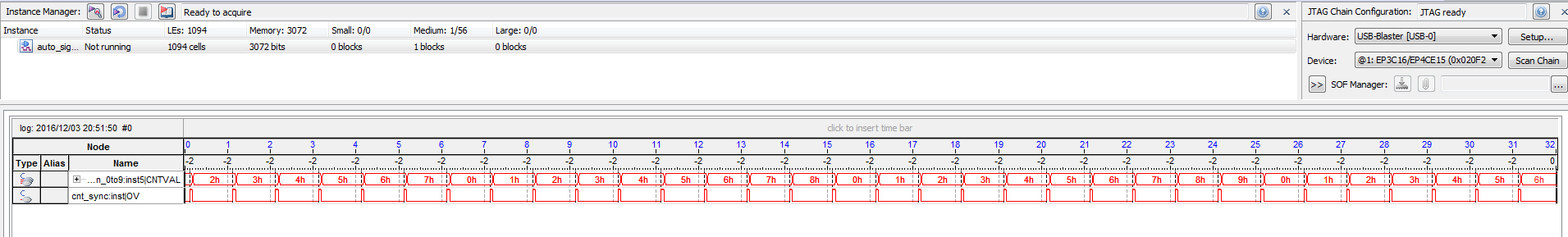

(1)第一模块为生成基准信号的cnt_sync模块,为使计数数值变化的时间间隔是1秒 ,所以定义一个常数MAX_VAL为50000000,当计数器的计数值等于这个常数时,OV溢出1,从而产生1s的时间间隔;

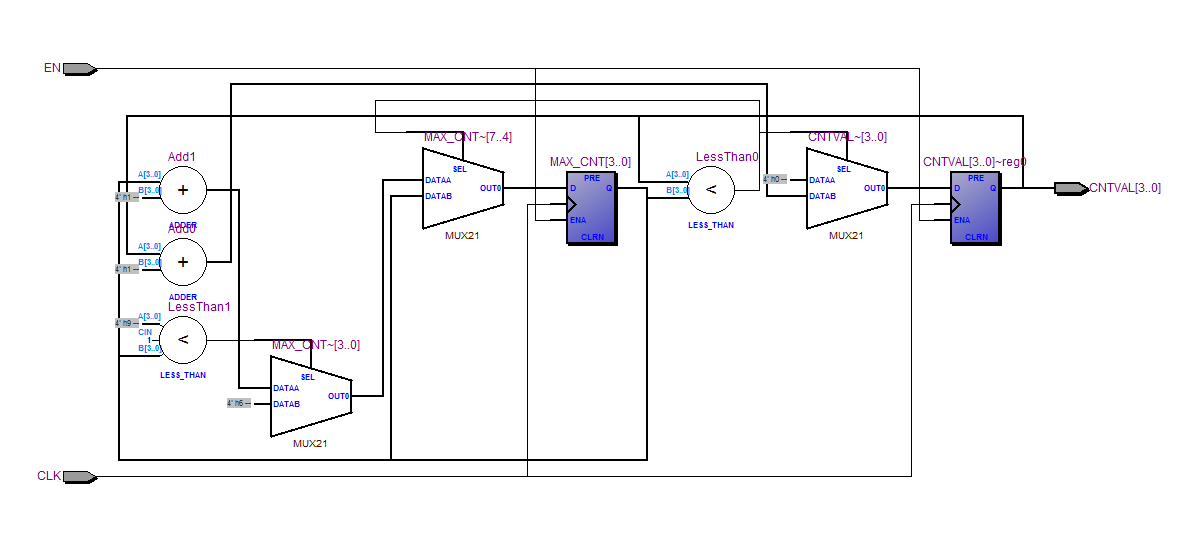

(2)第二模块为cnt_en_0to9带使能的计数器模块,当使能信号EN有效时,此模块开启,计数器开始从

0 1 … 6 0 1… 7 0 1 … 8 0 1 … 9 0 1 … 6 …… 开始循环计数;

(3)第三模块为dec_4to9的译码器模块,让译码器的输入端连接上一级计数器的输出端,根据8段数码管的编码原理进行编码,从而点亮LED数码管。

以下分别为不同RTL的展开图:

(1)cnt_sync生成基准信号模块

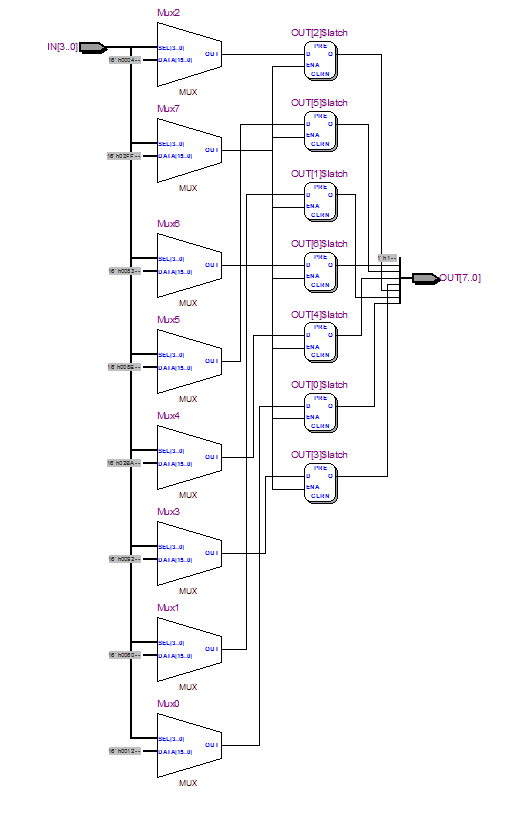

(2)cnt_en_0to9带使能的计数模块

(3)dec_4to9模块

3.SignalTap截图

4.代码片模块

/

//生成基准信号模块

module cnt_sync(

CLK,//时钟,上升沿有效

RST,//异步复位,低电平有效

CNTVAL,//输出的计数值信号

OV);//计数溢出信号,计数值为最大值时该信号为1

//电路编译参数,最大计数值

parameter MAX_VAL=50_000_000;

input CLK;

input RST;

output [32-1:0] CNTVAL;

output OV;

reg [32-1:0] CNTVAL;

reg OV;

always @ (posedge CLK or negedge RST)

begin

if(!RST)

CNTVAL <= 0;

else begin

if(CNTVAL >= MAX_VAL)

CNTVAL <= 0;

else

CNTVAL <= CNTVAL +1’b1;

end

end

always @ (CNTVAL)

begin

if(CNTVAL == MAX_VAL)

OV = 1’b1;

else

OV = 1’b0;

end

endmodule

//

//cnt_rst带有使能的计数器模块

module cnt_en_0to9(

CLK,//时钟,上升沿有效

EN,//输入的计数使能,高有效

CNTVAL);//输出的计数值信号

input CLK;

input EN;

output [3:0] CNTVAL;

reg [3:0] CNTVAL;

reg [3:0] MAX_CNT=6;

always @ (posedge CLK)

begin

if(EN) begin//使能信号开启,执行计数功能

if(CNTVAL < MAX_CNT)

CNTVAL <= CNTVAL +1’b1;

else begin

CNTVAL <= 0;//计数到最大值,下一计数值清零

MAX_CNT <= MAX_CNT + 1’b1;

if(MAX_CNT >= 9)

MAX_CNT <= 6;

end

end

else begin

CNTVAL <= CNTVAL ;//当使能信号无效时,计数值保持不变

end

end

endmodule

///

//译码器模块

module dec_4to9( //数码管的输出最大为0-9

IN,//译码器的输入

OUT);//译码器的输出

input [3:0] IN;

output [7:0] OUT;

reg [7:0] OUT;//有8段数码管

always @ (IN)

begin

case(IN)

4’h0: OUT= 8’hc0;

4’h1: OUT= 8’hf9;

4’h2: OUT= 8’ha4;

4’h3: OUT= 8’hb0;

4’h4: OUT= 8’h99;

4’h5: OUT= 8’h92;

4’h6: OUT= 8’h82;

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7380

7380

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?