(一)概述

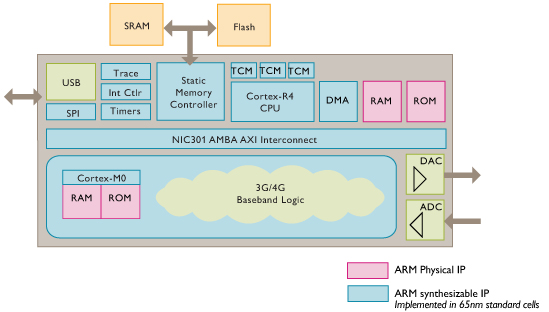

基带数字处理功能以及手机基本外围功能都集中到单片片上系统(SOC)中,其基本构架都采用了微处理器+数字信号处理器(DSP)的结构,微处理器和DSP的处理能力一直增强。微处理器是整颗芯片的控制中心,会运行一个实时嵌入式操作系统(如Nucleus PLUS)。DSP子系统是基带处理的重点,其中包含了许多硬件加速器和基带专用处理模块,完成所有物理层功能。现在,随着实时数字信号处理技术的发展,ARM微处理器(会采用不同的微系列,如3G芯片多采用ARM9)、DSP和FPGA体系结构成为移动终端芯片实现的主要方式。下图是典型的基于ARM架构的基带芯片的逻辑架构,其中3G/4G Baseband Logic指的是DSP运算子系统。

图1 典型ARM架构上的基带芯片框架

微处理器通过实时操作系统RTOS(如Nucleus PLUS)完成多任务的调度、任务间通信、外设驱动以及微处理器与DSP子系统及其他模块的通信等等。功能还包括:

1,对整个移动台进行控制和管理,包括定时控制、数字系统控制、射频控制、省电控制等。

本文介绍了移动终端基带芯片的基本架构,包括微处理器+DSP的结构,以及传统ARM基带芯片和多模基带芯片的设计框架。ARM处理器运行实时操作系统负责控制管理,DSP子系统处理物理层算法。双端口SRAM用于ARM与DSP的数据交互。随着技术发展,多模基带芯片在一颗芯片上支持多种移动网络和无线网络制式,增加了设计和通信管理的复杂性。

本文介绍了移动终端基带芯片的基本架构,包括微处理器+DSP的结构,以及传统ARM基带芯片和多模基带芯片的设计框架。ARM处理器运行实时操作系统负责控制管理,DSP子系统处理物理层算法。双端口SRAM用于ARM与DSP的数据交互。随着技术发展,多模基带芯片在一颗芯片上支持多种移动网络和无线网络制式,增加了设计和通信管理的复杂性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2315

2315

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?