平时原理图设计过程中,FPGA和CPLD换PIN是一件在刀尖上跳舞的细活,换PIN务必保证准确无误;博文主要包括两部分:

第一部分:BANK直连换PIN;

第二部分:不同页面的PIN之间的串阻网络调整

第一部分:BANK直连换PIN;

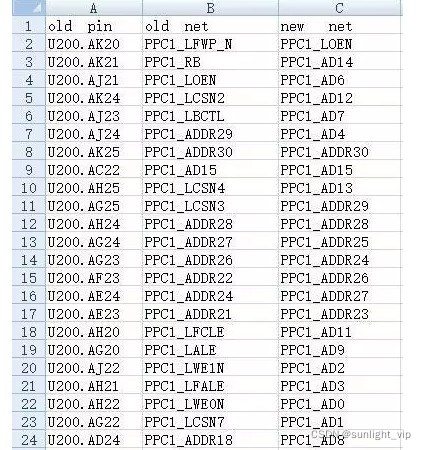

1.LAYOUT工程师会提供一份换PIN表格,格式如下图:

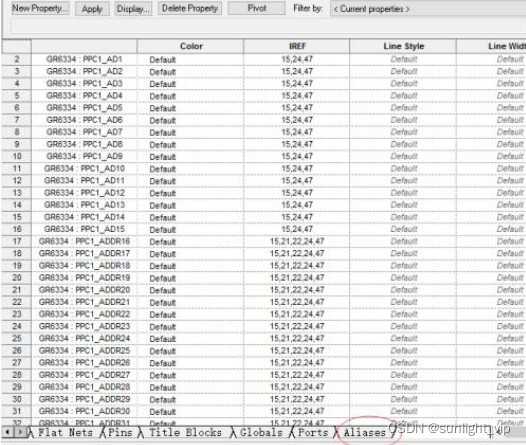

2. 打开原理图,找到换pin list文件里FPGA BANK对应的网络。这里可以把FPGA的每个BANK里的网络与BANK一一对应起来,

注意只选中网络右击选择edit properties;进入property edit界面后,在下方选择“Aliases”,进入Aliases页面

3. 在换PIN表格里面新建一页命名为对应的BANKX;选择将“Name”列全部复制到新的excel里面的对应BANKx里面;可以直接把对应BANK里面的所有网络按照下面方式全部拷贝出来放在第一列:

本文详细介绍了FPGA和CPLD在原理图设计中如何安全有效地进行PIN更换,包括BANK直连换PIN步骤和不同页面PIN间的串阻网络调整方法。通过LAYOUT工程师提供的换PIN表格,使用Excel的VLOOKUP函数配合原理图编辑器进行PIN替换,并针对串阻调整提供了具体操作流程,确保设计的准确性。

本文详细介绍了FPGA和CPLD在原理图设计中如何安全有效地进行PIN更换,包括BANK直连换PIN步骤和不同页面PIN间的串阻网络调整方法。通过LAYOUT工程师提供的换PIN表格,使用Excel的VLOOKUP函数配合原理图编辑器进行PIN替换,并针对串阻调整提供了具体操作流程,确保设计的准确性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

430

430

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?