0.FPGA SelectIO 引言

xilinx 7系列FPGA的SelectIO。所谓SelectIO,就是I/O接口以及I/O逻辑的总称;说到I/O,咱们必须先提到FPGA的BANK。在7系列的FPGA中,BANK分为HR(High-range)BANK和HP(High-performance) BANK。

1.HP BANK只能支持小于等于1.8V电平标准的I/O信号,HP BANK专为高速I/O信号设计,支持DCI(数控阻抗);

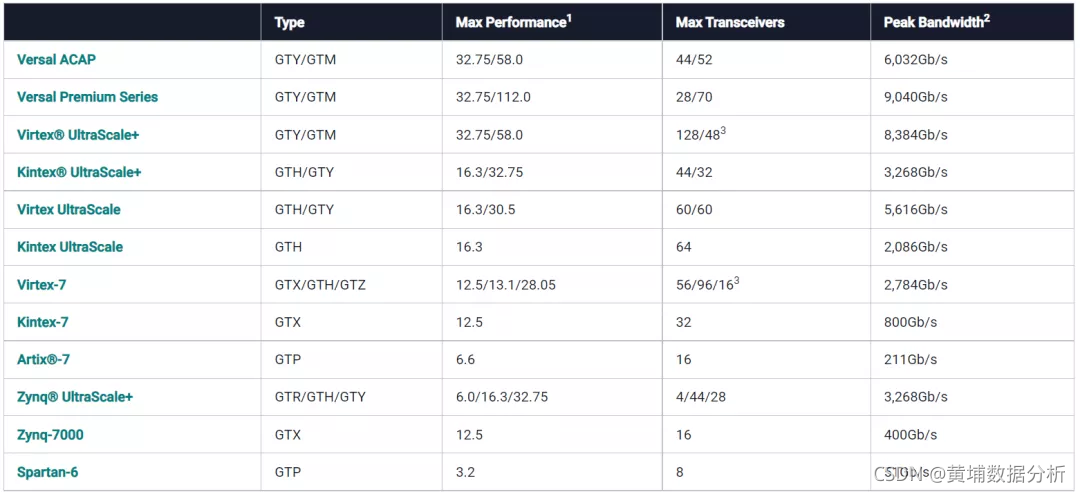

HP BANK涉及的高速I/O接口类型:GTX、GTH、GTY、GTP、GTZ、GTM;

他们都是高速收发器,只是传输速率不同,速率大小为:

GTP < GPX < GTH < GTZ < GTY < GTM

不同芯片上使用的高速收发器也不同,而且同样是GTX,不同系列芯片上的速率也可能不同。

比如7系列的FPGA,GTP最高可以达到6.6Gb/s,GTX最高12.5Gb/s,GTH最高13.1Gb/s,GTZ最高28.05Gb/s

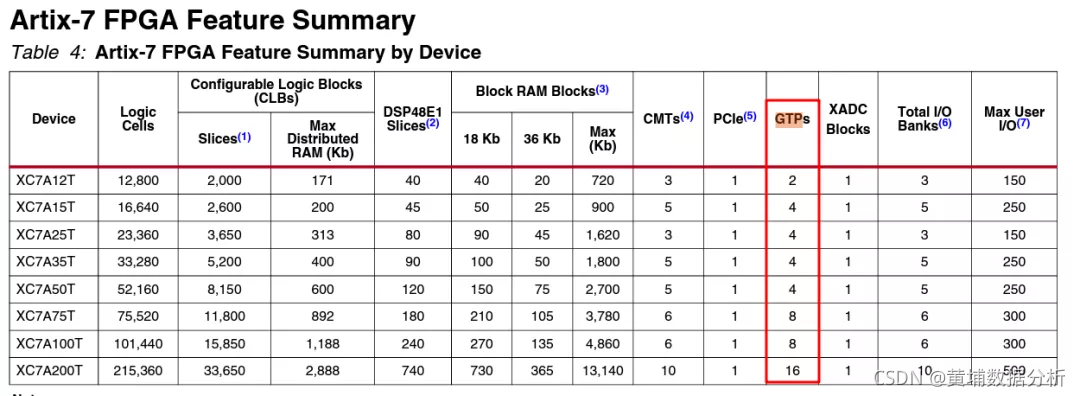

在A7系列上面使用的高速收发器是GTP:

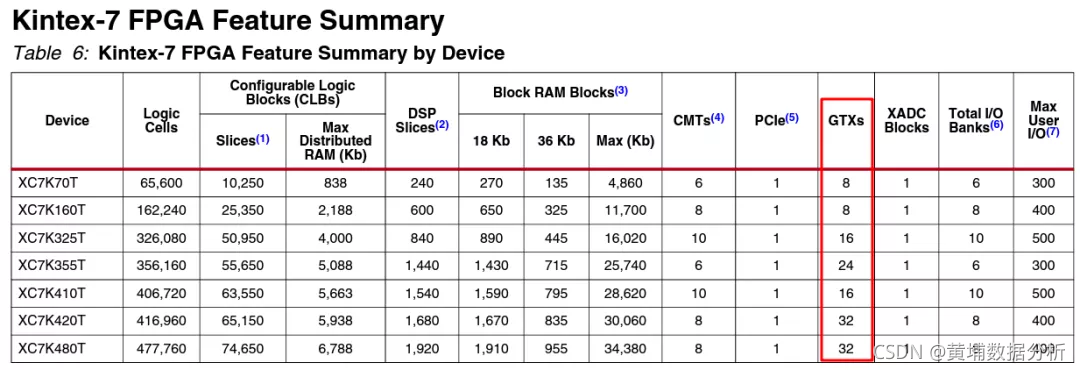

在K7系列上面使用的高速收发器是GTX:

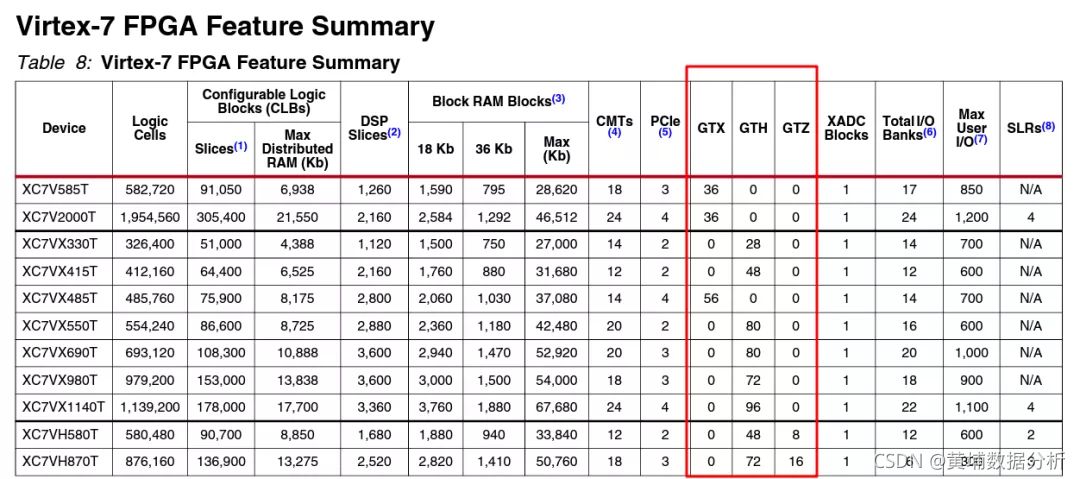

V7系列上面则是GTX/GTH/GTZ都有使用,而且只有在高端的芯片上才使用了GTZ。

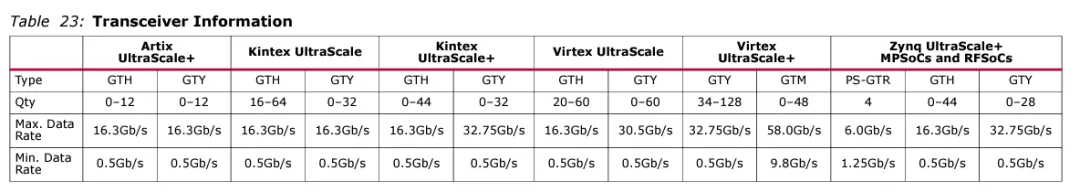

UltraScale和UltraScale+的FPGA,高速收发器使用情况如下表,速度最低的也是GTH,高端的Virtex UltraScale+中使用了GTM

Versal ACAP系列的芯片,使用的也是高端的GTY和GTM

下面的表总结了各系列FPGA的高速收发器的类型和性能。

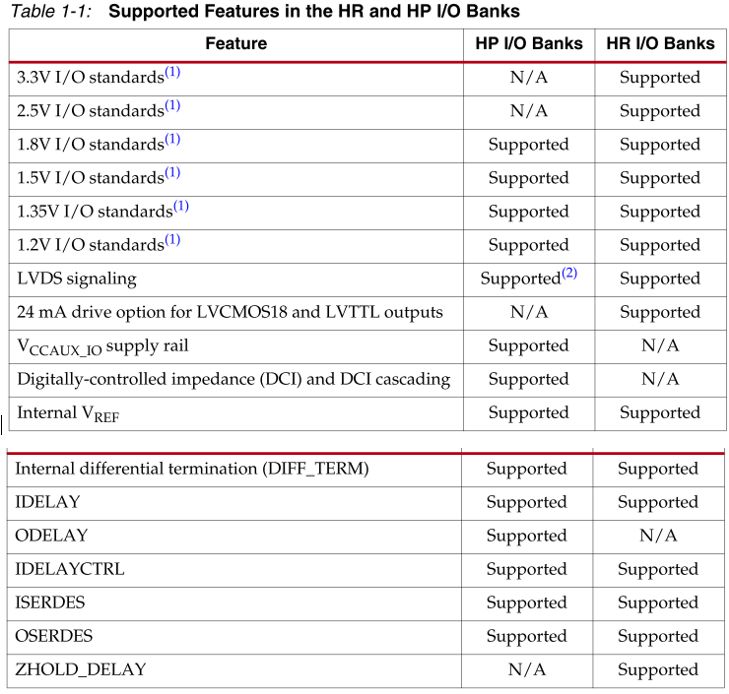

2.HR BANK则支持小于等于3.3V电平标准的I/O信号,而HR BANK则适合更大众化的所有I/O信号设计。下表列出了HP BANK 和HR BANK的特性。

无论是HR或者HP BNANK,每个BANK都包含50个I/O管脚,每个I/O管脚都可配置成输入、输出。每个BANK的首尾管脚只能作为单端I/O,其余48个I/O则可配置成24对差分I/O。

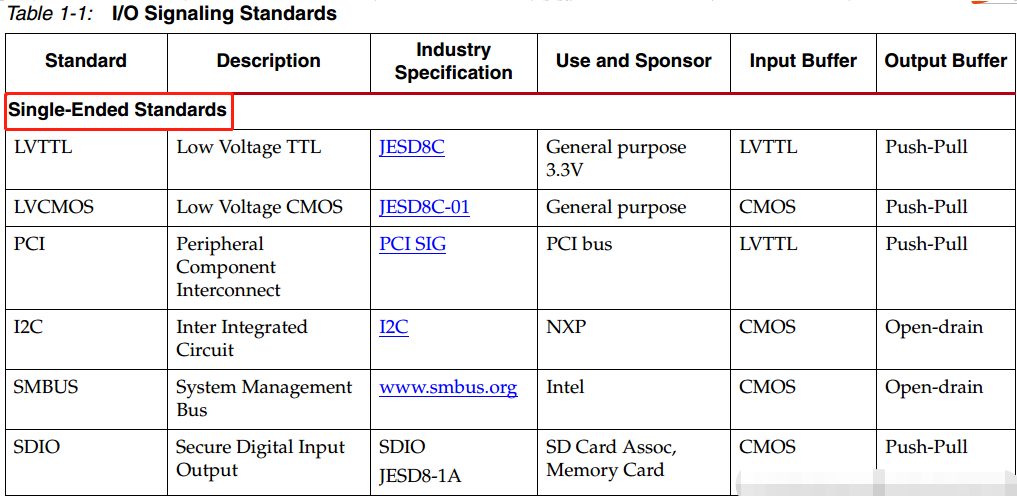

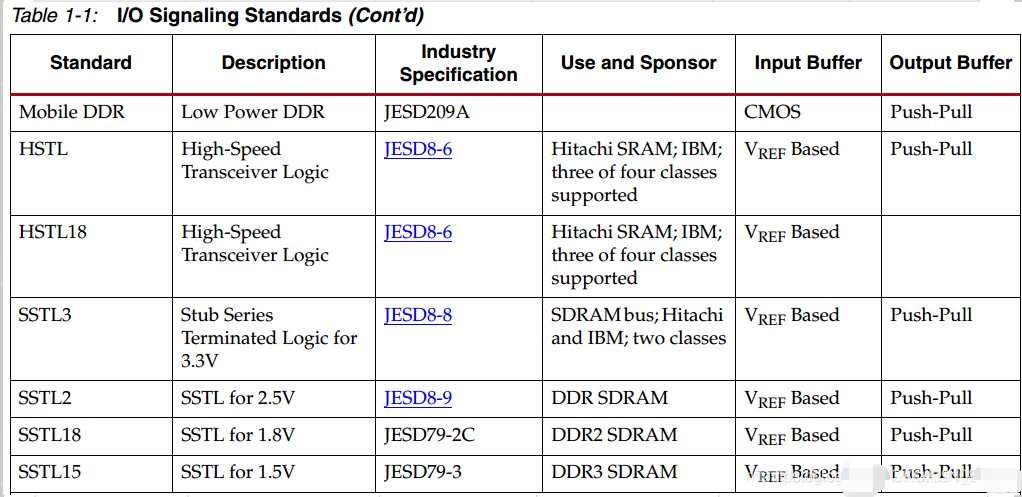

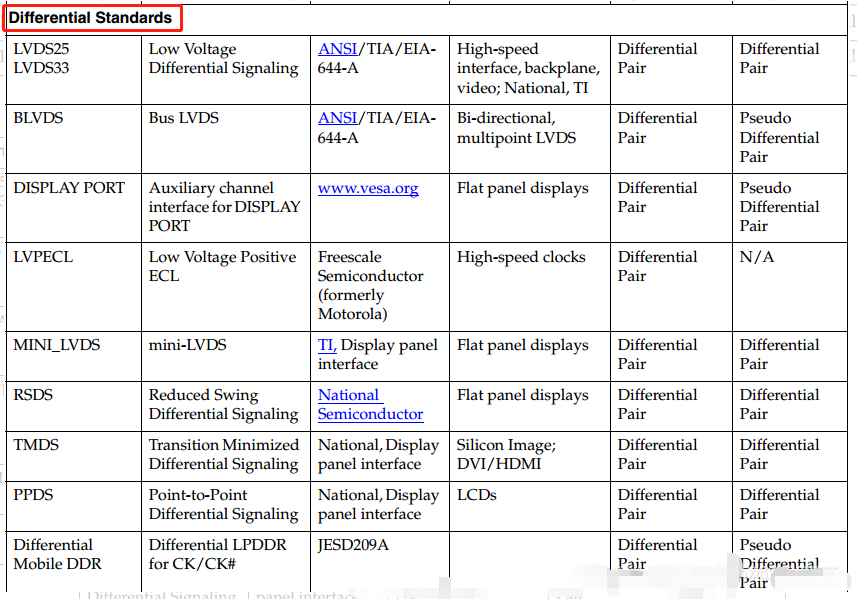

单端的I/O管脚支持LVTTL、LVCMOS、HSTL、PCI等等常用的电平标准。差分的I/O管脚则支持LVDS、差分HSTL等差分信号

1.FPGA 常见IO接口配置

Xilinx FPGA提供和支持高性能、可配置、多样化的接口标准。

I/O主要的可配置属性如下:

1.1 I/O std: 电平标准

常见IO接口可分为单端IO接口和差分IO接口,详细的IO标准参见下图1,表1

图1:IO接口标准

Xilinx SelectIO:个人整理_u924512005的博客-CSDN博客_selectio

具体与FPGA管脚(单端、差分)的连接应用可参考该篇博客;

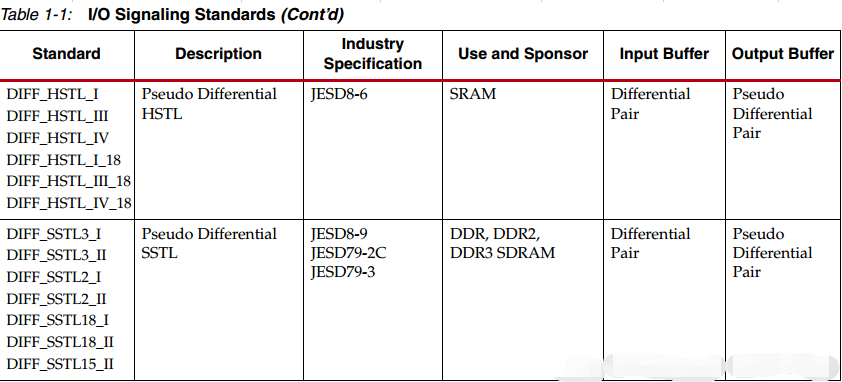

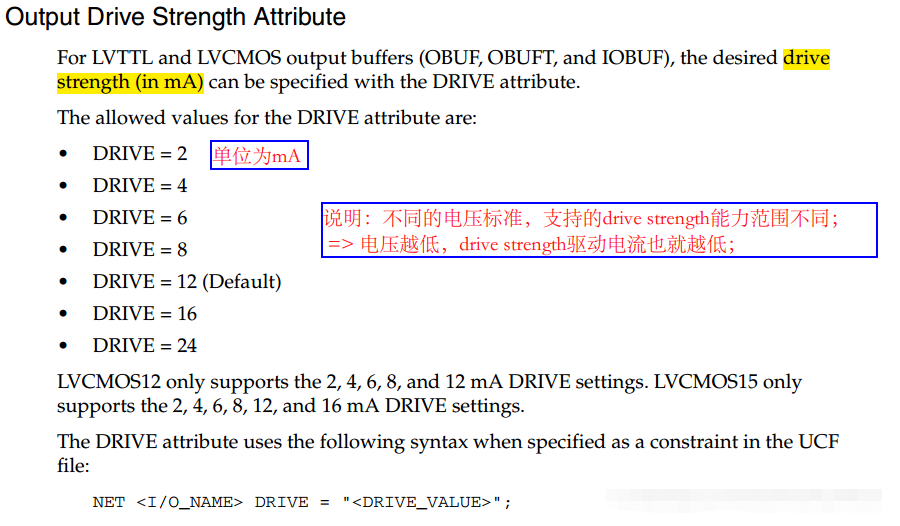

1.2.output strength(输出驱动器的电流驱动能力)

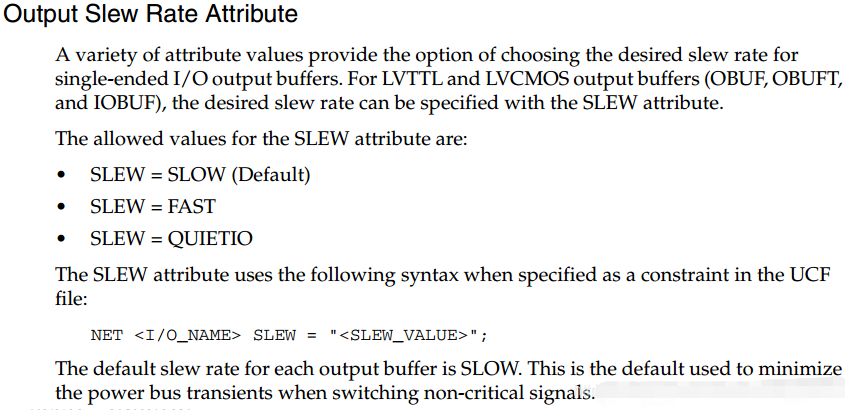

1.3.slew rate(输出电压压摆率)

注明:压摆率越快,电平转换时间越短,时间性能越优;

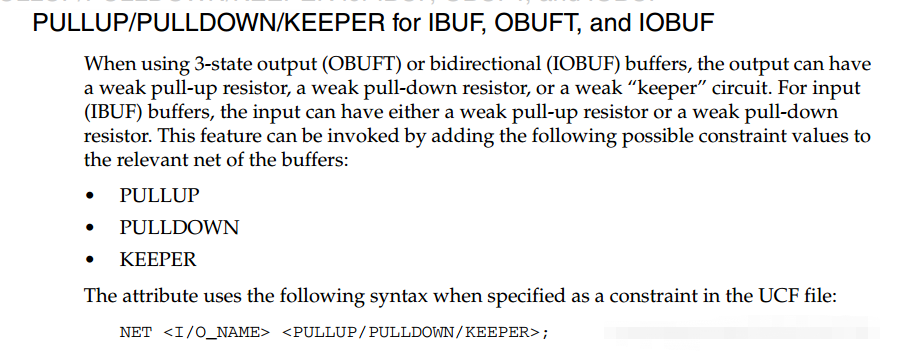

1.4.Pull type(上下拉类型)

1.5.On-chip termination(输入端/输出端的内置片上端接电阻)

当使用高速IO接口时,在接收端通常需要匹配的端接电阻,有利于高低电平的转换和提高信号的完整性,且端接电阻尽可能的放置在接收端。

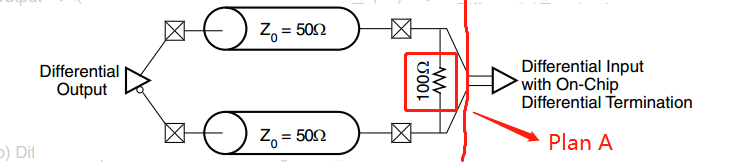

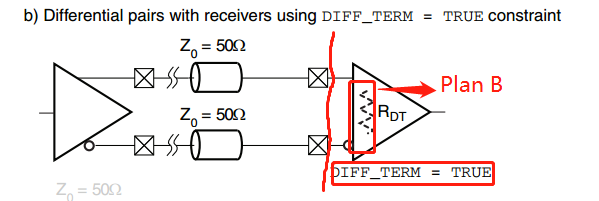

1.5.1 差分输入端接电阻配置

通常需要在差分输入端并行端接100Ω的电阻,FPGA在差分输入接收器提前内置了端接电阻,其阻值R为100Ω,为可选项optional。设计者也可以采用外接端接电阻来进行电阻匹配,阻值选择更灵活。采用片上内置的端接电阻可以节省无聊和缩小PCB面积

通过UCF文件进行约束,是否使用差分输入端接电阻,语法规则如下:

NET <I/O_NAME> DIFF_TERM = "<TRUE/FALSE>"

1.5.2 单端输入端接电阻配置

通过UCF文件进行约束,是否使用输入端接电阻,语法规则如下:

NET <I/O_NAME> IN_TERM = "UNTUNED_SPLIT_<25,50,75>"

1.5.3 输出端接电阻配置

由上图可知,输出端(也称为源端)也可以配置输出端接电阻,以减少信号的反射,应用在高速单端信号场合,例如FPGA输出驱动DDR3芯片。输出端接电阻也是optional可选项,常见阻值R为none,25Ω,50Ω,75Ω。通过UCF文件进行约束,是否使用单端输出端接电阻,语法规则如下:

NET <NET NAME> OUT_TERM = <NONE/ UNTUNED_25 / UNTUNED_50 / UNTUNED_75>;

2.实例应用:

具体在FPGA中使用时,我们在FPGA约束文件XDC需要对FPGA的管脚做如下处理:

OUTPUT管脚配置:

1.I/O std:

2.output strength

3.slew rate

4.Package-PIN

5.offchip_Term:out_term

INPUT管脚配置:

1.I/O std:

2.Package-PIN

3.offchip_Term(选配):in_term

常见IO接口标准之FPGA_CAOXUN_FPGA的博客-CSDN博客_fpga io口

3.电平标准和阻抗匹配

关于高速接口:LVPECL, LVDS, HSTL, and CML的定义以及端接匹配可参考TI的官方设计指导

下载地址如下:

1.LVPECL、VML、CML、LVDS接口定义介绍-其它文档类资源-CSDN下载

2.TI官方指导LVPECL、LVDS、HSTL、AndCML接口AC耦合匹配教程-其它文档类资源-CSDN下载

或者参考以下教程:

本文详细介绍了Xilinx 7系列FPGA及更高系列的I/O接口配置,包括HP BANK与HR BANK的区别,高速收发器GTX、GTH等的应用场景及其性能对比。同时,还探讨了I/O接口的配置属性,如电平标准、输出驱动强度、压摆率、上下拉类型及端接电阻等,并提供了实例应用。

本文详细介绍了Xilinx 7系列FPGA及更高系列的I/O接口配置,包括HP BANK与HR BANK的区别,高速收发器GTX、GTH等的应用场景及其性能对比。同时,还探讨了I/O接口的配置属性,如电平标准、输出驱动强度、压摆率、上下拉类型及端接电阻等,并提供了实例应用。

1364

1364

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?