在嵌入式开发的世界里,SPI(Serial Peripheral Interface,串行外设接口)绝对是个响当当的名字。它就像一个高效的“快递员”,在微控制器、传感器、ADC、DAC等设备之间快速传递数据。SPI以高速、简单、易实现的特点,成了无数嵌入式系统的“香饽饽”。

但对于新手来说,SPI的四线结构、时钟信号、模式配置可能会让人有点晕乎。别慌!这篇文章将带你从零开始,深入浅出地搞懂SPI的方方面面。读完后,你不仅能明白SPI的原理,还能信心满满地在项目中用起来!

什么是SPI?

SPI,全称串行外设接口,是一种同步、串行、全双工的通信协议,专为设备间的短距离数据交换设计。它采用主从架构,由一个主设备(Master)控制多个从设备(Slave),通过四条线实现高效通信。

简单来说,SPI就像一个对话场景:主设备是大哥,负责发号施令和控制节奏;从设备是小弟,乖乖听指令并回应。数据通过专属线路一比特一比特地传输,速度快、效率高。

SPI的“四线家族”

要搞懂SPI,先来认识它的核心——四条通信线。假设我们有一个最简单的场景:一个主设备和一个从设备连接。

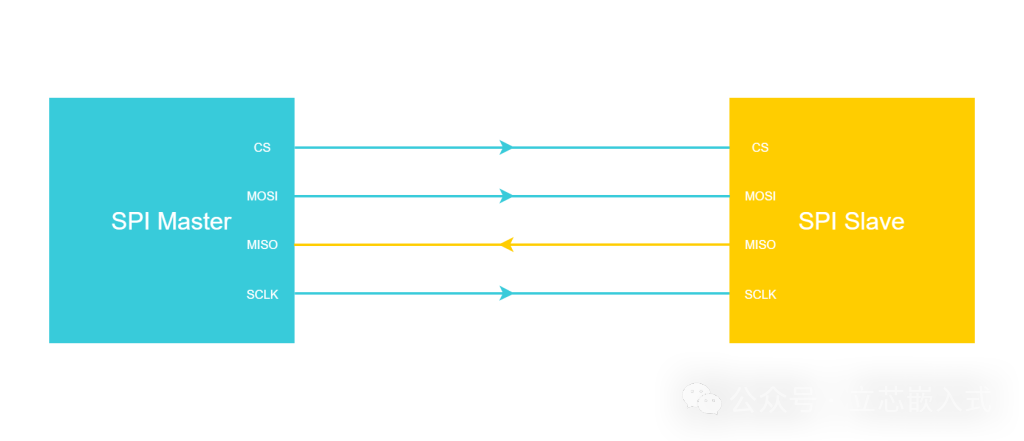

SPI的四条线分别是:

-

MOSI(Master Output Slave Input):主设备输出、从设备输入的线,数据从主设备流向从设备。

-

MISO(Master Input Slave Output):主设备输入、从设备输出的线,数据从从设备流向主设备。

-

SCLK(Serial Clock):时钟信号线,由主设备生成,负责同步数据传输的节奏。

-

CS(Chip Select,或称SS,Slave Select):片选信号线,用于主设备选择要通信的从设备。

通信流程

SPI通信的典型过程是这样的:

-

主设备通过拉低某个从设备的CS线,选中它。

-

主设备在SCLK线上生成时钟信号,控制数据传输的节奏。

-

数据通过MOSI和MISO线同时双向传输:主设备发送数据到从设备,从设备同时回传数据到主设备。

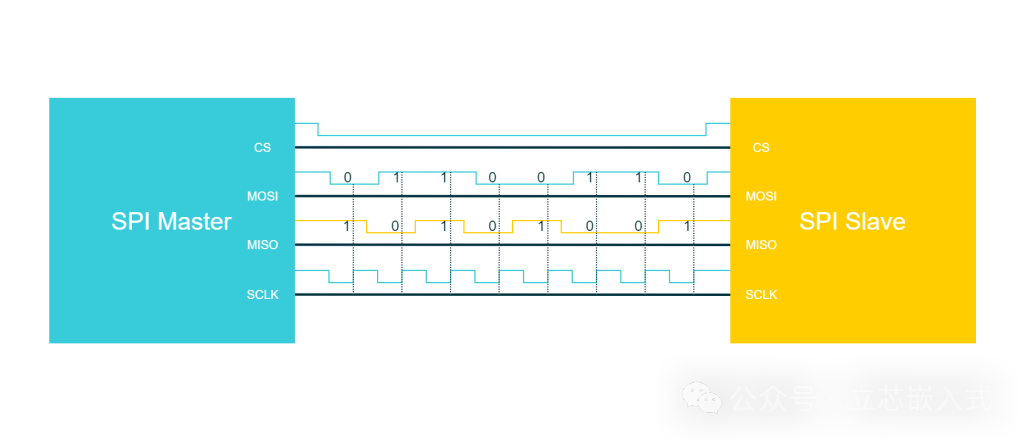

每次传输的数据通常是8位、16位或32位的“字”。比如,传输一个8位数据,就需要8个时钟周期,每周期传输1位,MOSI和MISO同时工作,效率杠杠的!

因为有专门的时钟线(SCLK)同步,SPI被称为同步协议;数据一位位串行传输,所以是串行协议;MOSI和MISO同时工作,所以是全双工协议。

推拉还是开漏?SPI的线路方向

SPI的四条线方向性非常明确:

| 引脚 | 主设备(Master) | 从设备(Slave) |

|---|---|---|

| SCLK | 输出 | 输入 |

| CS | 输出 | 输入 |

| MOSI | 输出 | 输入 |

| MISO | 输入 | 输出 |

由于方向固定,SPI的引脚采用推拉(Push-Pull)模式,意思是引脚可以主动输出高电平或低电平,驱动能力强,信号稳定。

这点和I2C协议不同。I2C的线路是双向的,采用开漏(Open-Drain)模式,防止主从设备同时驱动线路导致短路。SPI的单向线路设计让通信更简单直接,但也意味着它不像I2C那样支持多主设备。

时钟信号:SPI的“节拍器”

SPI的时钟信号(SCLK)由主设备生成,作用就像乐队的指挥,确保主从设备数据传输的节奏一致。主设备通常是微控制器,而从设备可能是传感器(如加速度计)或存储芯片。

SPI没有像UART那样的起始/停止位,每个时钟周期直接传输一位数据,接收一位数据。所以,SPI的时钟频率(也叫波特率)直接决定了传输速度。

时钟速度的限制

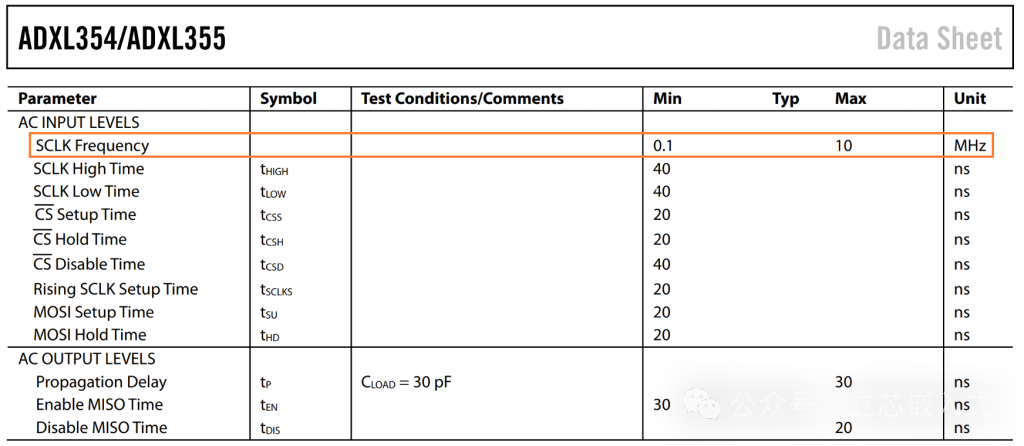

理论上,SPI的时钟频率可以很高,甚至达到数百兆赫兹。但实际中,从设备的处理能力往往是瓶颈。比如,ADXL355加速度计的SPI接口最大支持10MHz,超过这个频率它就“跟不上”了。

此外,高频传输时,线路的寄生参数(电容、电感)可能导致信号失真,影响通信可靠性。所以,选时钟频率时要参考从设备的数据手册,确保速度和稳定性兼顾。

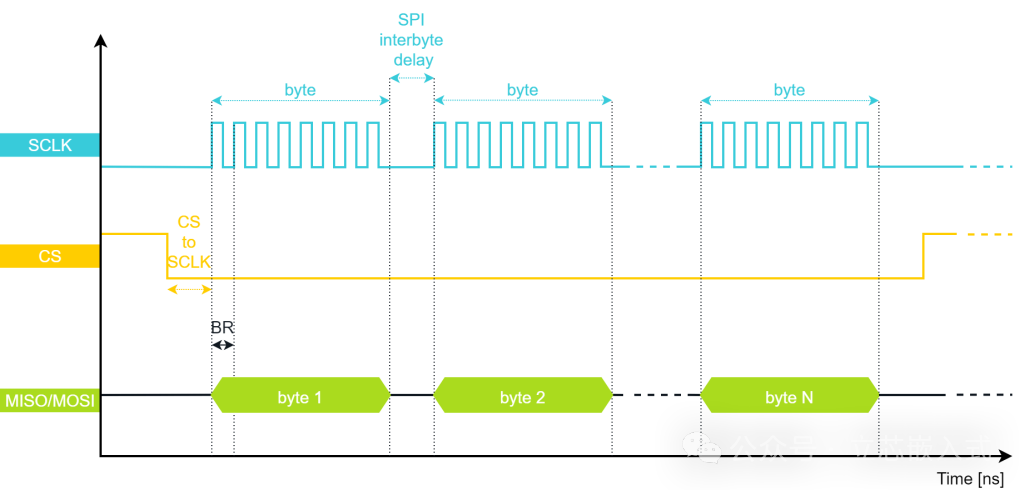

一点小“开销”

虽然SPI理论上没有额外开销,但实际通信中,CS拉低到第一个时钟边沿的延迟、字节间隙等都会引入少量开销,稍微降低有效数据速率。

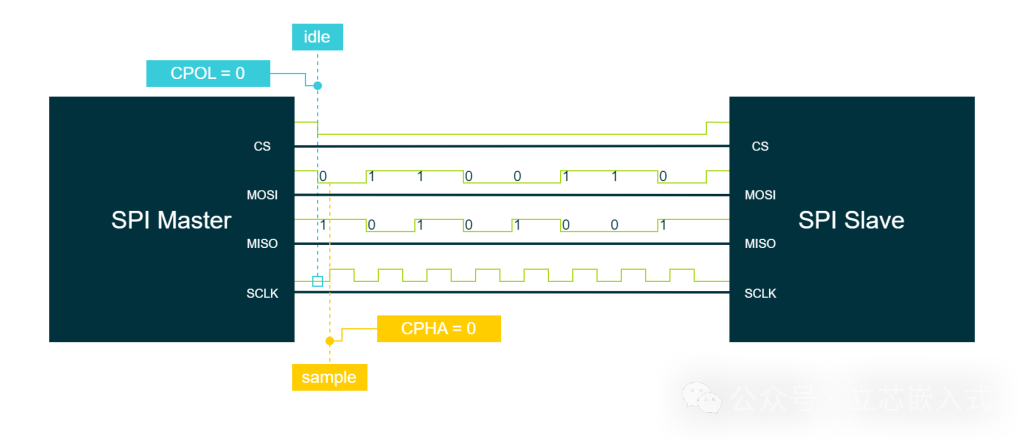

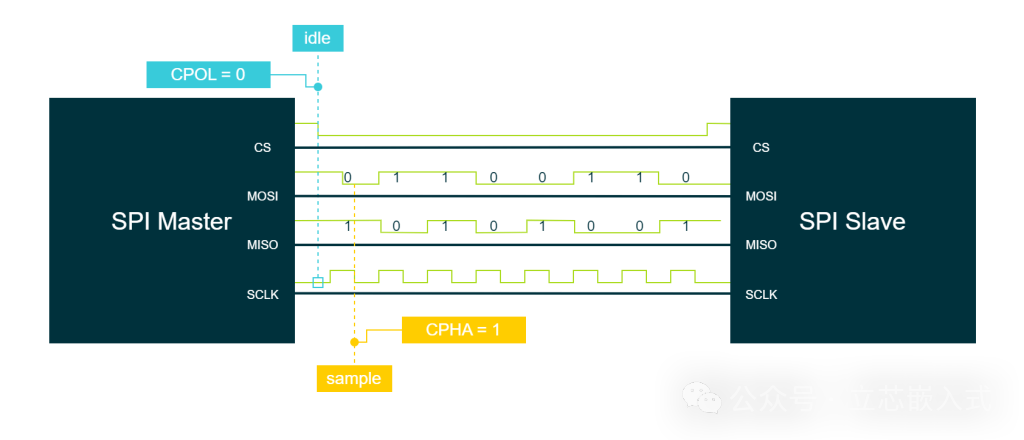

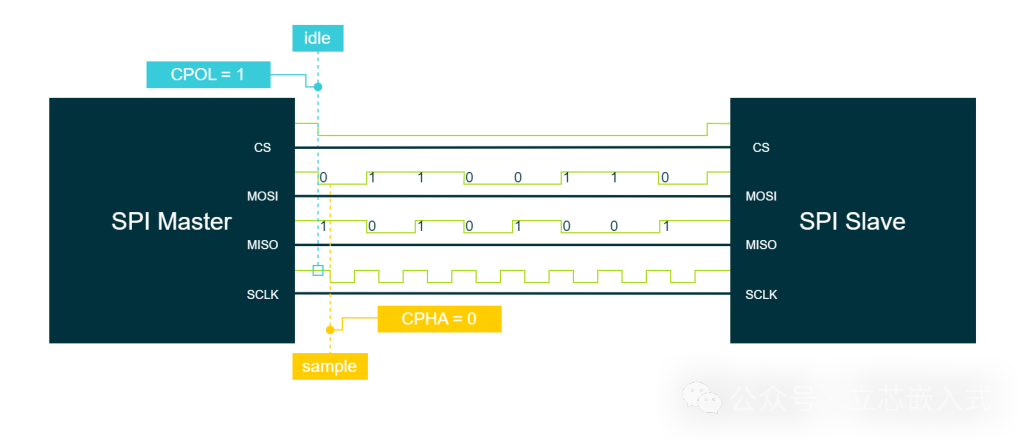

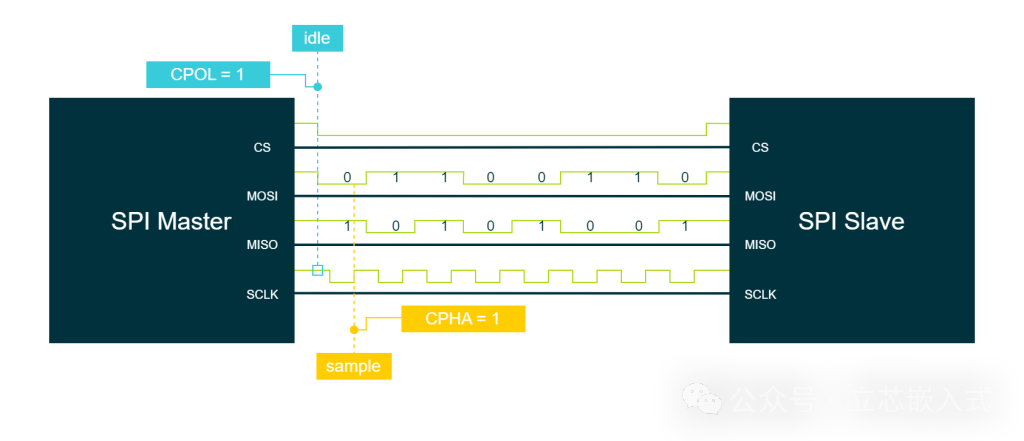

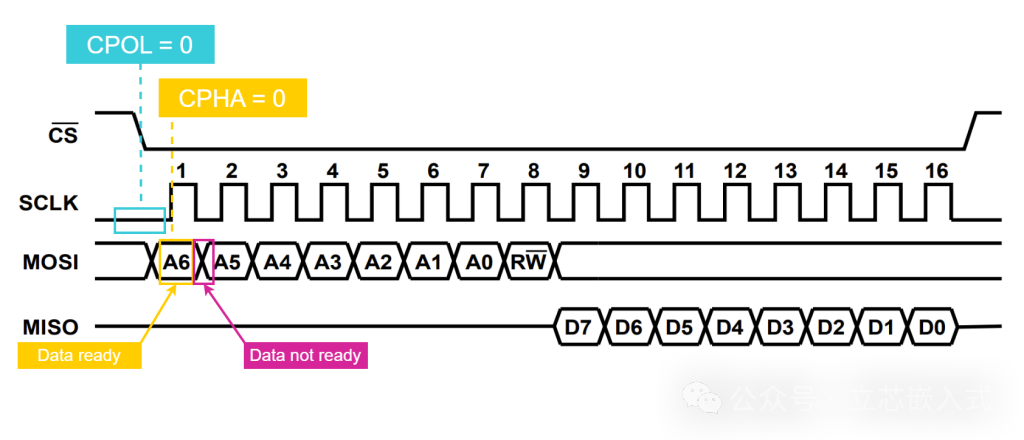

SPI的四种模式:CPOL与CPHA的组合

SPI有四种工作模式,由时钟极性(CPOL)和时钟相位(CPHA)决定。这两个参数控制数据在时钟信号的哪个边沿被采样和发送。

-

CPOL(Clock Polarity):决定时钟在空闲时的电平。

-

CPOL = 0:空闲时低电平。

-

CPOL = 1:空闲时高电平。

-

-

CPHA(Clock Phase):决定数据在时钟的哪个边沿被采样。

-

CPHA = 0:第一个时钟边沿采样。

-

CPHA = 1:第二个时钟边沿采样。

-

四种模式的组合如下:

| SPI模式 | CPOL | CPHA | 采样边沿 |

|---|---|---|---|

| 模式0 | 0 | 0 | 上升沿 |

| 模式1 | 0 | 1 | 下降沿 |

| 模式2 | 1 | 0 | 下降沿 |

| 模式3 | 1 | 1 | 上升沿 |

怎么理解这些模式?

以模式0(CPOL=0, CPHA=0)为例:

-

时钟空闲时为低电平(CPOL=0)。

-

数据在第一个时钟边沿(上升沿)采样(CPHA=0)。

这意味着主从设备需要在上升沿之前准备好数据,并在上升沿采样对方的数据。

其他模式类似,只是时钟的起始电平和采样边沿不同。实际使用时,主设备必须配置与从设备相同的模式,否则通信会出错。数据手册通常会明确说明从设备的支持模式,比如ADXL355就支持模式0。

片选(CS):SPI的“门禁卡”

CS(Chip Select)信号是主设备用来“点名”从设备的。CS是低电平有效,当主设备拉低某个从设备的CS线时,该从设备被选中,开始通信。

CS信号还有个重要作用:当CS为高电平时,从设备的MISO、MOSI和SCLK线进入高阻态,避免线路冲突。这在多从设备场景下尤其重要。

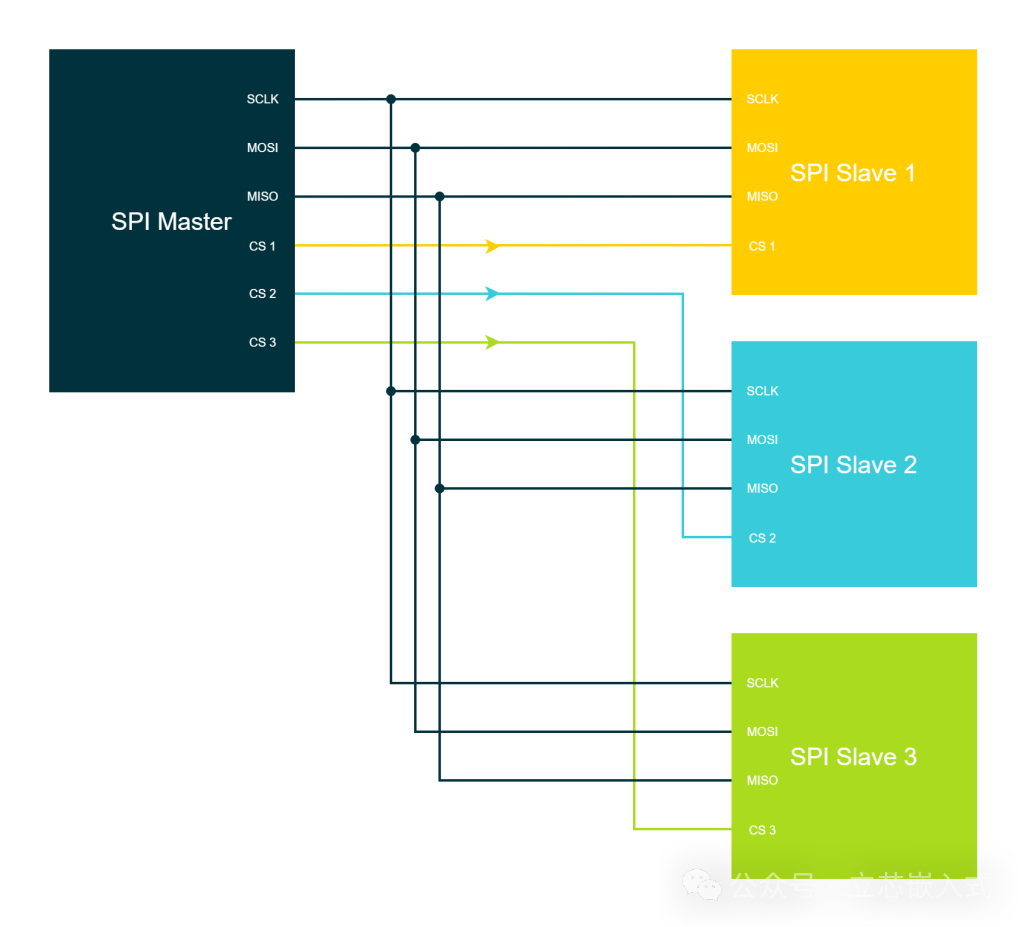

SPI的两种拓扑:独立模式与菊花链

SPI支持两种连接方式:独立模式和合作模式(菊花链)。

独立模式

在独立模式下,每个从设备有独立的CS线,主设备通过拉低某个CS来单独与某个从设备通信。所有从设备共享SCLK、MOSI和MISO线。

优点:

-

主设备可以灵活选择与哪个从设备通信,时间分配自由。

-

适合需要独立控制多个设备的场景。

缺点:

-

CS线数量随从设备增加而增加,占用更多GPIO(3根公共线 + N根CS线)。

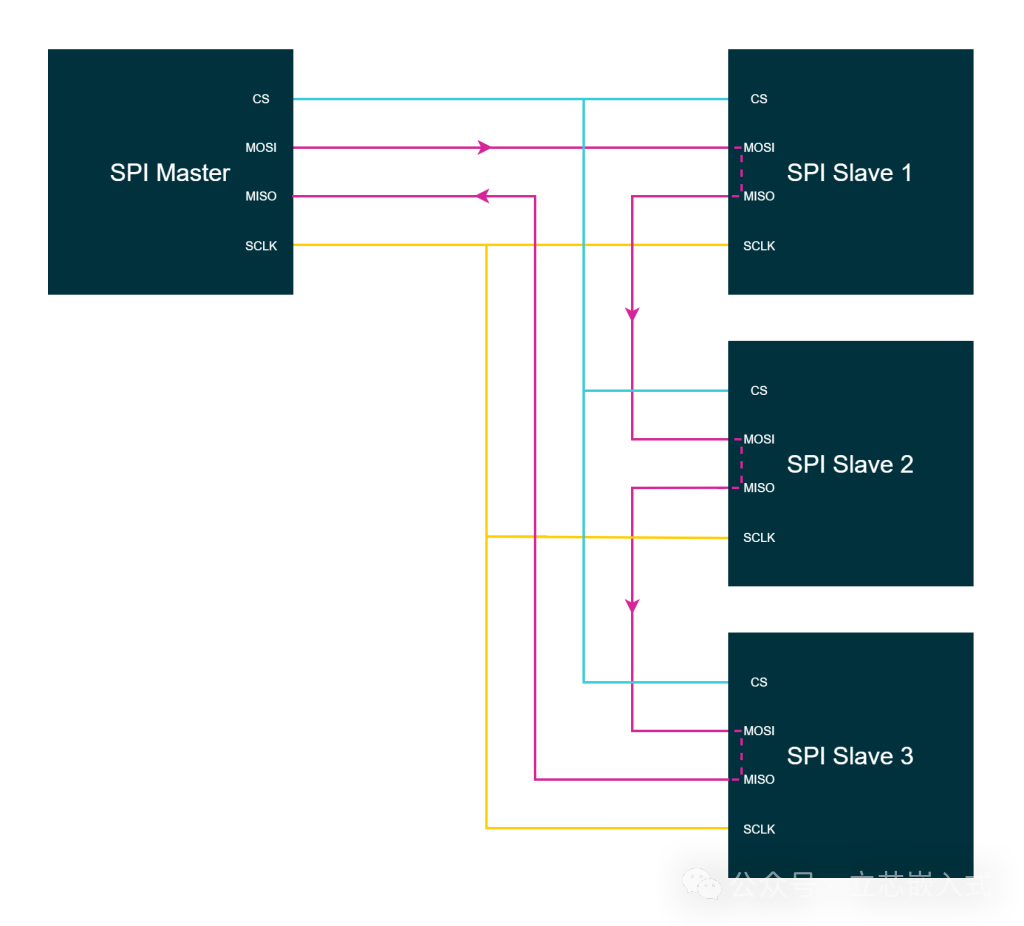

菊花链(Daisy Chain)

在菊花链模式下,所有从设备共享SCLK和CS线,数据线则串联:主设备的MOSI接到第一个从设备的MOSI,第一个从设备的MISO接到第二个从设备的MOSI,以此类推,最后一个从设备的MISO回到主设备的MISO。

优点:

-

只需要4条线,节省GPIO。

-

适合从设备数量多但通信需求简单的场景。

缺点:

-

数据需要逐个通过前面的从设备,延迟较高。

-

必须按顺序通信,无法直接跳到链尾的设备。

-

不是所有从设备都支持菊花链。

举个例子:假设有3个从设备,每个数据帧16位,想和第三个从设备通信,需要传输48位(3×16位),因为数据得先经过前两个从设备。

总结

SPI协议以其简单、高效、灵活的特点,成为嵌入式通信的明星协议。它的四线结构(MOSI、MISO、SCLK、CS)实现全双工通信,时钟模式(CPOL和CPHA)确保数据同步,片选机制灵活控制多设备通信。无论是独立模式还是菊花链,SPI都能适配不同场景。

1357

1357

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?