1.概述

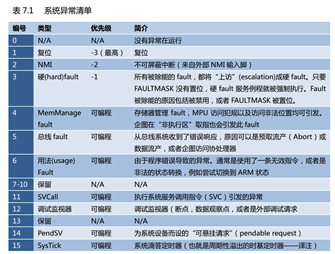

Cortex-M3 有16个异常(实际只用15个,也叫内核中断),并提供240个外部中断(针对内核来讲),有3个优先级最高的不可屏蔽异常,即1~3号异常。

F1中最多持68个可屏蔽中断(即内核中在外部中断),对应68个中断源。如USART1对应37#中断,但有多种条个可以触发该中断,如读完成、写完成、溢出等等都可以触发同一个中断源,进入中断函数后需根据状态位再判断具体中断原因。

STM32中断设置中,我们常用6组寄存器。

分别为:

ISER[8]:中断使能寄存器组,8个32位的寄存器对应STM32中支持的256个中断源,虽然F1没有使用这么多,但也把地址空间留出来以备后续器件扩展,以下寄存器组相同。你要使能某个中断,必须设置相应的 ISER 位为 1,使该中断被使能(这里仅仅是使能,后续还需中断分组、屏蔽、优先组设置、 IO 口映射等设置才算是一个完整的中断设置)。

ICER[8]:中断除能寄存器组。该寄存器组与 ISER 的作用恰好相反,是用来清除某个中断的使能的。专门设置一个 ICER 来清除中断位,而不是向 ISER 写 0 来清除,是因为 NVIC 的这些寄

存器都是写 1 有效的,写 0 是无效的。这是因为通过这种方式,使能/除能中断时只需把“当事位”写成1,其它的位可以全部为零。再也不用像以前那样,害怕有些位被写入 0 而破坏其对应的中断设置

本文详细介绍了STM32 Cortex-M3处理器的异常和中断处理,包括15个内核中断和68个外部中断,强调了3个最高优先级的不可屏蔽异常。讲解了中断使能、除能、挂起、解挂和优先级控制的寄存器,并阐述了中断优先级的设置方法,分为抢占优先级和子优先级。最后讨论了中断向量表的布局和启动过程中的映射配置。

本文详细介绍了STM32 Cortex-M3处理器的异常和中断处理,包括15个内核中断和68个外部中断,强调了3个最高优先级的不可屏蔽异常。讲解了中断使能、除能、挂起、解挂和优先级控制的寄存器,并阐述了中断优先级的设置方法,分为抢占优先级和子优先级。最后讨论了中断向量表的布局和启动过程中的映射配置。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5147

5147

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?