存储器保持大容量又被快速访问的原因:一个程序不会同时以相同的概率访问它全部的代码或数据

时间局部性:某个数据项被访问之后,可能很快被再次访问。循环结构。

空间局部性:某个数据项被访问之后,与其地址相近的数据项可能很快被访问。顺序结构。

存储器层次结构利用了如下特性:

时间局部性:将最近被访问的数据放在靠近处理器的地方。

空间局部性:将一些包含连续字的块移至存储器层次结构的较高层次。

Cache缺失引起流水线阻塞。

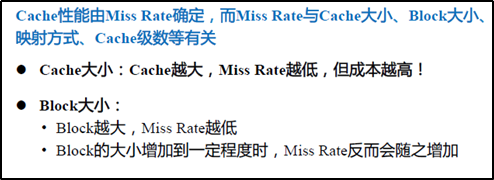

平均访问存储器时间(AMAT)= 命中时间 + 缺失率 * 缺失代价

两级Cache:

一级Cache减少命中时间,获得较短的时钟周期或较少的流水级。

二级Cache改善缺失率,减少长时间的访存代价。

更低的缺失代价允许使用更小的cache块,因为没有更多的延迟。

TLB是一个针对页表的Cache,它必须有标记域(tag)。

TLB中的引用位:如果在TLB中查找虚页号命中,引用位置位。

TLB中的脏位:处理器执行写操作,脏位置位。

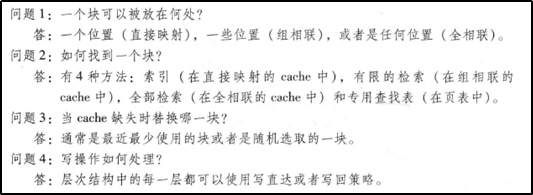

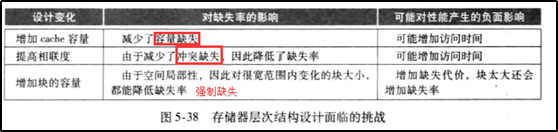

缺失分为3种:

强制缺失(冷启动缺失):第一次访问该数据时缺失。

容量缺失:针对全相联。

冲突缺失:针对直接映射和组相联。争用同一个Cache块。

Cache块增大,更好地利用空间局部性,以降低缺失率。但会带来缺失代价的增加。

当Block较大时,缺失损失的上升超过了缺失率降低带来的收益 ,故Cache性能也相应降低

Cache映射方式:

Cache容量小时, Cache映射方式对Miss Rate有影响

Cache容量大时,Cache映射方式对Miss Rate影响不大

容量失效和冲突失效可能引起Cache抖动

• 某些块在主存和Cache之间频繁传送

• 增加容量和相联性,有助于缓解这种现象

MIPS指令集:存储器访问指令,算术逻辑指令,分支指令。

逻辑单元:

组合单元:处理数据值。

状态单元:存储状态。有D触发器,寄存器,存储器

状态单元有2个输入,1个输出:

输入:写入单元的值,决定何时写入的时钟信号

输出:前一个时钟信号写入的数据值。

在流水线中,一个 MIPS 指令包含如下5个处理步骤:

1. 从指令存储器中读取指令。

2. 指令译码的同时读取寄存器。 MfPS 的指令格式允许同时进行指令译码和读寄存器。

3. 执行操作或计算地址。

4. 从数据存储器中读取操作数。

5. 将结果写回寄存器。

流水线冒险:

结构冒险:因缺乏硬件支持,而导致指令不能在预定的时钟周期内执行。

数据冒险:无法提供指令执行所需数据。

前推(旁路)

指令重排

控制冒险:取到的指令并不是所需要的。

分支预测:假定分支不发生。动态分支预测(分支预测缓存):1位或2位预测位。

旁路不能避免所有流水线阻塞的发生。取数-使用型数据冒险,流水线不得不阻塞一个时钟周期,可以使用代码重排解决这种冒险。

假设可以加入足够多的硬件使得在流水线的第二级能测试存储器、计算分支地址并更新PC。如果不能在第二级解决分支问题,分支结构上的阻塞将引起更大的速率下降。

较长的流水线会恶化预测的性能,并会提高错误预测的代价。

异常:控制流中任何意外的改变。

1. 未定义指令的执行

2. 算术溢出

中断:由外部引起的事件。

指令级并行

静态多发射:在编译时

动态多发射:在运行时

双发射MIPS处理器:ALU或分支,load或store。

2176

2176

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?