4.5 层次化和模块化的设计方法

对于较复杂的组合逻辑电路,往往不适合用一组方程式直接描述它们的逻辑功能,因而需要用层次化和模块化的设计方法。

层次化设计方法

层次化的设计方法是指“自顶向下”对整个设计任务进行分层和分块的划分,降低每层的复杂度,简化每个模块的功能;或“自底向上”地对每一个有限复杂度的模块进行实现或调用。模块化的设计方法是指将经过设计和验证的能完成一定功能的逻辑电路封装成为模块,在后续的设计中都可反复使用。

这两种方法的核心是首先将电路逐级分解为若干个简单的模块,然后再将这些模块设计好并连接起来。两种方法在设计实现中往往一起使用,这些简单的模块电路都可以用前面所讲的方法设计出来。

本节将介绍自底向上的方法。把上一节介绍的一些常用中规模模块作为已有的电路模块,利用它们进行一些电路设计和实现。最常见的一类设计方法是应用附加的控制端实现功能扩展,如下面三个例子。

例4.5.1:16线-4线优先编码器

试用4.4节中介绍的8线-3线优先编码器74HC148接成16线-4线优先编码器,将 𝐴15−𝐴0A15−A0 16个低电平输入信号编为0000~1111的4位二进制代码,其中 𝐴15A15 的优先权最高, 𝐴0A0 的优先权最低。

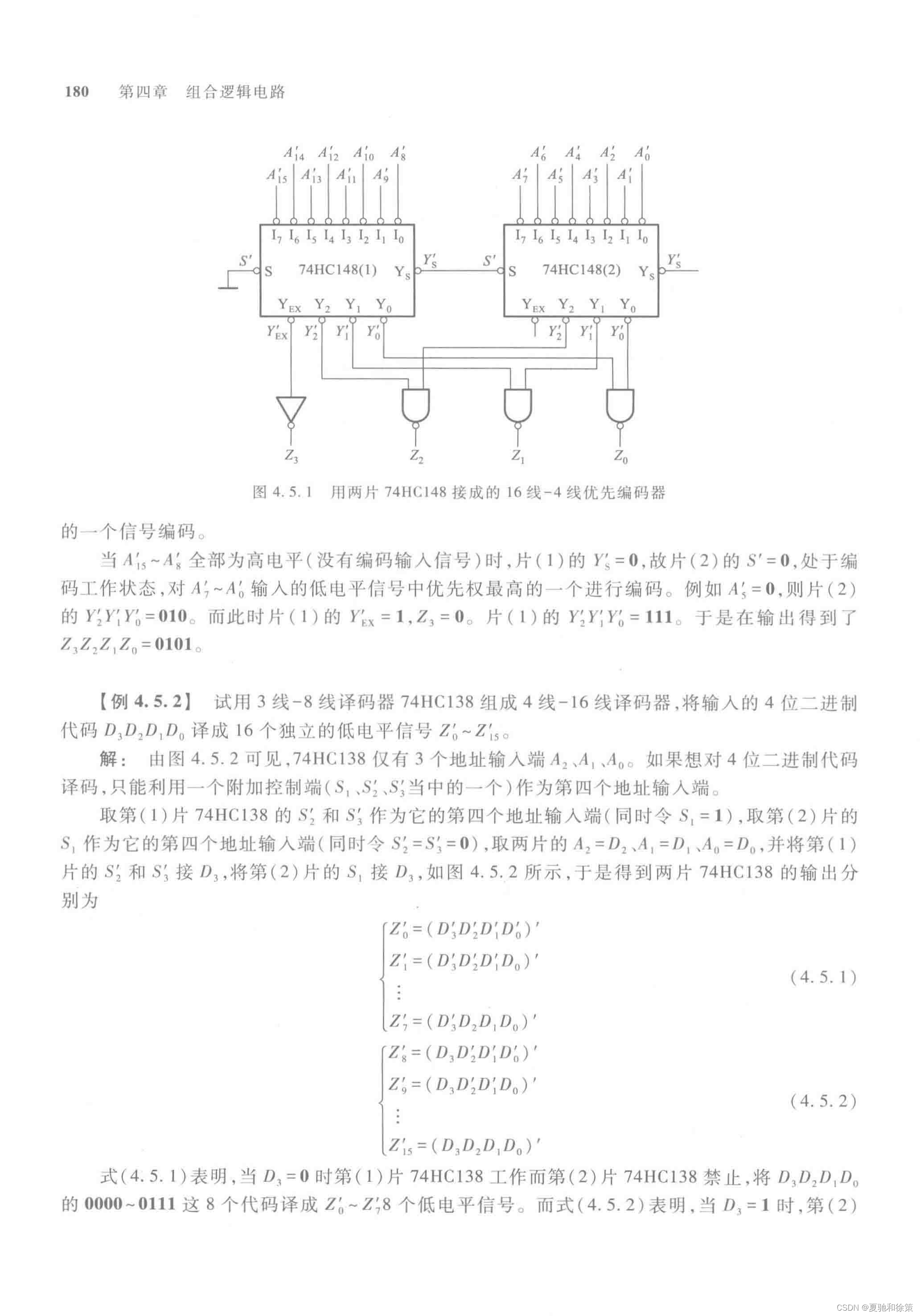

解:由于每片74HC148只有8个编码输入,所以需两个74HC148才能组合成一个16线-4线优先编码器。现将 𝐴15−𝐴8A15−A8 8个优先权高的输入信号接到第(1)片的 𝐼7−𝐼0I7−I0 输入端,而将 𝐴7−𝐴0A7−A0 8个优先权低的输入信号接到第(2)片的 𝐼7−𝐼0I7−I0 输入端。按照优先顺序的要求,只有 𝐼7−𝐼0I7−I0 均无输入信号时,才允许对 𝐼7−𝐼0I7−I0 的输入信号编码。因此,只要将第(1)片的“无编码信号输入”信号 𝑌𝐸YE 作为第(2)片的选通输入信号 𝐸2′E2′ 就行了。

此外,当第(1)片有编码信号输入时,它的 𝑌𝐸=0YE=0,无编码信号输入时 𝑌𝐸=1YE=1,正好可以用它作为输出编码的第4位,以区分8个高优先权输入信号和8个低优先权输入信号的编码。编码输出的低3位应为两片输出 𝑌2,𝑌1,𝑌0Y2,Y1,Y0 的逻辑或。

依照上面的分析,便得到了图4.5.1所示的逻辑图。

当 𝐴15−𝐴8A15−A8 全部为高电平(没有编码输入信号)时,片(1)的 𝑌𝐸=0YE=0,故片(2)的 𝐸2′=0E2′=0,处于编码工作状态,对 𝐴7−𝐴0A7−A0 输入的低电平信号中优先权最高的一个进行编码。例如 𝐴4=0A4=0,则片(2)的 𝑌2𝑌1𝑌0=010Y2Y1Y0=010。而此时片(1)的 𝑌𝐸=1YE=1,𝑍3=0Z3=0。片(1)的 𝑌2𝑌1𝑌0=111Y2Y1Y0=111。于是,在输出端得到了 𝑍3𝑍2𝑍1𝑍0=0101Z3Z2Z1Z0=0101。

例4.5.2:4线-16线译码器

试用3线-8线译码器74HC138组成4线-16线译码器,将输入的4位二进制代码 𝐷3𝐷2𝐷1𝐷0D3D2D1D0 译成16个独立的低电平信号 𝑍15−𝑍0Z15−Z0。

解:由图4.5.2可见,74HC138仅有3个地址输入端 𝐴2,𝐴1,𝐴0A2,A1,A0。如果想对4位二进制代码译码,只能利用一个附加控制端(𝑆1,𝑆2,𝑆3S1,S2,S3 当中的一个)作为第四个地址输入端。

取第(1)片74HC138的 𝑆2S2 和 𝑆1S1 作为它的第四个地址输入端(同时令 𝑆3=1S3=1),取第(2)片的 𝑆3S3 作为它的第四个地址输入端(同时令 𝑆2=𝑆1=0S2=S1=0),取两片的 𝐴2=𝐷3,𝐴1=𝐷2,𝐴0=𝐷1A2=D3,A1=D2,A0=D1,并将第(1)片的 𝑆1S1 和 𝑆2S2 接 𝐷0D0,将第(2)片的 𝑆3S3 接 𝐷0D0,如图4.5.2所示,于是得到两片74HC138的输出分别为:

𝑍𝑖′=(𝐷3𝐷2𝐷1𝐷0)′(4.5.1)Zi′=(D3D2D1D0)′(4.5.1)

𝑍𝑖=(𝐷3𝐷2𝐷1𝐷0)(4.5.2)Zi=(D3D2D1D0)(4.5.2)

当 𝐷3=0D3=0 时,第(1)片74HC138工作而第(2)片74HC138禁止,将 𝐷3𝐷2𝐷1𝐷0D3D2D1D0 的00000111这8个代码译成 𝑍7′−𝑍0′Z7′−Z0′ 8个低电平信号。而当 𝐷3=1D3=1 时,第(2)片74HC138工作,第(1)片74HC138禁止,将 𝐷3𝐷2𝐷1𝐷0D3D2D1D0 的10001111这8个代码译成 𝑍15−𝑍8Z15−Z8 8个低电平信号。这样就用两个3线-8线译码器扩展成一个4线-16线的译码器了。

例4.5.3:8位数值比较器

试用两片74HC85组成一个8位数值比较器。

解:根据多位数比较的规则,在高位相等时取决于低位的比较结果。因此只要将两个数的高4位 𝐶7,𝐶6,𝐶5,𝐶4C7,C6,C5,C4 和 𝐷7,𝐷6,𝐷5,𝐷4D7,D6,D5,D4 接到第(2)片74HC85上,而将低4位 𝐶3,𝐶2,𝐶1,𝐶0C3,C2,C1,C0 和 𝐷3,𝐷2,𝐷1,𝐷0D3,D2,D1,D0 接到第(1)片74HC85上,同时把第(1)片的 𝑌𝐴>𝐵,𝑌𝐴=𝐵,𝑌𝐴<𝐵YA>B,YA=B,YA<B 接到第(2)片的 𝐼𝐴>𝐵,𝐼𝐴=𝐵,𝐼𝐴<𝐵IA>B,IA=B,IA<B 就行了。

因为第(1)片74HC85没有来自低位的比较信号输入,所以将它的 𝐼𝐴>𝐵IA>B 和 𝐼𝐴<𝐵IA<B 端接0,同时将它的 𝐼𝐴=𝐵IA=B 端接1。这样就得到了图4.5.3所示的8位数值比较电路。

总结

上述例子都是采用“自底向上”的设计方法,在已有的中规模集成电路的基础上来完成设计和实现。在采用“自顶向下”的设计方法时,首先也是要对整个设计任务进行分块划分,然后再分别对每个模块进行设计实现。在选用大规模集成电路器件进行设计时,通常都采用“自顶向下”的设计方法。其中包括底层的设计都是利用EDA工具来辅助完成的。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?