文章目录

- 题目:STICKER: A 0.41-62.1 TOPS/W 8bit Neural Network Processor with Multi-Sparsity Compatible Convolution Arrays and Online Tuning Acceleration for Fully Connected Layers

- 时间:2018

- 会议:Symposium on VLSI Circuits

- 研究机构:清华刘勇攀

1 缩写 & 引用

- CSC: compressed sparse column

- COO: coordinate sparse matrix format

- NSG: dense format with zero-guard

- NSD: dense format without zero=guard

- IDX: index module

2 abstract & introduction

本篇论文的主要贡献:

- 自动化的sparsity detector,可以切换处理器模式

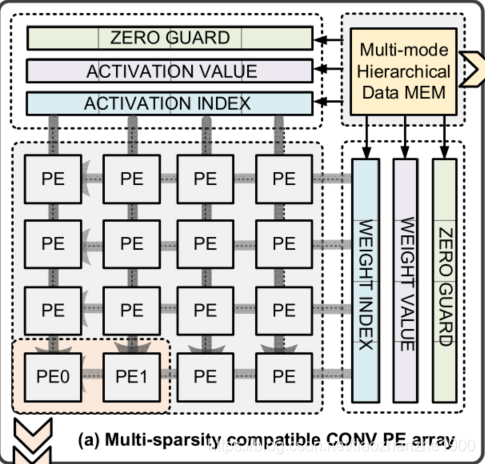

- 支持multi-sparsity的PE阵列和memory,组相联PE支持密集和稀疏操作

- 对稀疏全连接层online tuning的PE,基于Compressed Sparse Column的后向传播

在65nm工艺下,8bit位宽实现了62.1TOPS/W,7.8平方微米,200MHz@1V,运行的是Alexnet和lenet

3 面向稀疏性的处理器设计

3.1 sparsity-aware控制器

权重和activation分别由sparse,medium和dense三种模式,两两组合就是九种模式,PE阵列可以在这九种模式中切换,这就需要一个online activation sparsity detector

3.2 multi-sparsity compatible卷积PE阵列

不同模式下会使用不同的编码方式将activation存储在memory中:

- sparse模式:coordinate sparse matrix format (COO)

- medium模式:dense formats with zero-guards (NSG)

- dense模式:dense formats without zero-guards (NSD)

multi-sparsity compatible set-associative卷积PE阵列可以支持上面三种模式,支持不规则的部分和,具体实现是二路组相联

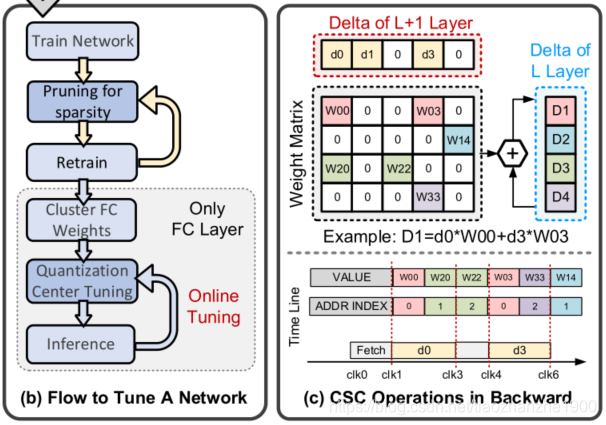

3.3 对稀疏全连接层的online tuning PE

两点主要的创新:

- 权重被32个量化中心聚类,用K-means算法,权重更新着干扁量化中心而不是所有的权重,这样更快

- CSC格式可以更快的后向传播

- 题目:STICKER: An Energy-Efficient Multi-Sparsity Compatible Accelerator for Convolutional Neural Networks in 65-nm CMOS

- 时间:2019

- 期刊:JSSC

- 研究机构:清华刘勇攀

1 缩写 & 引用

- DGB: Data Zero Guard Bank

2 abstract & introduction

之前的关于稀疏性的工作可以分成两类:

- 存数据还是正常存,遇到0跳掉或者关掉:可以节省能耗,不能节省存储空间

- 存储和计算都是只看非零元素,但是当数据是密集的时候,就会有overhead

本篇论文的主要贡献: 利用神经网络的稀疏性来降低能耗

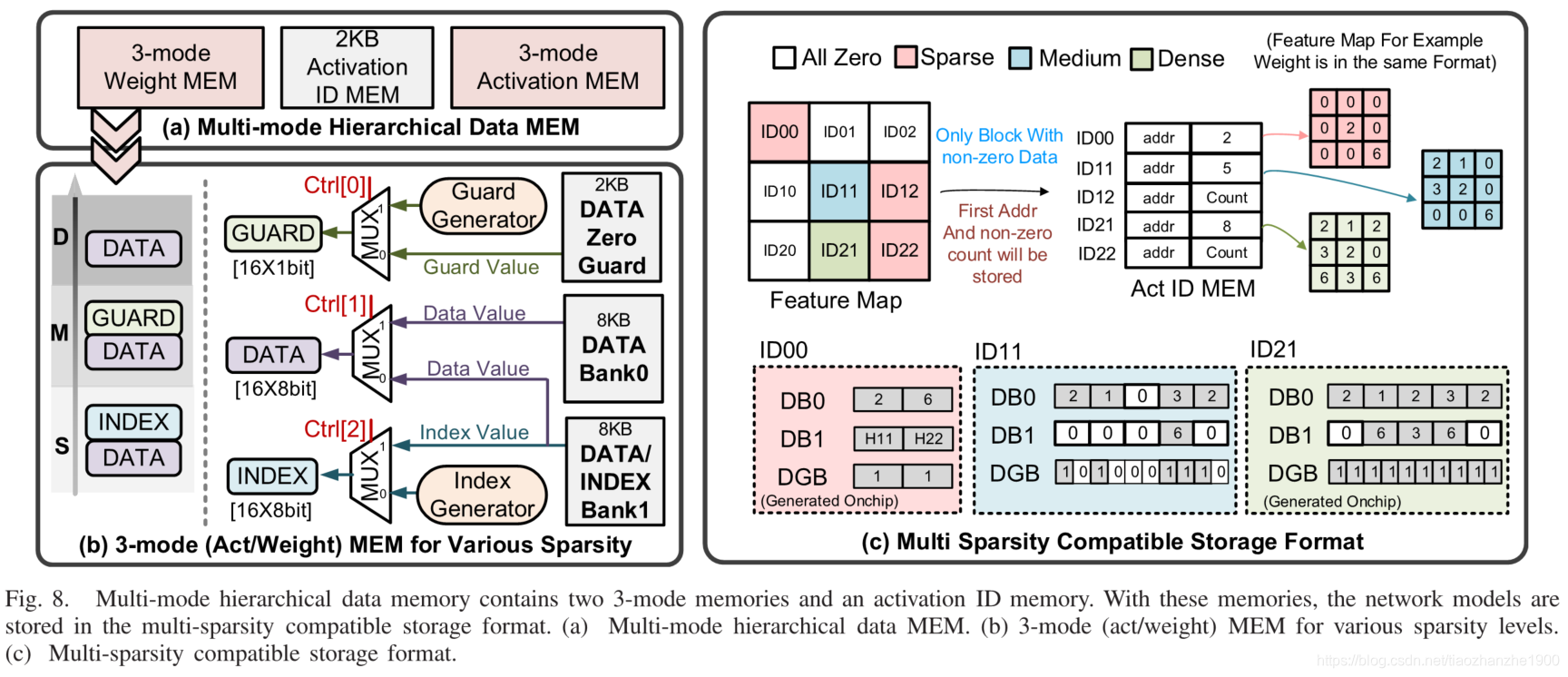

- 多级稀疏模式的控制

- 面对不同稀疏性的多级存储模式的选择

- 组相联的PE结构,支持不同稀疏模式

3 硬件架构总览

4 分级稀疏度的控制和数据流

5 分级稀疏度的存储设计

每个Memory都有三个Bank:

- DGB: Data Zero Guard Bank

- DB0: Data Bank 0

- DB1: Data Bank 1

存储以16x16为单位切成block,一共有四种:zero block、sparse block、medium block、dense block

2369

2369

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?