1.上节的invert 寄存器取反时,reference model 也要此值。reference model 怎么读呢?

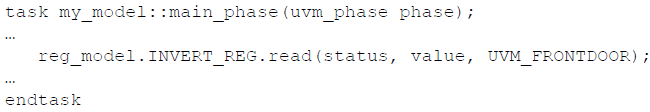

1)在一个大的设计中,有很多寄存器,之前的方式很麻烦。如果有寄存器模型,可以简化为:

启动sequence 及将读取结果返回,都有寄存器模型自动完成。

2.没有寄存器模型,只能通过FRONTDOOR 访问寄存器。有了之后,只与寄存器模型打交道。

3.可以在任何耗费时间的phase 中使用寄存器模型以前门或后门访问。在不消耗时间的phase(如check_phase) 使用后门访问来读取寄存器的值。

4.前门:通过模拟cpu 在总线上发出操作。消耗仿真时间。后门:通过层次化的引用来改变寄存器的值。

5.寄存器模型还提供一些任务,如mirror,update,可以批量完成寄存器模型与DUT的交互。

6.寄存器模型本质就是重新定义了验证平台与DUT 寄存器的接口,简化流程,减少工作量。

954

954

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?