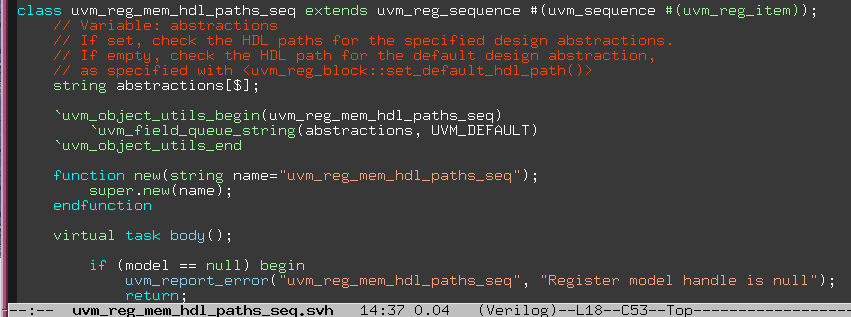

1.UVM 提供了一系列sequence用于检查寄存器模型及DUT 的寄存器。其中uvm_reg_mem_hdl_paths_seq 检查hdl 路径的正确性。原型为:

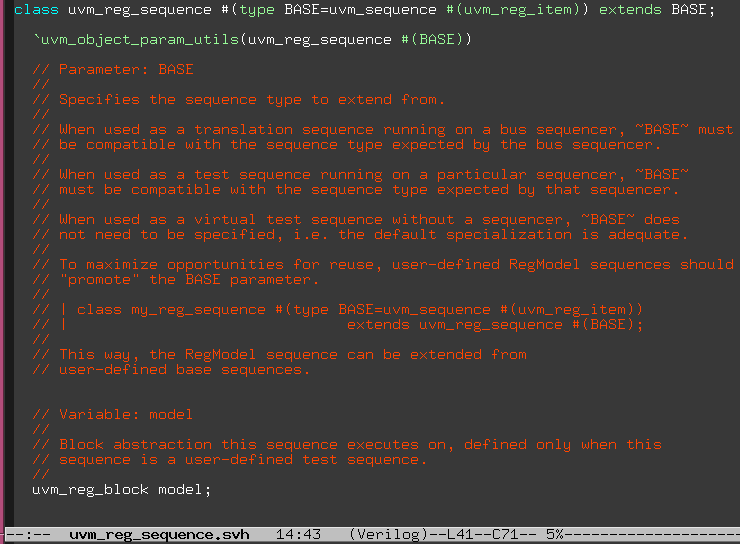

此sequence 的运行依赖于在基类uvm_sequence 中定义的一个变量:

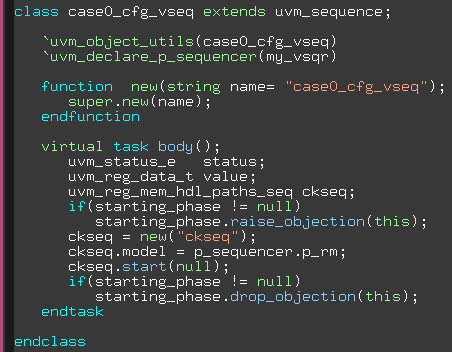

2.启动此sequence 时必须给model 赋值。在任意的sequence 中,可以启动此sequence:

1)start 传入的sequencer 为null。因为不依赖这个sequencer,而依赖于model 变量。

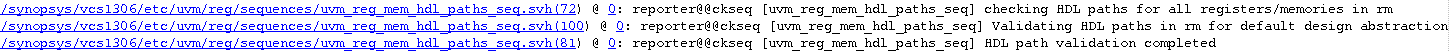

2)这个sequence 会试图读取hdl 所指向的寄存器,如果无法读取,报错。

3)还可以检查存储器。

4)如果某个寄存器,存储器在加入寄存器模型时没有指定其hdl 路径,那么检查时会跳过这个寄存器,存储器。

5759

5759

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?