硬件架构的艺术第三、四章

处理多个时钟

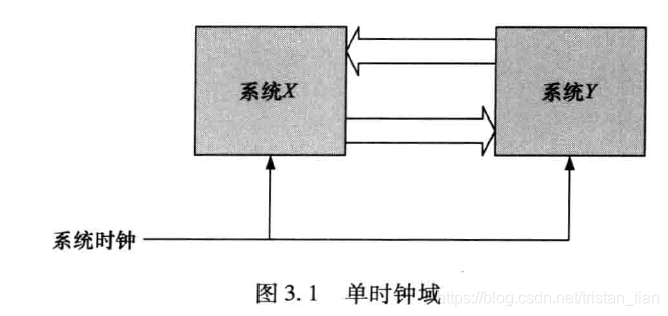

单时钟域

易于实现,并且更少产生于亚稳态、建立与保持时间违背方面的问题。

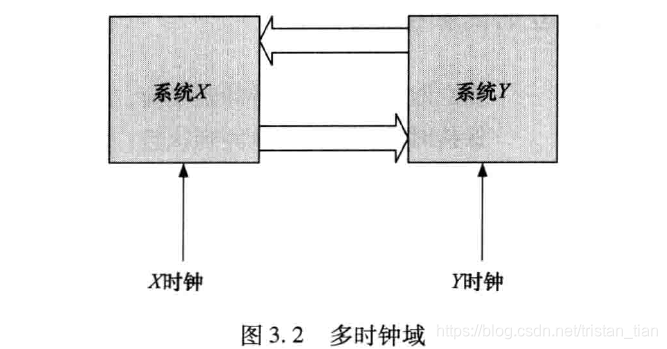

多时钟域

多时钟设计具有问题:

- 建立时间和保持时间的违背

- 亚稳态

多时钟设计的处理技术

通用的准则有时钟命名法和分模块设计

时钟命名法

例如:系统时钟可以命名为sys_clk,发送时钟可以命名为tx_clk,接收时钟可以命名为rx_clk,这样可以在脚本中使用通配符来对所有时钟进行操作。同样,属于同一个时钟域的信号,在命名时使用同样的前缀。

分模块设计

分模块设计:

- 每个模块在单个时钟下工作

- 在信号跨时钟域传输时,使用同步器模块,使进入某个时钟域内的模块信号,与该模块时钟保持同步

- 同步器模块规模尽可能小

跨时钟域

跨异步时钟域的传输可以分为两类:

- 控制信号的传输

- 数据信号的传输

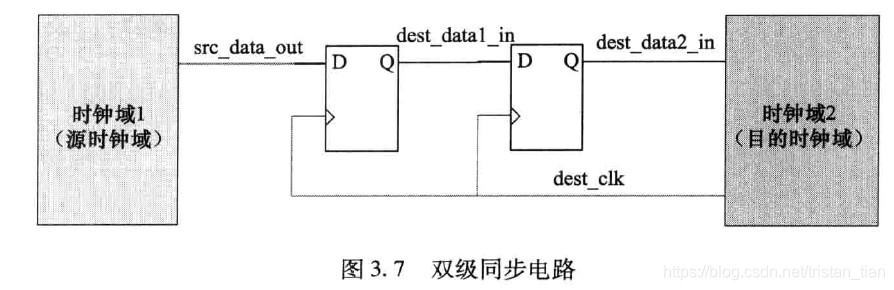

控制信号传输:

为减少亚稳态的影响,设计者最常用的方式是使用多级同步器,即两个或多个触发器串联起来组成的同步电路(使用两级同步电路就足以避免亚稳态的出现,只有在时钟频率非常高的设计中才要求使用三级同步器电路)

数据信号传输:

握手信号和异步FIFO

跨同步时钟域问题

同频零相位差时钟

唯一要求:保证STA(静态时序分析)通过,如果这一条件满足,就不会出现亚稳态问题和数据丢失或不一致问题。

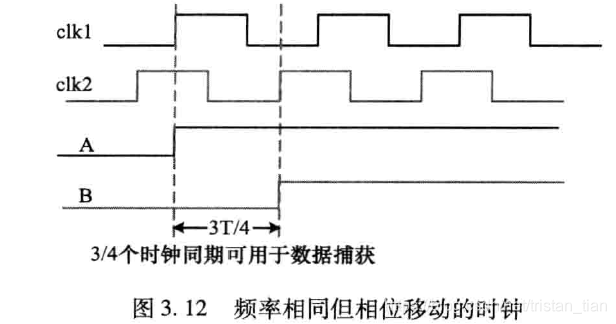

同频恒定相位差时钟

当数据从clk1 传输至clk2 时,由于更小的建立时间/保持时间余量,对于组合逻辑的延时约束都会变得更紧,如果组合逻辑的延时能够保证满足采样沿处建立时间和保持时间的要求,数据就可以正确传输,并且没有亚稳态产生(不需要同步器)

当数据从clk1 传输至clk2 时,由于更小的建立时间/保持时间余量,对于组合逻辑的延时约束都会变得更紧,如果组合逻辑的延时能够保证满足采样沿处建立时间和保持时间的要求,数据就可以正确传输,并且没有亚稳态产生(不需要同步器)

一般会创建这种情况以满足时序的要求(通过在发射边沿和捕获边沿加入偏移)

非同频、可变相位差时钟

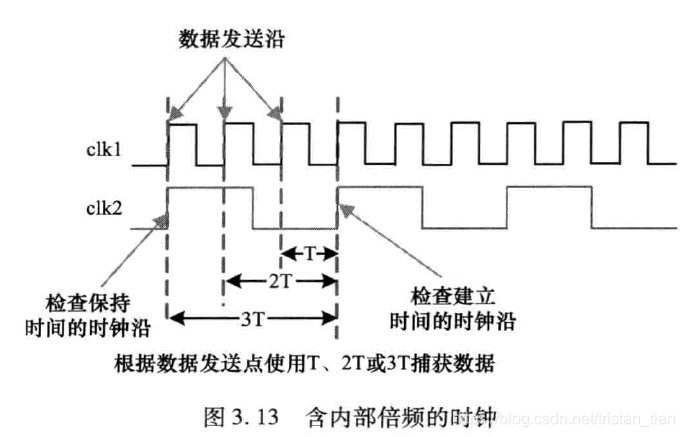

整数倍频率时钟

两个时钟的有效边沿的相位差是可变的,这两个时钟的有效边沿的最小相位差始终等于其中较快的那个时钟的时间周期

(以下的图,数据是由快时钟到慢时钟,可能会出现数据丢失,所以必须要将源数据保持至少一个目标时钟周期,可以使用一个简单的FSM实现)

clk1的频率是时钟clk2的三倍。clk2捕获数据的时间可能是T、2T或3T,取决于数据是在clk1哪一个边沿发送出来,所以应满足任意路径的最差延迟都应在时钟边沿相位差为T时满足建立时间的要求。

clk1的频率是时钟clk2的三倍。clk2捕获数据的时间可能是T、2T或3T,取决于数据是在clk1哪一个边沿发送出来,所以应满足任意路径的最差延迟都应在时钟边沿相位差为T时满足建立时间的要求。

由于至少都有较快时钟的一个完整的周期用来传输数据,所以通常可以保证满足建立时间和保持时间的要求,基本不会存在亚稳态或数据不一致的问题,也就无需使用同步器。

非整数倍频率时钟

由于一个时钟的频率是另一个时钟的非整数倍,所以有效边沿的相位差是可变的。此时两时钟之间的最小相位差足以使亚稳态发生(取决于实际的频率倍数和设计工艺)。

- 在源时钟和目的时钟有效沿之间有足够大的相位差,所以不会有亚稳态。

例如,clk1和clk2分别是clk=30ns的三分频与二分频,即clk1的周期是15ns,clk2的周期是10ns。这两个时钟的最小相位差为2.5ns,对于满足建立时间和保持时间足够了。由于相位差很小,避免在跨越两个时钟的未知使用任何组合逻辑,必须要使用同步器。

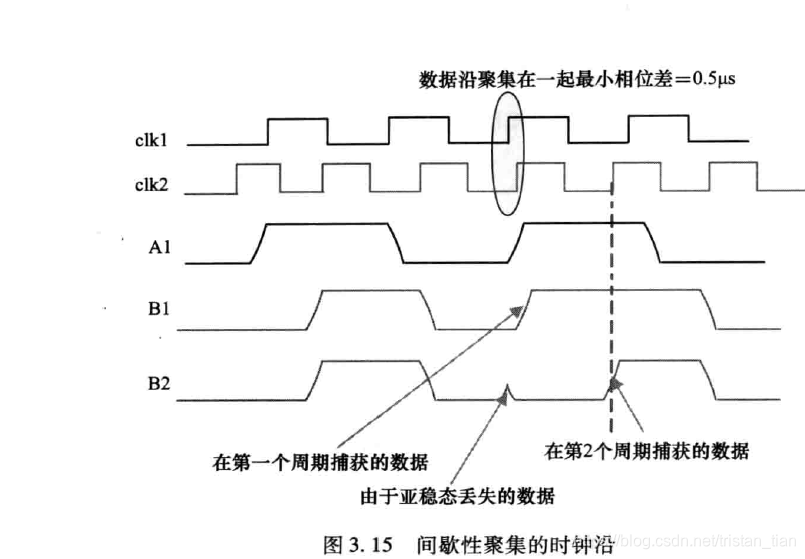

- 源时钟和目的时钟有效沿非常接近,导致产生亚稳态问题。

一旦有时钟边沿接近这种情况出现,下一个时钟周期就会留出足够大的时间冗余,使得数据的捕获不会出现违背建立时间或保持时间的要求。

例如,时钟clk1和clk2的周期分别为10ns和7ns,之间的最小相位差是0.5ns。必须要用同步器。

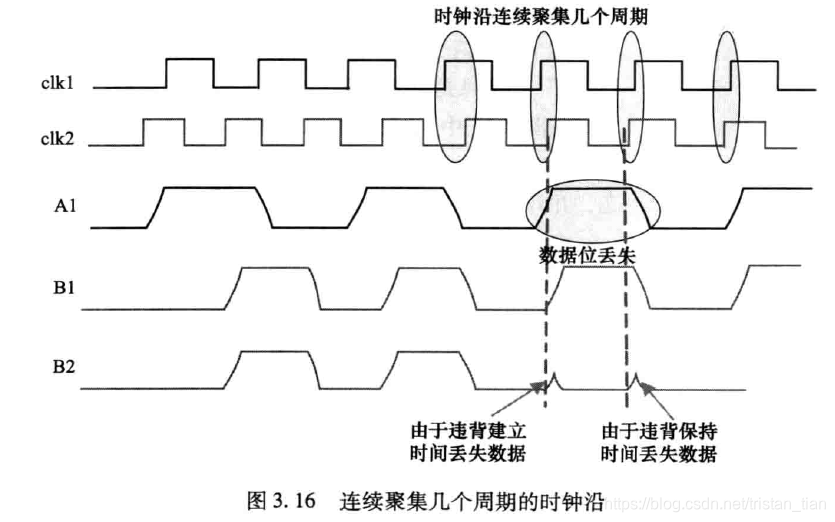

- 两个时钟的时钟沿在许多连续的周期中都非常接近

在这种情况下时钟的相位差差异很小,并且连续存在几个周期。除了变化的相位差异和周期性重复现象,其余都与异步时钟很相似。

clk1=10ns,clk2=9ns

在前两个周期中可能违背建立时间(源时钟在目的时钟之前),而在后两个时钟周期中可能会违背保持时间(目的时钟在源时钟之前)(除了亚稳态问题,数据从慢时钟域传递至快时钟域也可能丢失)。

为了不丢失数据,数据需要保持稳定至少两个目的时钟周期,既适用于从快到慢的传输,也适用于从慢到快的传输。

为了不丢失数据,数据需要保持稳定至少两个目的时钟周期,既适用于从快到慢的传输,也适用于从慢到快的传输。

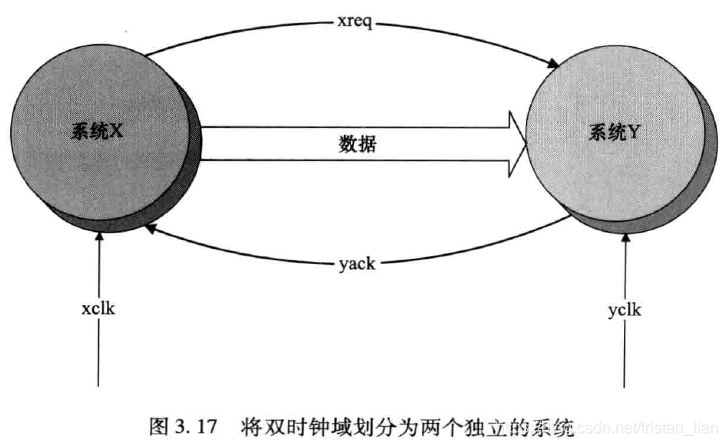

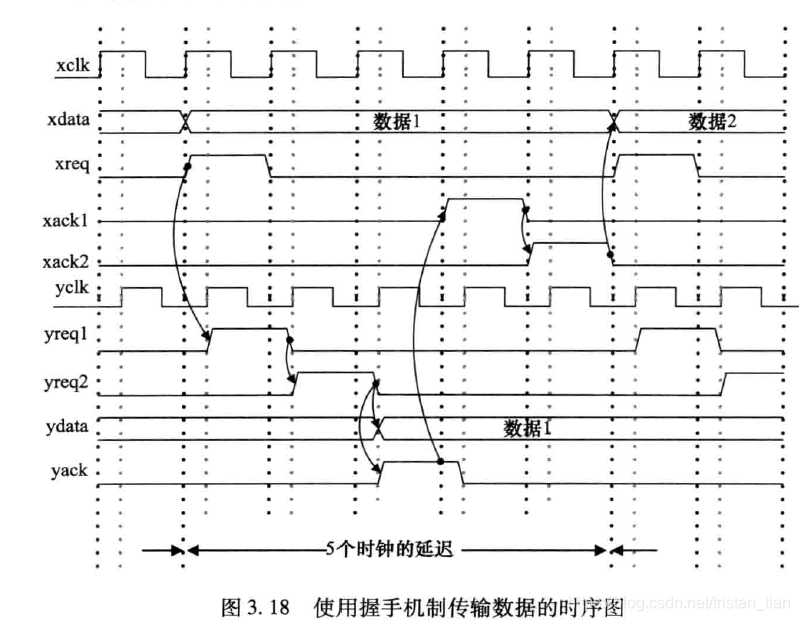

握手信号方法

使用握手信号是最古老的在不同域之间传输数据的方式。

(1)发送端将数据放到数据总线上并发送(xreq)信号,表示有效数据已经发送接受端的数据总线上,途中xreq->yreq1即将xreq同步至yclk时钟。

(2)接收器通过一个同步器,识别yreq2后,锁存数据总线上的数据,并发出确认信号yack

(3)yack信号同步至xclk,产生信号xack1

(4)发送端通过一个同步器,识别xack2。

(5)下一个时钟周期,将下一个数据放到数据总线上

所以安全地将一个数据从发送端传输至接受端需要5个时钟周期。由此看来握手信号的缺点也十分明显,传输单个数据的延迟太长

**握手信号要求:**数据应在发送时钟域上稳定至少2个时钟上升沿。

**缺点:**传输单个数据延时高

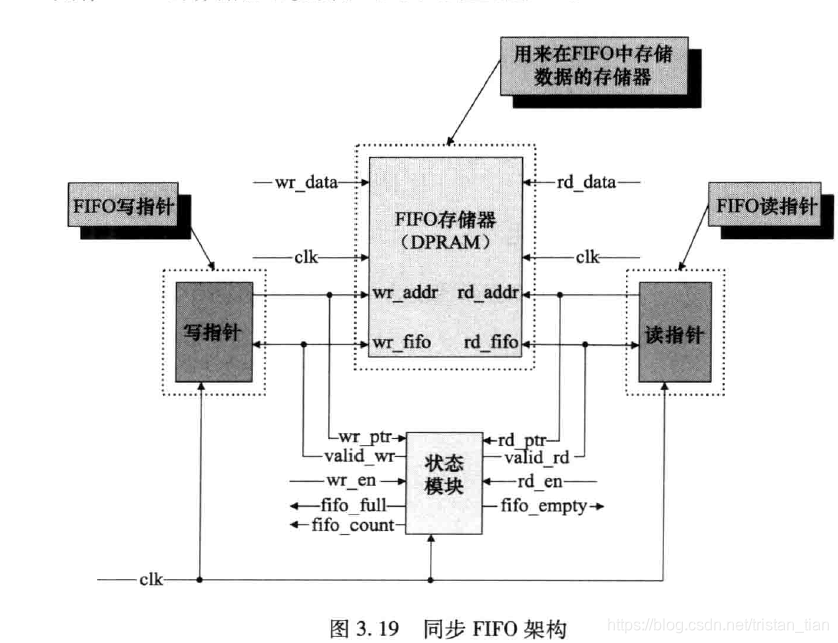

使用同步FIFO

同步FIFO的工作原理:在同一个时钟信号下,通过读、写指针产生各自的读、写地址,再通过产生的读、写地址分别从FIFO存储器中读取和写入数据。使用状态模块产生的fifo_empty和fifo_full信号。如果fifo_empty有效,说明FIFO已经“读空”,如果fifo_full有效,说明FIFO已经“写满”。

同步FIFO的工作原理:在同一个时钟信号下,通过读、写指针产生各自的读、写地址,再通过产生的读、写地址分别从FIFO存储器中读取和写入数据。使用状态模块产生的fifo_empty和fifo_full信号。如果fifo_empty有效,说明FIFO已经“读空”,如果fifo_full有效,说明FIFO已经“写满”。

而在读写指针相等时,FIFO要么空要么满,所以需要对这两种情况进行区分。

- 写操作使两个指针在下个时钟保持相等,即FIFO满,这时会发出fifo_full信号

- 使读操作使两个指针在下个时钟保持相等,即FIFO空,这时会发送fifo_empty信号

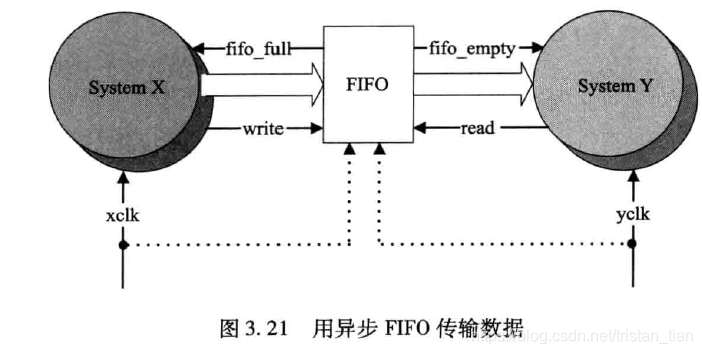

使用异步FIFO

异步FIFO用来在两个异步时钟域建传输数据。它用于对性能要求比较高的设计中,尤其是时钟延时比系统资源更为重要的环境中。

异步FIFO的工作原理:原理上,与同步FIFO的区别在于读写数据工作在不同时钟域下。(与握手信号不同,异步FIFO用于性能要求较高的设计中,延迟比系统资源更为重要)

异步FIFO的工作原理:原理上,与同步FIFO的区别在于读写数据工作在不同时钟域下。(与握手信号不同,异步FIFO用于性能要求较高的设计中,延迟比系统资源更为重要)

- 避免使用二进制计数器,使用格雷码同步实现指针;

由于指针与各自的时钟同步,而彼此的之间异步,使用二进制计数器实现指针,可能会导致用于比较的指针值取样错误。(比如从FFF->000所有位都会发生改变,所以本次采用格雷码进行操作)

- 数据指针如何在不同时钟域传递

(1)xclk的写指针(二进制)->gray 码 ->经过同步器 ->读写指针比较是否产生“写满”状态

(2)yclk的读指针(二进制) ->gray码 ->经过同步器 ->读写指针比较是否产生"读空"状态

- gray码的读写指针如何比较产生读写状态

判断读空时:需要读时钟域的格雷码rgray_next和被同步到读时钟域的写指针wp每一位都相同。

判断写满时:需要写时钟域的格雷码wgray_next和被同步到写时钟域的读指针rp高两位不同,其余各位完全相同。

时钟分频器

偶数分频器

偶数分频器可以用摩尔型状态机或者计数器很容易实现。

奇数分频器

也可以使用与偶数分频相同的方法,但是无法产生50%占空比的输出(比如7分频)。

产生具有50%占空比的奇数分频时钟最简单的方式是以输出频率的一半生成两个正交相位时钟(两个时钟之间有90度相位差),然后将两个波形异或得到输出时钟(以N=3为例)

- 产生两个6分频且相位差有90度的时钟(一个使用上升沿产生6分频信号,一个使用下降沿产生6分频信号)

- 对两个时钟进行异或处理,产生3分频目标时钟

重点:

(1)上升沿在计数值为0时翻转

(2)下降沿在计数值为(N+1)/2时翻转

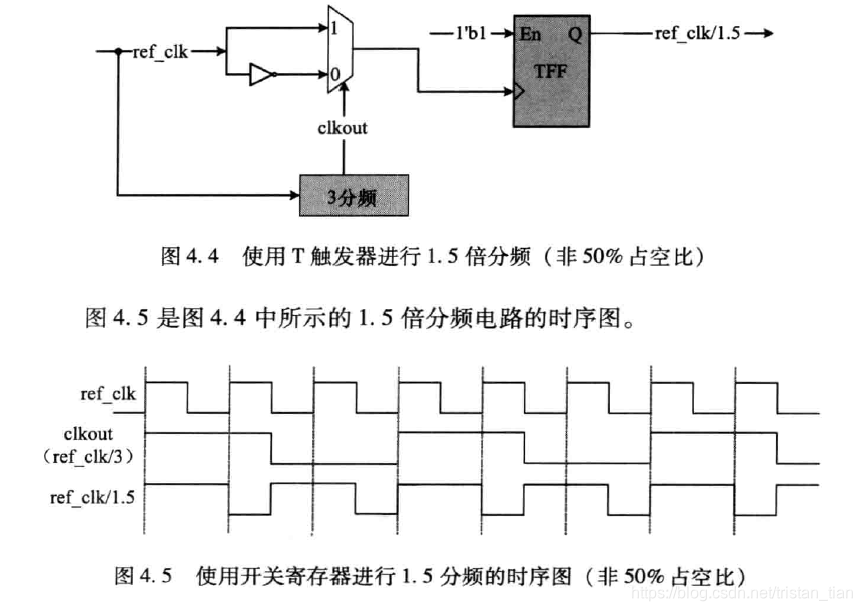

分整数分频

产生1.5倍的分频时钟

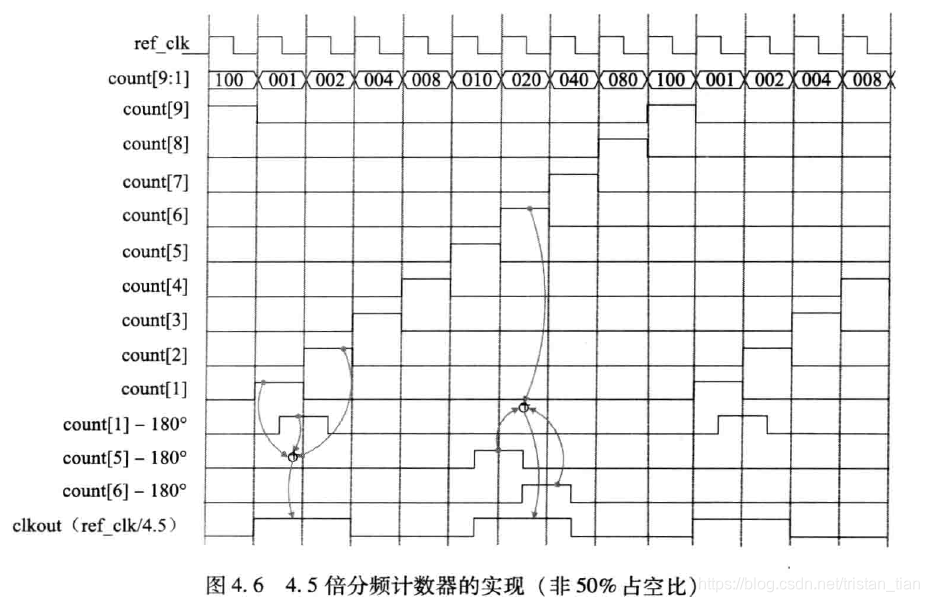

产生4.5分频时钟

使用移位寄存器产生4.5倍分频的实现(非50%占空比),对非整数分频电路进行优化,使输出时钟不含毛刺

(1)使用复位值为000000001的9位移位寄存器,在时钟上升沿使移位寄存器循环左移一位。

(2)产生4.5倍分频的第一个脉冲,将在半周期移位第1位并将之与第1位与第2位进行或操作(占空比40%)

(3)产生4.5倍分频的第二个脉冲,第5位和第6位在半周期时移动并与第6位进行或操作

445

445

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?