1.同步电路和异步电路

同步电路:顾名思义,就是保证保持同一个时刻。就是在同一个时钟的上升沿或者下降沿去处理数据。(即同时的去处理数据)

异步设计:电路没有统一的时钟,即不是所有的触发器都同时处理数据。

在日常设计的时候,肯定是不止一个时钟的,因此全局的同步是不可能的,所以需要在设计的中需要保证在一个时钟域中是同一个时钟(时钟源)

2.行波计数器

2.1行波计数器的特点

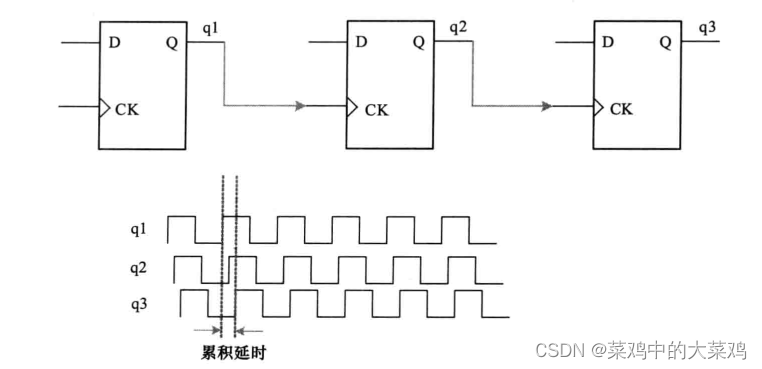

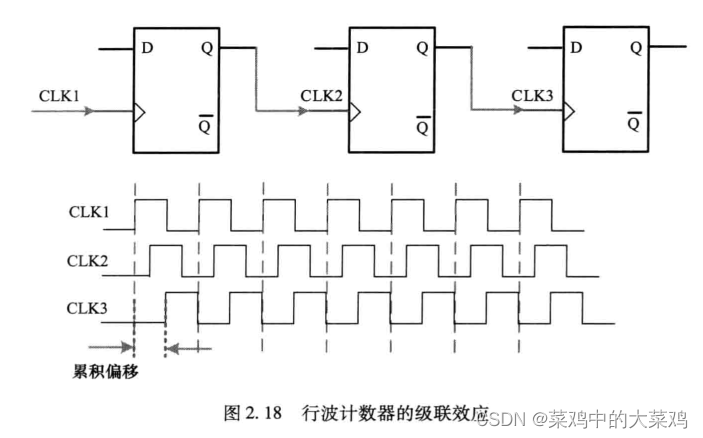

行波计数器:把上一个触发器的输出,作为下一个触发器的的时钟,会存在问题。即CKt o Q是存在延时的,从而会导致延时的累积。在实际使用中,如果这个延迟累积到能一个时钟周期,那不能使用这种方法。

这种异步计数器和同步计数器的区别也就是时钟的区别。行波计数器时常用在时钟进行幂为2的分频上,这种方式相比较同步技术的优势在于门数更少。但是会增加延迟。

2.2行波计数器的应用

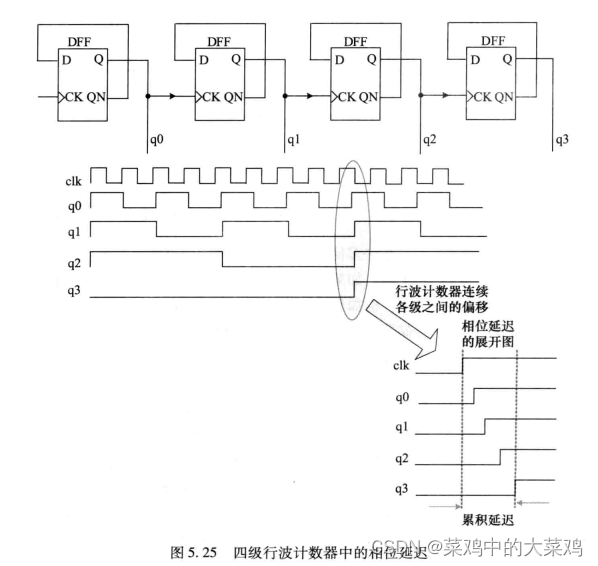

在《硬件架构的艺术》提到了这种方式会影响STA和DC,所以应该尽量避免这种结构。但是在低功耗设计中会使用到行波计数器。这是一个有四个触发器组成的四位等效计数器。

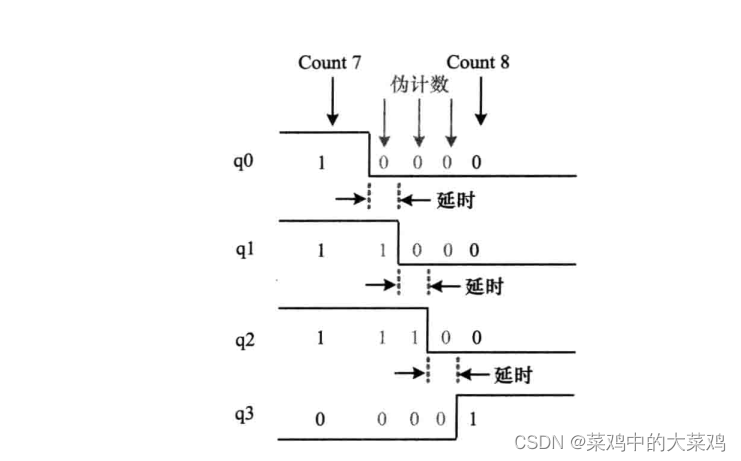

可以看到延迟的累积过程,因为有着延迟,所有再出现正确的值之前会出现一些错误值,虽然很快会消失,但是会有影响。这个影响就要看具体的应用需求了,在led中,这是可以接受的。下面这张图就可以看到延时过程中数据的错误。

以这个行波计数器为例,他一个触发器的verilog可以表示为

reg Q;

wire D;

reg QN;

always@(posedge clk or restn)

if (resetn) begin

Q <= 1'b1;

QN <= 1'b1; //这个示意图上没有 我自己加的

end

else begin

Q <= D;

Qn <= !D;

end

assign D = Qn;2.3行波计数器的改进

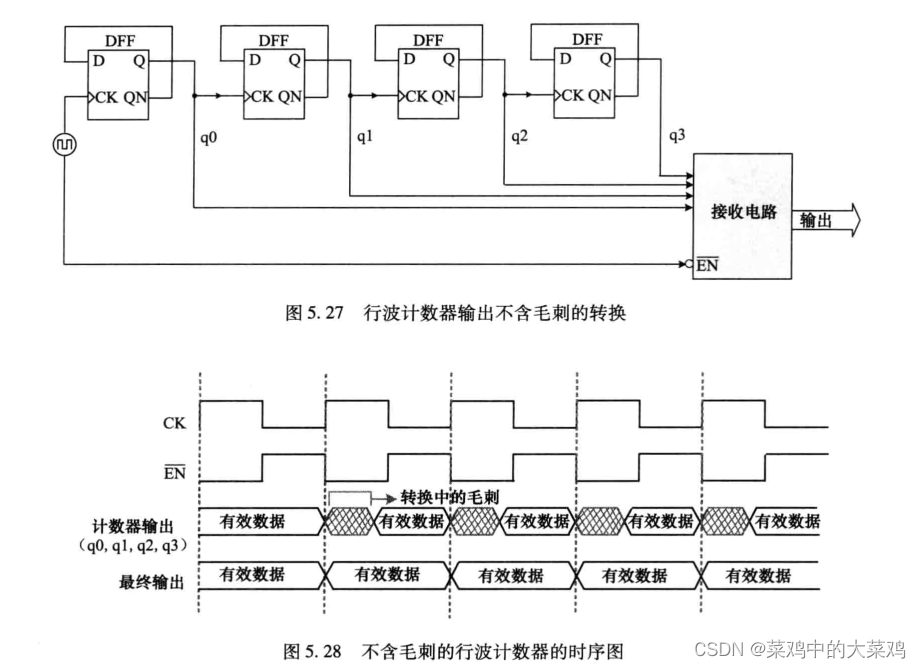

这下面是一个改进方法,就是加一个低使能信号。因为计数电路是上升沿触发的,计时开始于时钟从低到高的过程中。 而这个使能信号是为了在时钟的脉冲为低的时候,接收电路才会开启。给与了行波回到了安全稳定状态的时间。注意这个时钟的1/2时间需要大于最大的行波周期时间,否则留给保持稳定的时间不够,还会出现毛刺

473

473

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?