硬件架构的艺术第五、六章

低功耗设计

功耗源

浪涌、静态功耗和动态功耗是主要的三个功耗源。

- 浪涌: 涌电流指器件上电时产生的最大瞬时输入电流,在应用中称为启动电流。浪涌电流与设备有关(不同设备的浪涌电流是不同的),例如基于SRAM的FPGA有很突出的浪涌电流,因为上电时这些器件没有配置,所以需要从外部存储器中下载数据来配置其编程资源(如布线连接和查找表)

- 静态功耗: 关断主电源或系统进入待机模式下产生的电流,由此电流产生的功耗称为待机功耗。这同样与电气特征密切相关。静态功耗也包含电路中由晶体管的漏电流所导致的功耗。

- 动态功耗:门电路输出切换时,由逻辑转换所引起的功耗。

动态功耗=翻转次数 * 门寄生电容 供电电压的平方时钟频率

而ASIC的总功耗为静态功耗+动态功耗

在各设计抽象层次降低功耗

降低功耗应当在所有的设计层上进行。即,系统级,逻辑级和物理层。层次越高越有效。

系统级低功耗技术

在系统设计之前,必须对系统及其性能以及功耗作为目标进行考虑。

片上系统

由于I/O使用比芯片内核逻辑更高的电压供电(typical value 3.3v),使得其占到总功耗的50%以上。所以如果整个系统包含多个芯片,这些芯片的连线就会消耗大量的功耗。这些方法主要关注降低功耗,缩减面积以及降低成本的方法。

硬件/软件划分

系统的设计首先从性能规范开始,决定系统哪些部分使用不同的方法实现,有些使用硬件(verilog),有些使用软件(C语言)。

系统的设计首先从性能规范开始,决定系统哪些部分使用不同的方法实现,有些使用硬件(verilog),有些使用软件(C语言)。

还可以使用基于模型的方式,模型要么完全自己建立要么使用已复用的已有模型库,随着库的增加,可以缩短设计时间。

低功耗软件

就是修改应用软件来降低功耗。

比如合并循环等

选择处理器

处理器的选择会对整体功耗产生明显影响。

- 选择合适数据宽度的处理器

例如:使用8位的微控制器来处理16位数据会增加大量排序;对于16位乘法,使用16位处理器需要30条指令(加与移位),而使用8位处理器则需要127条指令;而更好的结构是使用乘加单元(MAC)或16*16位并行乘法器用一条指令执行乘法。 - 选择节省功耗的系统体系结构

使用节省功耗的系统体系结构,利用微处理器进行控制,同时用协处理器或DSP(Digital Signal Processor)进行数据处理(使任务在最小且能耗最高的机器中完成),大多数情况下,微控制器和协处理器不会并行运行。

体系结构级降低功耗

高级门控时钟

- 组合门控时钟

在输出不变时使触发器的时钟失效,所以它可以降低5%~10%的动态功耗(在插入门控时钟之前和插入之后电路的功能并没有改变,所以可以用一致性检查工具进行验证)

- 时序门控时钟

时序门控时钟能减少连接到带有门控时钟的寄存器块的设计部分的冗余切换(在不影响设计功能的情况下改变设计结构,由于需要多余逻辑,不适用于多位宽的情况

DVFS

在对频率不敏感的应用阶段中降低时钟速率和供电电压,可以在性能适度损失的情况下大幅度降低功耗(但是降低供电电压会降低系统的性能,所以需要作出权衡,而对于一般应用,一般只在很小的时间中需要高性能,而在其余的大多数时间中使用低性能、低功耗的处理器就足够)。现在也有功耗关系芯片控制。

注意:在实时嵌入式系统中,往往不能直接使用DVFS算法,因为改变处理器的操作电压将会影响到任务的执行时间并违反时效性要求(也可以将DVFS合并到OS调度程序和实时嵌入式系统任务管理服务中)

基于缓存的系统体系结构

对大多数DSP,FFT算法要求频繁访问系统存储器的数据,可以在系统存储器或RAM和处理器之间增加缓存。

对数FFT体系结构

对于大规模运算的应用,使用对数系统(LNS)比使用线性系统更好,LNS在降低平均位元活跃度的同时用加法和减法实现乘法运算,使其效率比线性系统更高,因此可能节省大量功耗。负面影响是加法器和减法器的宽度会增加-导致需要以指数级增大的查找表。

异步(无时钟)设计

传统的设计方法会形成大规模时钟树。可能存在时钟偏移,需要增加额外的电路。

其中两个模块使用握手接口进行交互:(由于未工作元件几乎不消耗能量,所以异步电路的动态功耗接近0)

异步电路基于依赖延迟不敏感编码,双轨道编码用两根线传输每个数据位(单轨只使用一根线传输每个数据位)。“LL”=”无数据“,”LH"=“0”,“HL"=“1”,“HH”=无效。这里L="0"且H=“1”.

异步电路基于依赖延迟不敏感编码,双轨道编码用两根线传输每个数据位(单轨只使用一根线传输每个数据位)。“LL”=”无数据“,”LH"=“0”,“HL"=“1”,“HH”=无效。这里L="0"且H=“1”.

电源门控

电源门控通常指在芯片上加入开关以根据应用要求选择性切断供电电源

1、细粒度电源门控

在每个门和地之间存在一个开关晶体管

2、粗粒度电源门控

创建一个电源开关网络,各组开关晶体管能并行地将整个模块打开或关闭。

多阈值电压

多单元库(包含至少两组功能相同但阈值电压不同)有助于处理漏电和动态功耗的问题。高阈值电压单元较慢但是漏电较少;相反,低阈值电压单元更快但是漏电较多。

多电压供电

在多电压供电(MSV)设计中,设计可以分割为独立的”电压域”,根据每个区域对时序的要求而使用不同的供电电压。

存储器电源门控

在经典的SoC中,SRAM消耗了总功耗的1/3。

- 使用多个小存储器(一小部分存储器常开)

- 基底偏压存储器(提高了阈值电压并降低了漏电功耗)

- 使用多模式给存储器供电(在读写时,存储器使用全电压供电;在存储器不需要读写,降低供电电压,只需保持数据不丢失即可)

在寄存器级传输降低功耗

在大规模ASIC中,在RTL完成时至少80%的功耗已经确定。

状态机编码和解码

在各种状态机编码类型,格雷码是最适合低功耗设计

1、格雷码每次只有一个触发器变化,消耗能量小。

2、格雷码消除了依赖于状态的组合等式中存在毛刺的风险。

二进制数表示法

在大多数应用中,用补码来表示二进制数往往比有符号数更常用。然而对于某些只使用积分器进行求和的应用,补码表达法在0到1的转变发生所有位都会发生变化(有较高的开关功耗),相比之下,有符号数只有两个位发生变化

门控时钟基础

独热码多路器

如果MUX的每个输入都是多位总线,就会产生明显的开关过程,由此产生功耗。如果使用独热码方式,输出就会更快、更稳定,而且在初期就能将未选中总线掩藏,实现低功耗效果。

如果MUX的每个输入都是多位总线,就会产生明显的开关过程,由此产生功耗。如果使用独热码方式,输出就会更快、更稳定,而且在初期就能将未选中总线掩藏,实现低功耗效果。

除去多余的转换

如果转换后的数据未被真实采样,那么它就是多余的,将这样的转换去掉显著可以降低功耗。

例如,如果load_out没有置位,那么前面的操作都是多余的,浪费了能量。

如果load_out没有置为有效,那么load_op也不应置为有效,这样可以节省一部分功耗;仅当sel 为0时才读入A和B,而仅当sel 为1才读入C和D

如果load_out没有置为有效,那么load_op也不应置为有效,这样可以节省一部分功耗;仅当sel 为0时才读入A和B,而仅当sel 为1才读入C和D

新增一些逻辑门,用来取消未选择的总线分支的转换,这些逻辑门会增加一些功耗,但保证了只有最终选中的目标才有数据切换发生,这样就降低了功耗

新增一些逻辑门,用来取消未选择的总线分支的转换,这些逻辑门会增加一些功耗,但保证了只有最终选中的目标才有数据切换发生,这样就降低了功耗

资源共享

如果有同样的操作在多处使用,必须避免相应的运算逻辑在多个位置重复出现。这可以减小面积和功耗。

使用行波计数器来降低功耗

总线翻转

在当前数据和下一个数据之间的汉明距离大于N/2时,就要将一下个数据反向后传输,以减少总线上出现转换的位数量。

高度活跃网络

将活跃度较高的网络和较低的区分开开,置于逻辑云中尽可能深的位置。

寄存器级别降低功耗

- 技术水平:先进硅处理技术。

- 版图优化: 直接关联的模块在硅片上都应该紧密连接在一起。

- 衬底偏压:衬底偏压减少漏电功耗。采用这种技术,可以将衬底电压偏置,以提高晶体管阈值,因此减小漏电。

- 减少氧化层厚度:降低与阈值电流

- 多氧化层器件:

- 利用订制设计减小电容:

流水线的艺术

对于ASIC,可以通过流水线提高吞吐量,但是也会带来系统延时和面积的增加。流水线通过在较长的组合逻辑中插入寄存器降低组合逻辑的延迟,来提高时钟频率并提高性能。

组合路径延迟为X个时间单位,在下图中通过插入三个寄存器被分割为多个小块,寄存器间的延迟为Y个时间单位,Y<X ;加入寄存器时钟频率明显增加,但是同时也增加额外的开销,并且增加了系统的延迟。

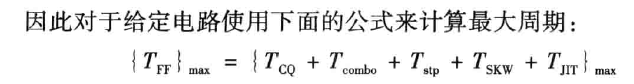

影响最大时钟频率的因素

时钟频率是数据流入西太后在输出端出现的速率。

对于没有任何抖动的理想时钟,时钟信号同时到达两个寄存器模块。

对于没有任何抖动的理想时钟,时钟信号同时到达两个寄存器模块。

时钟偏移

在实际电路中,由于存在线路上的传播延迟,寄存器B的时钟输入相对于寄存器A可能会有一些延迟,这种现象称为“时钟偏移”,在相邻两个寄存器的时钟延迟大于这两个寄存器之间的数据路径延迟,就会产生负时钟偏移。这种情况下,先到的时钟会引起竞争条件(即数据还未成功锁存,时钟就触发了寄存器)。

时钟抖动

到达电路中某一点的连续时钟边沿之间间隔的变化称为时钟抖动。

我们计算从寄存器bf到输出o之间的精确的组合延时。

我们计算从寄存器bf到输出o之间的精确的组合延时。

组合延迟部分可以通过添加多个触发器来减小,来增大电路的最大频率。

组合延迟部分可以通过添加多个触发器来减小,来增大电路的最大频率。

流水线

流水线使用存储器件将时钟周期内关键路径(最大组合延迟的路径)分割开来。减小了关键路径上各阶段延迟并使电路以更高频率工作。但是使用并行电路进行同样的k次操作,比重复使用某一逻辑k次在面积和功耗方面的开支更大,因为使用了更多的触发器和额外逻辑,导致了更多的连线。

流水线的延时是从数据进入流水线的输入端到这些数据经过处理后从流水线的输出端输出所小号的时间。

流水线的延时是从数据进入流水线的输入端到这些数据经过处理后从流水线的输出端输出所小号的时间。

对于非流水线电路的延时:

对于非流水线电路的延时:

Tlatency = Tcomb + Tregister +Tclk

Tregister(寄存器开支) = Tcq + Tstep

Tclk(时钟开支) = Tskw + Tjit

而插入流水线后,延时最大的流水器阶段决定时钟周期:

Tpipeline=max{Tcomb} + Tregister +Tclk

而最终系统的延迟:

而最终系统的延迟:

T=n*Tpipeline =Tcomb+n(Tregister + Tclk)

注意:在使用流水线会引入额外的开销,如时钟偏移和寄存器延迟,限制了流水线所能达到的加速值

DLX指令集的实现

DLX是新兴学院派指标结构的理论32位RISC微处理器,每条DLX指令最多由5部分组成,最多用5个时候周期完成。

指令获取(IF)

IR < = MEM[PC]

NPC < =PC+4

操作:

1、从存储器获取指令并放入指令寄存器(IR)

2、IR保存下个时钟周期所需指令

3、PC值递增4,指向下一个指令地址

解码(ID)

A<=Reg[IR6...10]

B<=Reg[IR11...15]

IMM<={[IR16]16IR16...31}

操作:

1、分析IR中的指令并访问寄存器堆以读取寄存器

2、将通用寄存器的输出读入两个临时寄存器A和B

3、IR的高16位经过符号扩展保存到临时寄存器IMM中供以后使用

执行(EX)

ALU对上一个时钟周期准备好的操作数进行操作,根据DLX指令的类型进行下面一个功能的一个:

- 访问存储器

操作:ALU通过加法形成有效地址,并将结果放入寄存器ALUoutput中 - 寄存器-寄存器ALU指令

操作:根据操作码对寄存器A和B的数值进行操作,把结果放在临时寄存器ALUoutput中 - 寄存器-立即数ALU指令

操作:根据操作码对寄存器A和IMM的数值进行操作,把结果放在临时寄存器ALUoutput中 - 分支指令

操作:ALU计算出分支的目标地址,检查寄存器A的值来决定是否进行分支

储存器访问(MEM)

- load:从存储器中返回的数值存入LMD寄存器中

- store:将寄存器B写入存储器

写回(WB)

- 寄存器-寄存器ALU指令

- 寄存器-立即数周期

- 取指令

操作:将结果写回寄存器堆中,结果可能来自存储器或者ALU

流水线对吞吐量的影响

引入流水线时会带来额外的开销,需要控制。

引入流水线时会带来额外的开销,需要控制。

流水线冒险

(1)结构冒险:由于资源冲突而使硬件无法支持所有的指令组合同时执行

(2)数据冒险:指令执行需要之前指令的计算结果,而这个结果在流水线还没有计算出来

(3)控制冒险:分支的流水线和其他指令改变程序计数器的值

(4)存储器的冒险

通用方法:停止流水线,阻塞。

98

98

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?