矩阵乘法包含大量的a+b*c类运算,因此常在运算中将乘法器和加法器合成一个计算单元,进程乘法累加操作,这个单元被称为MACs(multiply and accumulate operations.MAC).乘法运算是数学中重要的基本算术运算,乘法累加操作在数字信号处理中被广泛应用,比如,FFT,DFT,卷积计算,甚至是微控制器的ALU中的通用计算单元都能见到它的身影。在DSP应用中,比通用处理器更加侧重MACs的设计,MACs的逻辑实现通常是数字电路设计中Critical path的主要贡献方,设计的好坏决定了PPA,本文试图从软件视角搞清楚MACs是什么以及如何工作的。

设计原理

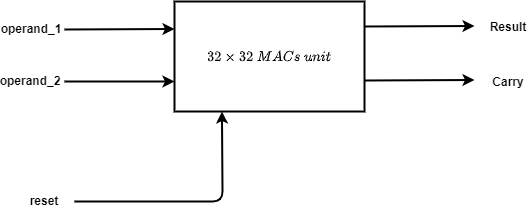

MACs顶层实现方框图如下,其中的operand_1 和 operand_2是32位输入操作数,MACs操作的结果通过64位的Result pin输出,内部的64位加法器将乘法器的输出作为第一个操作数,与存储在内部的第二个加法操作数相加,第二个操作数的来源一般是上一个周期的Result结果,得到Result输出和进位信号Carry,这里的32x32表示两32位输入的MAC,并非是乘法,也并非代表个数,如果N个这样的MAC,一般表示为N*32x32MAC.

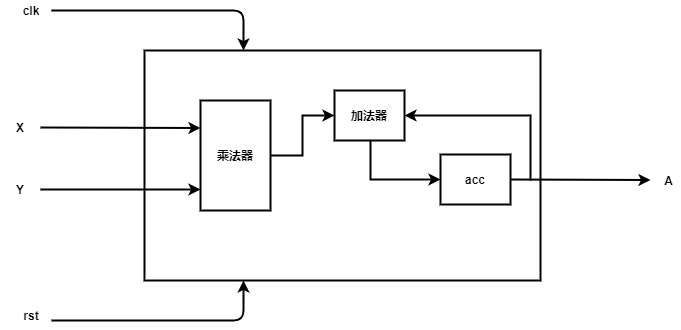

MAC内部结构:

一个用VHDL实现的MACs单元逻辑:

1 LIBRARY ieee;

2 USE ieee.std_logic_1164.ALL;

3 USE ieee.numeric_std.ALL;

4

5 ENTITY mac IS

6 GENERIC (n : INTEGER := 4); --define X and Y size

7 PORT (

8 ck : IN STD_LOGIC;

9 rst : IN STD_LOGIC;

10 X : IN SIGNED (n-1 DOWNTO 0); --n

11 Y : IN SIGNED (n-1 DOWNTO 0); --n

12 A : OUT SIGNED ((2+2*n)-1 DOWNTO 0) --2+2n (include two leading bits for overflow)

13 );

14 END mac;

15

16 ARCHITECTURE hdl OF mac IS

17 SIGNAL acc : SIGNED ((2+2*n)-1 DOWNTO 0) := (OTHERS => '0'); --2+2n

18

19 BEGIN

20

21 PROCESS (ck)

22 BEGIN

23 IF rising_edge(ck) THEN

24 IF rst ='0' THEN --reset accumulator at low

25 acc <= (OTHERS => '0');

26 ELSE

27 acc <= acc + shift_left(X * Y, 1);

28 END IF;

29 END IF;

30 END PROCESS;

31

32 A <= acc;

33 END hdl;

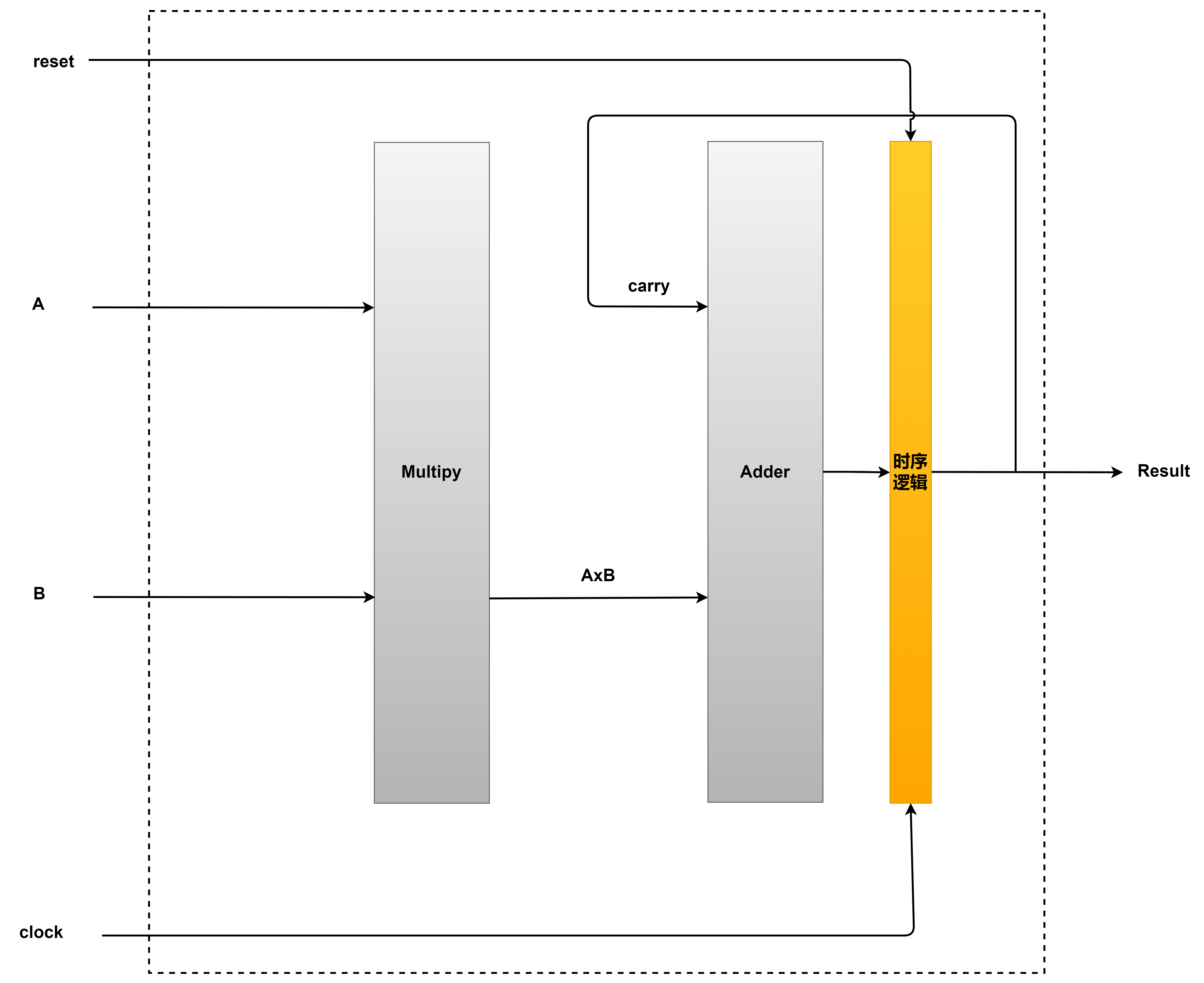

这段代码对应的电路逻辑如下图所示,acc作为输出的同时,又通过一条反馈回路喂给加法器,作为其中一个操作数进行下次累加计算,所以叫做累加器-MACs.

值得一提的是,如上VHDL代码反应的时序逻辑中,乘法和加法属于组合逻辑部分,计算部分不需要时钟控制,MAC乘加运算计算完成后的结果需要保存在寄存器中,也就是下图中黄色的部分,这一步才用到时序逻辑保存中间结果,所以时钟信号和复位信号指向从时序逻辑这里输入。

Vedic Multiplier 电路实现

数字电路的设计中,内蕴了深刻的递归和同构的思想,当问题在不同层面具有相同的结构时,可以通过将复杂问题逐层递归分解,找到最小的问题可解决结构,再最小结构层面上把问题解决,然后再以此为基础,再按照分解的逆向过程逐步解决高层问题,最终得到整个问题的解,同样道理,构造,可以从最简单的

乘法器开始构造。

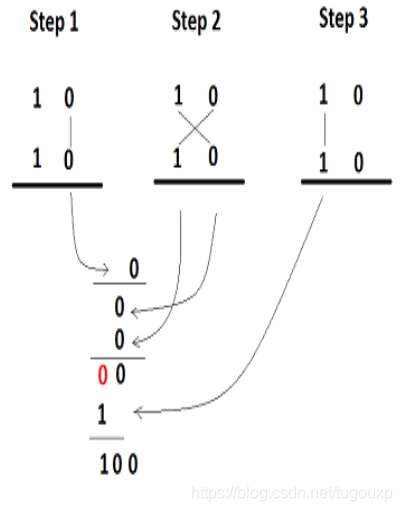

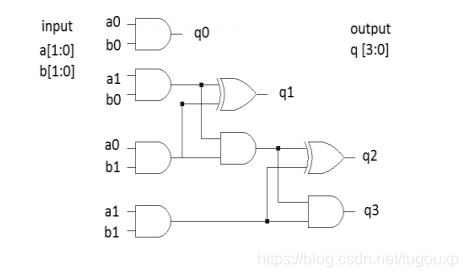

采用Vedic算法的乘法器原理如下:

对应的数字电路实现如下图所示:

基于 multiplier,可实现

的verdic multiplier

基于 multiplier,可实现

的verdic multiplier

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?