之前的工作中对C-Model有过简单接触,当时的情况是在客户现场遇到一个视频解码问题,简单描述就是一段码流经过VPU解码后,显示出来的画面有一点儿轻微马赛克,当时不确定是码流问题还是VPU IP内的解码算法问题,后面对比了样机表现,发现样机OK。于是基本确定问题发生在VPU算法上,VPU是当时的东家设计的,于是就把码流拿回去请专家分析。专家很快就给出了分析结果以及解决方案,至于为何这么快,后来才了解到,专家把码流在CModel上跑了一遍,很快复现到问题,后面解决问题也水到渠成了。

虽然用过,但理解不深,只是大概猜测可能是因为视频解码逻辑本身是一个确定性问题,随机性不发生影响,所以可以用按照VPU IP 算法同样的设计编写的C 代码来解同样一笔数据,由于算法本身是一样的,所以无论是在芯片上跑还是在CMODEL上跑,结果都是一样的,都可以说明问题。

直到看到一篇文章,对这个过程的理解加深了一层,简单写下自己的理解。

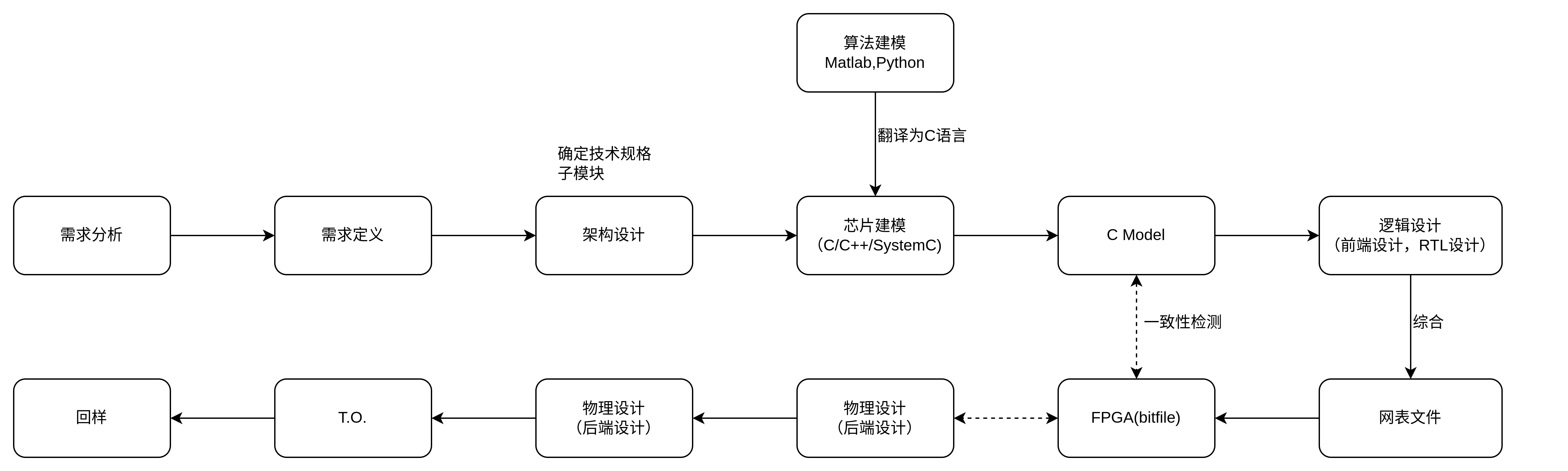

一颗芯片芯片设计过程从端到端的角度理解,流程如下

在芯片的架构设计阶段需要对芯片进行建模,建模的主要目的是在大规模投入人力之前先用低成本的计算机软件实现目标芯片的主要功能,评估芯片的工作效果,验证设计思想,并作为后续开发活动的标准和依据。从这个意义上说,C Model的开发团队是芯片设计团队的先锋队,需要承担逢山开路、遇水搭桥的光荣任务,为后续大部队扫清前进通路上的障碍。

不同的项目对C Model的功能定位可能会有很大差别,一般而言,C Model的功能定位可能会有以下几种:

1. 作为算法模型的C版本,定义模块输入输出行为的标准,实现数据的bit-match;

2. 在1的基础上,定义模块的内部结构和资源约束;

3. 在2的基础上,精确定义模块的输入输出时序,实现cycle-accurate;

第一种定位可以理解为C Model的初级阶段,它要解决的问题是算法级的,目标是保证未来RTL代码的输出数据能够与C Model做到bit-match,并以此作为评估RTL代码正确性的验收标准。在芯片进行FPGA验证阶段,需要编写自动化测试脚本,将FPGA实跑的结果与C Model输出的golden sample进行比对,每个模块至少比对十万个golden数据才达到验收通过标准。

在算法层面上,我们会认为C Model与Matlab/Python算法模型是等价的,那么如果RTL代码与C Model以 bit-match的方式实现了等价性(equivalency),则有理由认为RTL与算法模型也是等价的。

一般而言,本阶段C Model需要解决的主要问

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

637

637

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?