特定用途的半导体芯片研发流程

1.ASIC设计流程

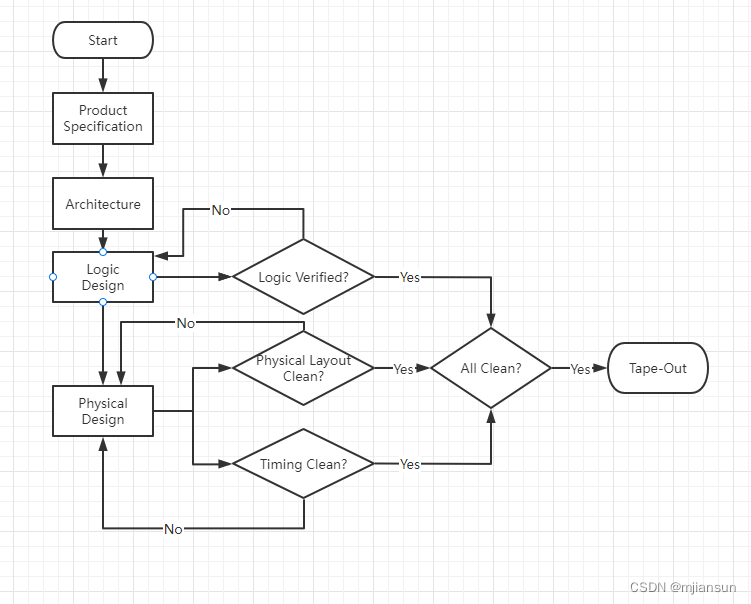

图1 工作流程图

主要分为4个部分:

(1)Product Specification:产品需求规格定义。

(2)Architecture:架构设计,输出成果是一个正式的架构设计文档和一套C模型。

(3)Logic Design:逻辑设计,一般称为ASIC前端设计,常用的逻辑设计工具有Verilog, VHDL, System Verilog等硬件描述语言,输出的代码称为RTL(Register Transfer Level)代码。

(4)Physical Design:物理设计,ASIC后端设计。物理设计的任务是将逻辑设计映射为具体的物理器件。

1.1架构设计--算法设计流程

算法团队的主要使命有两个,一是跟踪行业的技术发展动态,了解掌握前沿技术,二是针对公司的具体项目输出合适的算法模型,保证产品的技术先进性。

1.2架构设计--C Model设计流程

前面已经提到,在芯片的架构设计阶段需要对芯片进行建模(modeling),建模的主要目的是在大规模投入人力之前先用低成本的计算机软件实现目标芯片的主要功能,评估芯片的工作效果,验证设计思想,并作为后续开发活动的标准和依据。从这个意义上说,C Model的开发团队是芯片设计团队的先锋队,需要承担逢山开路、遇水搭桥的光荣任务,为后续大部队扫清前进通路上的障碍。

不同的项目对C Model的功能定位可能会有很大差别,一般而言,C Model的功能定位可能会有以下几种:

1. 初级阶段:作为算法模型的C版本,定义模块输入输出行为的标准,实现数据的bit-match;

在本阶段中,C Model只关注输出结果的正确性,但并不关注资源利用率和时序等性能问题。

2. 中级阶段:在1的基础上,定义模块的内部结构和资源约束;

C Model的设计者需要更多地站在RTL工程师的角度思考问题,每个模块预留多大的cache,每个处理周期读取多少行数据,数据对齐的规则如何定义,读数据和处理数据如何实现并行化,模块与模块之间如何进行数据同步,模块的寄存器接口如何定义,出错之后如何恢复,等等。

以ISP为例,真实的ISP硬件在处理图像时一定是以行为最小处理单位的,并且ISP内部各个子模块之间一定是并行工作的,不会出现一个模块处理图像,九个模块围观的搞笑场景

3. 高级阶段:在2的基础上,精确定义模块的输入输出时序,实现cycle-accurate;

精确定义一个模块的时序,以支持软件仿真的用途。和硬件的工作原理类似,这种C Model在架构上需要支持clock和状态机的概念,每个clock会触发所有函数体执行一遍,而函数体内部则是触发一次状态机的翻转,经过若干个clock的触发后,模块就完成了一轮数据的处理。显然,如何安排每个clock的工作量是一个比较棘手的任务,如果设计得不合理,则翻译成RTL代码后很容易违反时序约束,此时必须回头修改C Model以及RTL实现,所以这种C Model的设计会与RTL设计进行多次迭代,直到符合硬件的时序约束才算完成。

1.3逻辑设计--SystemC

传统的ASIC设计流程是先开发C Model,确认模型效果后由RTL工程师手动将C Model转成Verilog或VHDL语言。对于cycle-accurate C Model而言,C Model本身的有效性是不能在PC平台上验证的,只能翻译成RTL之后在EDA平台上验证,以满足物理器件的时序约束。这就涉及在两个系统之间反复迭代的过程,不得不说这是一项相当痛苦的任务。

1999年11月,世界最主要的EDA工具厂商联合一批业内公司推出了SystemC,这是一种面向系统设计的计算机语言,基于C++编写,能够满足对软件和硬件协同仿真的需求,目前已被IEEE组织采纳为IEEE1666-2005标准。

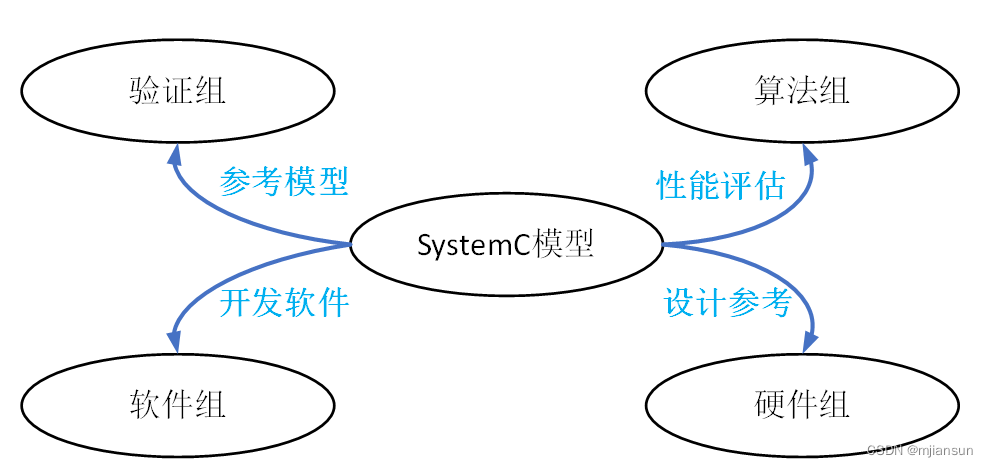

总结:SystemC模型在芯片前端流程中重用度非常高,几乎可以作为各个部门(架构组,算法组,设计组,验证组,软件组)之间的桥梁,使得部门之间的沟通合作更加有效,大大增加工作效率。

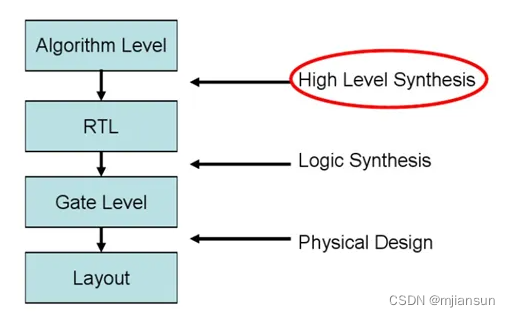

1.4逻辑设计--HLS

VHDL语言诞生于1982年,Verilog语言诞生于1983年,迄今为止它们还是最流行的硬件描述语言,但是人们从未满足于此。几十年来,人们一直在探索将C/C++为代表的高级语言改造为硬件描述语言的可能性,这个研究领域称为高层次综合(High Level Synthesis, HLS)。

6844

6844

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?