实验内容:在basys3中利用数码管制造一个计时器,功能包含:按秒计时,开始,停止,清零操作。

实验目的:了解vivado的工程创建,IP添加等操作

实验环境:windows7,vivado2017.2,basys3

实验步骤(将省略部分简单过程):

1,打开vivado后,点击creat project

2,进入到如下界面后,需定义工程名和工作位置

3,下一界面中选择“RTL Project

”,(RTL即Register Transmit Levl,寄存器传输级

),其他选项用的比较少,暂不讨论。

并勾选“Do not specify sources at this time”,意思是先创建工程,后期再添加文件。也可不勾选。

4,

(1) 如果用的是xilinx生产的板子,则可以点击"Boards"选择相应开发板,这样新建的工程就包含引脚约束等文件,更加方便。

而我们使用的是Digilent的开发板,因此点击“Parts”,并在芯片栏中选择相应型号芯片,如2.

(2) Speed grade:速度等级,其绝对值越大,速度越快,即逻辑延时较低。这是由芯片出厂后测试标定的,速度等级不一样,价格也相差很多。

(3) Temp grade:温度等级,表面该芯片适用的温度范围。注意这里温度值得是FPGA结温,而不是室温。

5,最后就新建好了工程

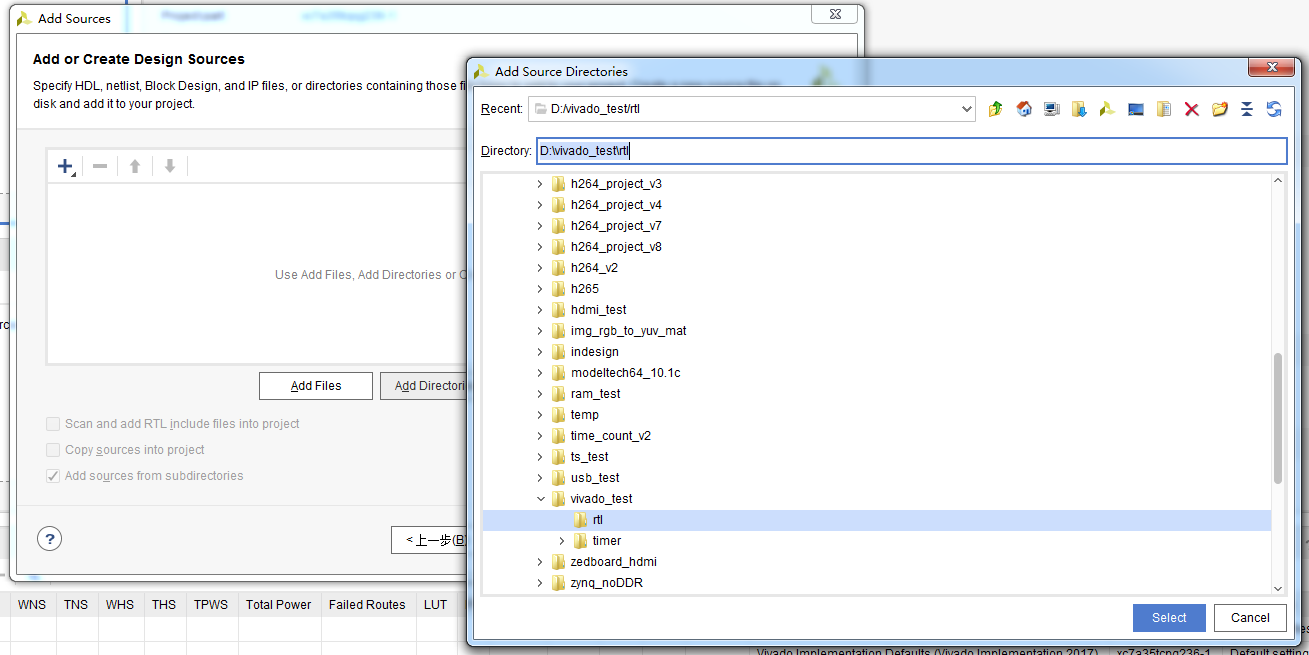

7,然后再接下来的页面中选择要添加的文件或者文件夹,或者创建新文件

8,由于本工程需要用到rom,因此点击左侧“IP Catalog”,在右侧出现的搜索框中搜索“rom”,然后双击选择“Block Memory Generator”

9,接下来对ROM进行配置,完成后会出现如下对话框:

(1) synthesis Options:

Global:每次综合时IP与工程一起综合,耗时较长

Out of context per IP:IP单独综合,工程需要用到IP时,直接使用IP综合出来的网表文件,不需要对IP重新综合。耗时较短。

综上,选择

Out of context per IP。

(2) Run Setting:设置当多线程综合时,参与运算的处理器数。具体日后讨论,保持默认即可。

10,生成后,在“IP Source->IP->num_rom->Instantiation Template”可以看到实例化文件。可将该IP实例化到工程中。

11,完成工程代码编写后,工程会自动检查与非错误,或者右击文件,选择“Refresh Hierarchy”以使vivado检查语法错误。

若有语法错误,则图示几处会给出错误提示。

12,再接下来就是仿真了,本人习惯使用modelsim进行仿真,因此将在下一章中说明如何使用vivado和modelsim进行联合仿真。

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?