电子设计自动化实验 实验五

EDA

一.实验名称:综合性实验五、有限状态机的硬件描述语言设计方法

二.实验目的:

1、 熟悉用硬件描述语言(VHDL)设计一般状态机所包含的几个基本部分;

2、 掌握用硬件描述语言(VHDL)设计 Moore 型和 Mealy 型有限状态机的方法;

3、 了解状态机在信号输出方式、结构方式、状态表达方式和编码方式的差异。

4、 学习用状态机实现序列检测器的设计,并对其进行仿真和硬件测试; 三.实验内容:

1、 说明附件中例 5-11 的代码表达的是什么类型的状态机,它的优点是什么?**

2、 利用 QuartusII 对例 5-11 进行文本编辑输入、仿真测试并给出仿真波形,了解控制信 号的时序;**

3、 对例 5-11 进行引脚锁定并用实验箱完成硬件验证实验,采用 NO.8 电路结构;**

4、 根据例 5-11 写出由两个主控进程构成的相同功能的符号化 Moore 型有限状态机,画 出状态图,并给出其仿真测试波形**。

5、 将 8 位待检测序列数作为外部输入信号,即可随时改变序列检测器的检测序列数。写 出此功能的符号化有限状态机,并用你学号末两位的十进制码进行验证。** 四.例5-11

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY SCHK IS

PORT(DIN,CLK,CLR : IN STD_LOGIC;

AB : OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END SCHK;

ARCHITECTURE BEHAV OF SCHK IS

SIGNAL Q : INTEGER RANGE 0 TO 8;

SIGNAL D : STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN D<="11100101";

PROCESS(CLK,CLR)

BEGIN

IF CLR = '1' THEN Q<=0; ELSIF CLK'EVENT AND CLK='1' THEN

CASE Q IS

WHEN 0=> IF DIN=D(7) THEN Q<=1; ELSE Q<=0; END IF;

WHEN 1=> IF DIN=D(6) THEN Q<=2; ELSE Q<=0; END IF;

WHEN 2=> IF DIN=D(5) THEN Q<=3; ELSE Q<=0; END IF;

WHEN 3=> IF DIN=D(4) THEN Q<=4; ELSE Q<=0; END IF;

WHEN 4=> IF DIN=D(3) THEN Q<=5; ELSE Q<=0; END IF;

WHEN 5=> IF DIN=D(2) THEN Q<=6; ELSE Q<=0; END IF;

WHEN 6=> IF DIN=D(1) THEN Q<=7; ELSE Q<=0; END IF;

WHEN 7=> IF DIN=D(0) THEN Q<=8; ELSE Q<=0; END IF;

WHEN OTHERS => Q<=0;

END CASE;

END IF;

END PROCESS;

PROCESS(Q)

BEGIN

IF Q=8 THEN AB<="1010";

ELSE AB<="1011";

END IF;

END PROCESS;

END BEHAV;五.设计原理:

1.例子5-11

- 分析5-11代码可知,该段代码的功能是,检测一段由8位数字构成的序列。当完整输入该序列时,输出结果“1010”;反之则输出“1011”。在VHDL实体描述部分用作电路模块端口的有四个,下面分析其功能:

CLK:用作时钟,当检测到上升沿到来时,读入由DIN输入的数据。

CLR:用作清零信号,当为高电平时,将系统状态清零,即从Q<=0开始。

DIN:用于输入0和1组成的序列

AB: 用于输出一个4位的数,即"1010"或"1011"同时,在结构体说明部分定义了两个信号,下面分析其功能:

Q:定义了从0到8的整数,共9个。用于描述状态。

D:定义了被检测序列,用于和由DIN输入的序列做对比。2.波形仿真

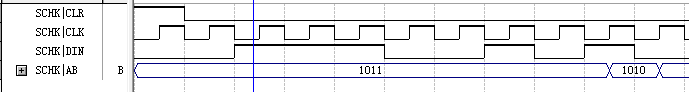

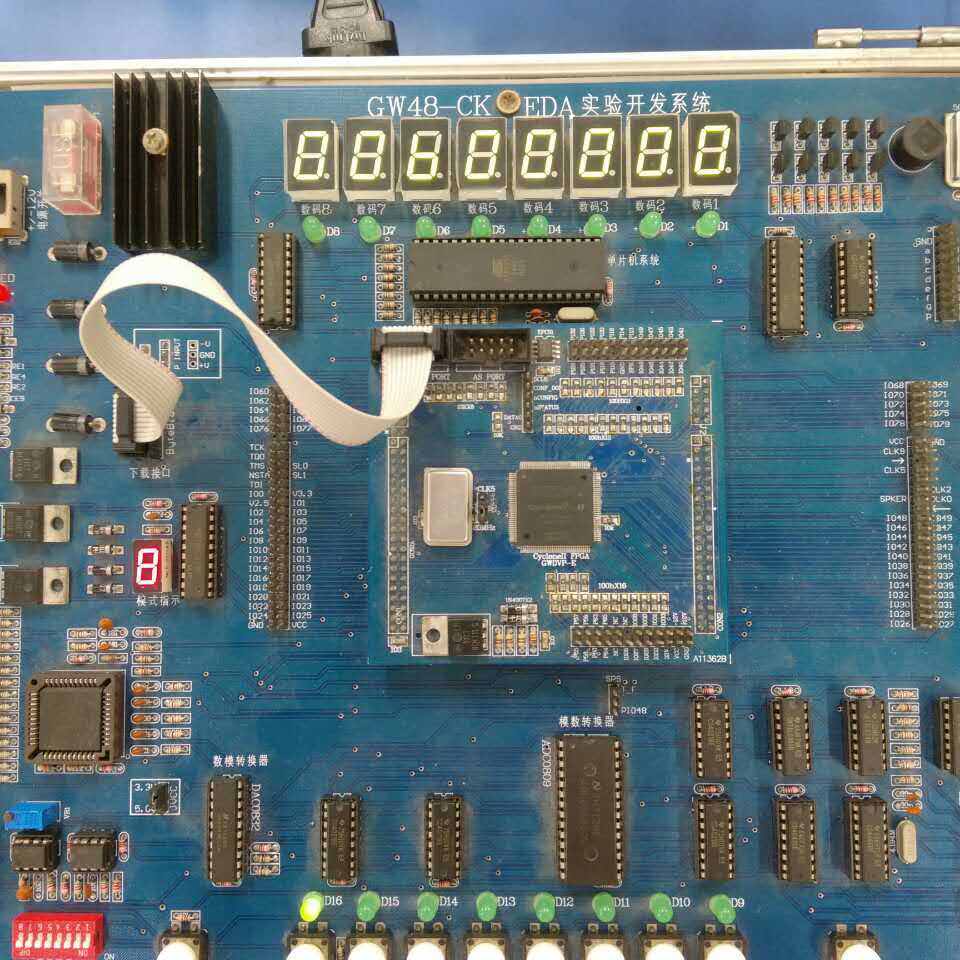

由功能仿真图可以看出,由DIN输入数据,当CLK的上升沿到来时DIN数据,当检测出这个序列式,输出AB从”1011”变为”1010”。

3.硬件实现

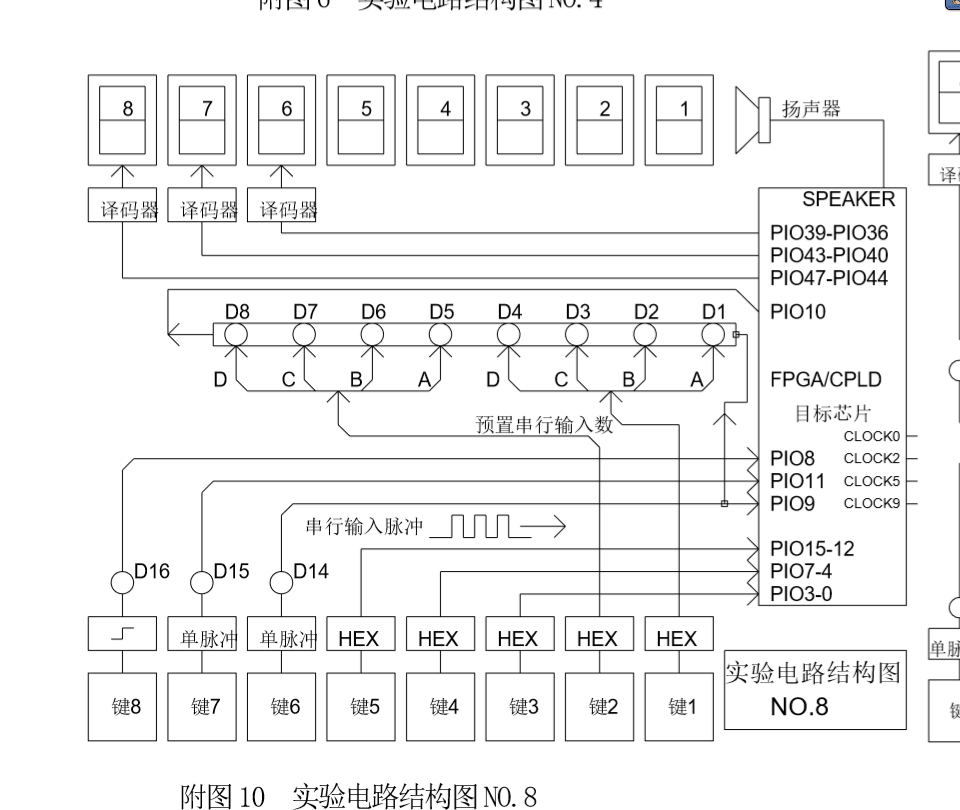

在进行硬件实现时,根据具体的硬件,可将单个输入均接到三个按键上,如下图中的键6~8;输出可接一个带译码器的数码管,如下图译码器6。

在输入数据时,可将DIN所绑定引脚(如键8)置为1,此时CLK按键每按下一次代表一个时钟上升沿,便读入一个1;同理,将DIN置为0时,便可读入一个0。

按下CLR(如键7)时,系统状态清零,不管已输入多少,均清零重新检测。

由于数码管有译码功能,所以在显示时,读入数据或者检测不到正确的数列时显示为’b’(“1011”),检测到正确的数列时即变为’A’(“1010”)。

2.MOORE型有限状态机

将上述例子所实现的功能用由两个主控进程构成的MOORE型有限状态机来设计。

1.代码如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY MOORE_SCHK IS

PORT(DIN,CLK,CLR : IN STD_LOGIC;

AB : OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END MOORE_SCHK;

ARCHITECTURE BEHAV OF MOORE_SCHK IS

TYPE states IS (s0,s1,s2,s3,s4,s5,s6,s7,s8); --定义各状态

SIGNAL ST, NST : states :=s0; --设定现态变量和次态变量

SIGNAL D : STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

COM: PROCESS(ST,DIN) BEGIN --组合进程,规定各状态的转换方式

D<="11100101";

CASE ST IS --11100101

WHEN s0=> IF DIN=D(7) THEN NST<=s1; ELSE NST<=s0; END IF;

WHEN s1=> IF DIN=D(6) THEN NST<=s2; ELSE NST<=s0; END IF;

WHEN s2=> IF DIN=D(5) THEN NST<=s3; ELSE NST<=s0; END IF;

WHEN s3=> IF DIN=D(4) THEN NST<=s4; ELSE NST<=s0; END IF;

WHEN s4=> IF DIN=D(3) THEN NST<=s5; ELSE NST<=s0; END IF;

WHEN s5=> IF DIN=D(2) THEN NST<=s6; ELSE NST<=s0; END IF;

WHEN s6=> IF DIN=D(1) THEN NST<=s7; ELSE NST<=s0; END IF;

WHEN s7=> IF DIN=D(0) THEN NST<=s8; ELSE NST<=s0; END IF;

WHEN s8=> IF DIN=D(0) THEN NST<=s2; ELSE NST<=s0; END IF;

WHEN OTHERS => NST<=s0;

END CASE;

END PROCESS;

REG:PROCESS (CLK,CLR) BEGIN --时序进程

IF CLR = '1' THEN ST<=s0;

ELSIF CLK'EVENT AND CLK='1' THEN ST<=NST;

END IF;

END PROCESS REG;

AB <= "1010" WHEN ST=s8 ELSE "1011";

END BEHAV;当有正确序列进入时,变为状态s8,输出序列AB变为”1010”,而当下一位数据为1时,即DIN=1,进入状态s2。这是因为测出的数据11恰好与原序列数的前两位相同。

波形仿真和硬件仿真均与上例没有区别。

3.具有”记忆”性的序列检测器

在上面两例中,检测器均不具有记忆功能,即若该输入数与检测序列不同时,状态就会被清零,不管前面已输入哪些数。例如上例中,第四位为’0’,而此时如果再输入一个’1’,状态就会被清零,重新开始检测。如果来’1’,状态不清零,而是保持在原状态,等待下一个’0’来进入下一个状态的话。因此,系统便具有”记忆“功能。

要实现以上功能,只需修改一句代码,即为”1”不清零,维持原状态。用例5-11举例。

WHEN 3=> IF DIN=D(4) THEN Q<=4; ELSE Q<=3; END IF; 4.可随时改变检测序列数的检测器

以上三个例子中,检测的数列是固定在程序内部的,无法随时更改。要实现可随时更改待检测的序列,要将固定在程序内部的序列改为由外部输入,将SIGNAL D改为一个输入端口PORT,即在实体定义时加入D的输入端口,同时删除SIGNAL D。

1.代码如下:

ENTITY MOORE_SCHK IS

PORT(DIN,CLK,CLR : IN STD_LOGIC;

D : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

AB : OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

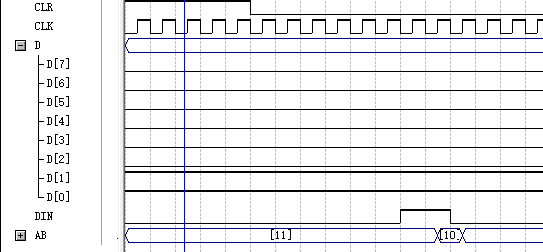

END MOORE_SCHK; 2.波形仿真:

举个例子,输入的待检测序列为’3’(即00000011B)

由图片可以看出,当清零信号为’0’后开始检测序列,当连续输入六个’0’和一个’1’后,系统输入AB从’11’(即1011B)变为’10’(即1010B)。

3.硬件实现:

在硬件实现时,可将外部输入D(8位)绑定到键3和键4,一个按键控制4位。

1287

1287

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?