目录

7 PCU程序控制单元

7.1 概述

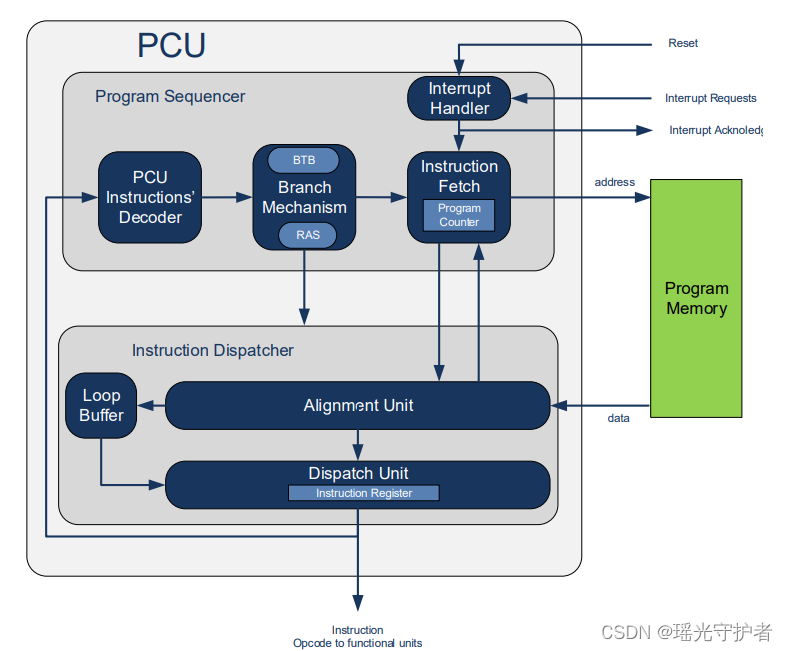

这段文本描述了一个处理器中的程序控制单元(PCU)的功能和结构。以下是对这段文本的详细解释:

程序控制单元(PCU):

程序控制单元(PCU)是处理器中的一个关键组件,它主要负责处理与程序内存相关的接口、从程序内存中获取指令包并进行对齐、将指令分派给不同的功能单元,以及在核心中控制指令包的执行流程。

PCU的功能:

- 从程序内存中获取指令包的操作码:PCU首先会从程序内存中读取指令包的操作码。

- 对齐指令包:由于从内存中读取的指令可能不是完美对齐的,PCU需要对这些指令进行对齐处理,以确保它们可以被正确地解码和执行。

- 识别每个指令所属的功能单元:不同的指令可能需要在不同的功能单元上执行。PCU会识别每个指令,并确定它们应该在哪个功能单元上执行。

- 将指令分派给不同的功能单元进行进一步的解码和执行:一旦确定了指令的目标功能单元,PCU就会将这些指令分派给相应的单元以进行后续的解码和执行。

PCU的组件:

- 指令分派器:它包含以下功能元素:

- 对齐单元:负责将从内存中读取的指令进行对齐。

- 分派单元:负责将指令分派给不同的功能单元。

- 循环缓冲区:可能用于存储循环中的指令,以优化性能。

- 程序定序器:它包含以下功能元素:

- 程序地址生成和指令获取单元(IFU):负责生成程序地址并从内存中获取指令。

- 指令解码器(用于PCU指令):负责解码PCU接收到的指令。

- 分支机制:处理程序中的分支指令,这些指令会导致程序执行流程的改变。

- 分支目标缓冲区(BTB):用于预测分支指令的目标地址,以减少因执行分支而导致的性能损失。

- 中断处理程序:负责处理处理器接收到的中断信号,并根据需要调整程序的执行流程。

有关指令分派器和程序定序器的更多详细信息,可以分别参阅第7.2节和第7.3节。这些部分可能会提供更深入的技术细节和实现方式。

指令获取单元(IFU)生成程序地址总线,该程序地址总线被驱动到程序存储器。为了生成地址,它接收来自指令调度器、中断处理器以及块重复和分支机制的指示。

从程序存储器读取的指令包操作码被加载到指令调度器中,指令调度器将它们对齐并将它们发送到各个功能单元(每个单元都包含自己的指令解码器)。

处理器控制单元(PCU)的指令解码器为其所有内部单元生成控制信号。

7.1.2 术语

本节定义了后续章节中用于描述程序控制的术语:

• Fetch-Line(获取行):在指令获取阶段,程序定序器在一次访问中从程序存储器中读取的信息单元。

• Instruction(指令):由核心功能单元之一执行的原子操作。指令长度不一,从16位到64位不等。指令由两个操作码组件组成,如下:

◦ Basic Instruction(基本指令):必需部分;携带指令标识的信息。

◦ Instruction Extension(指令扩展):可选的操作码部分,可以扩展操作码。扩展可以是16位、32位或64位长。

• Instruction Packet(指令包):一组并行执行的指令。

• Slot(槽位):指令包内的一个位置,可以在其中放置一个组件。指令包中的每个组件占用指令包的一个槽位。

• Slot Limit(槽位限制):可以构成指令包的最大组件数量(如果使用,则不包括头部)。

• Change of Flow (COF)(流程更改):指指令PC不以线性方式进展的所有情况(由于执行的指令或中断事件)。

• Branch-Type Instruction(分支类型指令):可能导致COF事件的PCU指令。

• Delay Slots (DS)(延迟槽):分支类型指令延迟槽。分支类型指令可以包括在其执行之后执行的一个或两个包(无论是否发生COF事件)。

• COF Frame(COF框架):由分支类型指令及其延迟槽组装而成的一组包。

• Branch Prediction(分支预测):在PCU计算分支地址之前,用于推测下一个要执行的PC的机制。

• Branch Target Buffer (BTB)(分支目标缓冲区):存储PC相关信息(可能由分支预测推测)的分支预测存储器。

• Return Address Stack (RAS)(返回地址堆栈):用于推测ret指令返回地址的分支预测堆栈。

7.2 指令调度器

核心编码方案是VLIW(Very Long Instruction Word,超长指令字)。这意味着一个指令包是由一条或多条指令组成的,其中每条指令都与核心的一个功能单元相关联。在指令包中,每条指令占据一个槽位。

指令调度器负责识别构成指令包的各个指令,并将每条指令分派给与其相关联的功能单元。

指令调度器包含以下功能组件:

- 对齐单元:它负责识别指令包,并将其加载到指令寄存器中。当指令包中包含16位指令时,此单元会在将这些16位指令加载到指令寄存器之前,将它们对齐到32位边界上。更多详细信息,请参见第7.2.2节“对齐单元”。

- 派发单元:它负责将指令实际发送到相应的功能单元。更多详细信息,请参见第7.2.3节“派发单元”。

- 循环缓冲区:它存储可配置数量的指令包,以便作为循环重新执行,而无需从程序存储器中重新获取这些指令包。更多详细信息,请参见第7.4.4节“短循环”。

7.2.1 指令调度器功能

指令调度器设计用于支持以下主要特性:

• 可变指令大小支持:基本指令大小可以是16位或32位。16位指令提供了良好的代码紧凑性,有助于减少存储空间和提高执行效率。

• 指令级并行性支持:允许多条指令组成一个指令包。这种设计使得处理器能够同时执行多个操作,提高了整体性能。只要不超过可用的执行单元数量和包的最大长度限制,几乎允许任何指令组合。

有关包内编码规则的详细信息,请参阅第7.2.4.2节“包编码规则”。这一节将详细介绍如何对指令进行编码以形成有效的指令包。

7.2.2 指令对齐单元

对齐单元在取指行内识别指令包的起始和结束点,然后将其加载到指令寄存器中。

从程序存储器中获取的指令包操作码存储在临时缓冲区中,该缓冲区称为指令队列(在程序定序器中实现,如第7.3节“程序定序器”所述)。所选双字(DWs)的数量由取指宽度决定,该宽度可以是四个或八个DWs。

所选组包含要分派到功能单元的单个指令或一组并行指令(即指令包)。在对齐阶段结束时,指令寄存器加载所选组。在当前派发阶段,从此指令寄存器将当前指令包分派到功能单元。

对齐单元还计算指令包的长度和下一个顺序指令包的地址。

7.2.3 指令派发单元

派发单元将当前周期内必须执行的所有指令(即指令包)发送到相应的功能单元。同时,派发单元还会向功能单元发送立即扩展指示。

派发单元的输入是指令寄存器,该寄存器由对齐单元加载。

每条指令都有一个标识字段,用于指示与其相关联的功能单元。派发单元根据此字段将每条指令发送到相应的功能单元。

控制字位于指令之前,并包含一个指示其类型的字段。派发单元使用此字段来识别每个控制字。

当指令包中包含扩展控制字时,派发单元会确定每条指令的大小以及每个扩展字段与哪个功能单元相关联。然后,它使用这些信息将所有扩展字段相应地发送到各个功能单元。

7.2.4 编码方案

以下部分定义了CEVA-BX2的基本编码方案。

7.2.4.1 基本指令字段

32位宽的基本指令具有以下固定字段:

• 系统(System):32位基本编码的最高有效位(MSBs)被称为系统字段,它包含有关数据包边界、指令应分派到的单元以及指令扩展使用的信息。此字段还标识指令所属的执行单元类型,例如SPU、LD、ST等。专用的系统值用于标识16位指令。

• S(序列):此字段用于通过值为0来标识数据包中的最后一条指令。

• EE(存在扩展):此字段指示指令是否具有编码扩展:

0 = 指令仅为32位长。

1 = 指令有扩展(即,指令至少为48位长)。

扩展的大小在扩展本身中编码。

根据定义,16位指令没有EE字段,但有些包含S位。这意味着,当16位指令存在于数据包中时,它必须是数据包中的最后一条指令。

7.2.4.2 数据包编码规则

多个指令可以在一个指令数据包中编码(简称为数据包)。数据包将在一起执行同一周期中分派的指令捆绑在一起。数据包必须符合以下规则:

• 数据包的长度不能超过程序取指行的长度(256位)。

• 没有编码S字段的16位指令必须在数据包的末尾编码。

• 如果数据包中出现PCU指令,则必须将其编码为数据包中的第一条指令。这意味着此类16位PCU指令必须单独存在于数据包中,因为这样的指令必须是数据包中的第一条和最后一条指令。

7.2.4.3 扩展减少

其最大编码定义使用扩展(超过32位)的指令可以具有几种编码变体,具有较短的扩展,直至基本的32位编码。

由于汇编器不编码编码默认值的扩展部分,因此将使用最小的非默认扩展对指令进行编码。每个单元中的指令解码器将指令扩展到其最大长度。硬件将这些扩展字段解释为具有默认值。

这种编码方案最小化了代码大小,并将常用字段放在基本编码和较短的扩展中。通常,一个字段将被拆分为几个子字段,这些子字段部分在基本编码中编码,部分在扩展中编码。例如,可以定义指令,以便谓词字段不在基本编码中编码,而仅在扩展中编码。这意味着,如果指令没有谓词,则将其编码为32位。使用谓词将强制指令使用扩展。

在另一个示例中,32位的立即数字段可能被拆分为三个部分,每个部分在不同的位置编码。指令的实际长度将由立即数值决定;值越小,扩展越短(以16位为单位)。

7.2.4.3.1 减少立即数字段

如果较长扩展字中编码的部分全部为零,则将减少无符号的立即数字段。

如果较长扩展中编码的部分是统一的符号扩展(即,它要么全部为零,要么全部为一),则将减少带符号的立即数字段。解码器将根据其编码部分中的MSB将其扩展到全长。

7.2.4.3.2 减少寄存器字段

如果寄存器字段被拆分,以便其一些MSB位于较长的扩展中,则假定在字段的缺失位中编码0。例如,可以拆分编码寄存器r0-r31的5位字段,以便在主要指令中编码三位,在扩展中编码两位。如果指令使用寄存器r0-r7,则汇编器不会编码扩展。如果使用寄存器r8-r31,则会生成扩展。注意:如果寄存器字段是连续编码对或相同寄存器编码对的一部分(如第7.2.4.3.3节“减少连续寄存器对”和第7.2.4.3.4节“减少相同寄存器对”中所述),则此减少不适用。

7.2.4.3.3 减少连续寄存器对

在某些情况下,一对具有连续索引的操作数(例如,r6,r7)将被组织起来,使得第二个操作数被编码在更长的扩展中。在这种情况下,解码器假定,如果没有扩展,第二个操作数就是编码操作数的连续寄存器。这种方案经常用于编码64位操作数、累加器源-目标对、双元素向量(.i2)或双元素复数。

7.2.4.3.4 减少相同的寄存器对

在某些情况下,一对具有相同索引的操作数(例如,r7,r7)将被组织起来,使得第二个操作数被编码在更长的扩展中。在这种情况下,解码器假定,如果没有扩展,第二个操作数具有与编码操作数相同的索引。这种方案经常用于编码两个经常组织成.s2部分的16位操作数。

7.2.4.4 共享编码载波操作码

共享编码载体(SEC)是一种操作码,它为数据包中的所有指令添加额外的编码位以共享。它由汇编器为某些语法自动生成。

CEVA-BX2使用此操作码将数据包标记为部分执行(PE)对象。有关更多详细信息,请参阅第8节“部分执行”。

3642

3642

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?