SAR ADC(逐次逼近型模数转换器)的工作原理是基于二进制搜索算法和逐次逼近技术来实现的模拟信号到数字信号的转换。以下是SAR ADC的基本工作原理:

- 采样阶段:首先,SAR ADC将模拟输入信号进行采样,通常通过采样保持电路来实现。采样保持电路确保在转换期间输入信号保持不变。

- 初始化阶段:在采样完成后,SAR ADC将其内部的逐次逼近寄存器(SAR)初始化为中间值,通常是对应于模拟输入范围一半的数字码。

- 比较阶段:接下来,SAR ADC将采样的模拟输入信号与SAR产生的模拟输出信号进行比较。这通常通过一个比较器来实现,比较器输出一个表示两个信号大小关系的数字信号。

- 逐次逼近阶段:根据比较器的输出结果,SAR ADC会调整SAR中的数字码,以逼近模拟输入信号。具体来说,如果比较器指示模拟输入信号大于SAR产生的模拟输出信号,则SAR ADC会增加SAR中的数字码;反之,如果模拟输入信号小于SAR产生的模拟输出信号,则SAR ADC会减少SAR中的数字码。这个过程会逐位进行,从最高有效位(MSB)开始,直到最低有效位(LSB)。

- 输出阶段:当逐次逼近过程完成后,SAR中的数字码就是转换结果的数字表示。SAR ADC将这个数字码输出为最终的数字信号。

SAR ADC的工作原理使其具有高精度、低功耗和可扩展性强的特点。通过逐次逼近技术,SAR ADC可以逐步减小转换误差,提高转换精度。此外,由于其结构简单,SAR ADC的功耗较低,适用于对功耗要求较高的电子设备。同时,SAR ADC的结构易于实现和扩展,可以根据需要增加比特位数以提高转换精度。

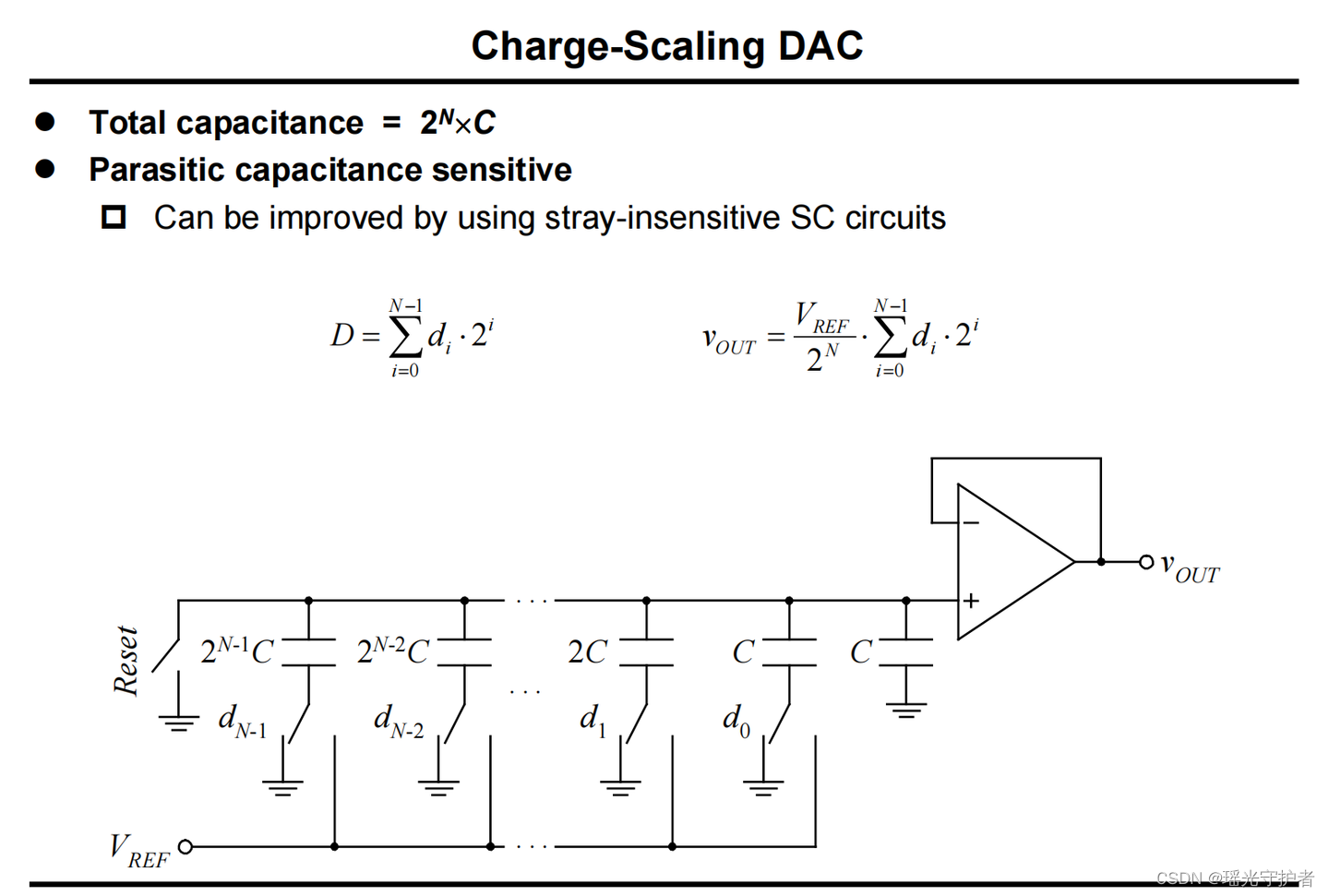

SAR ADC电路结构如下所示:

1 单调开关切换

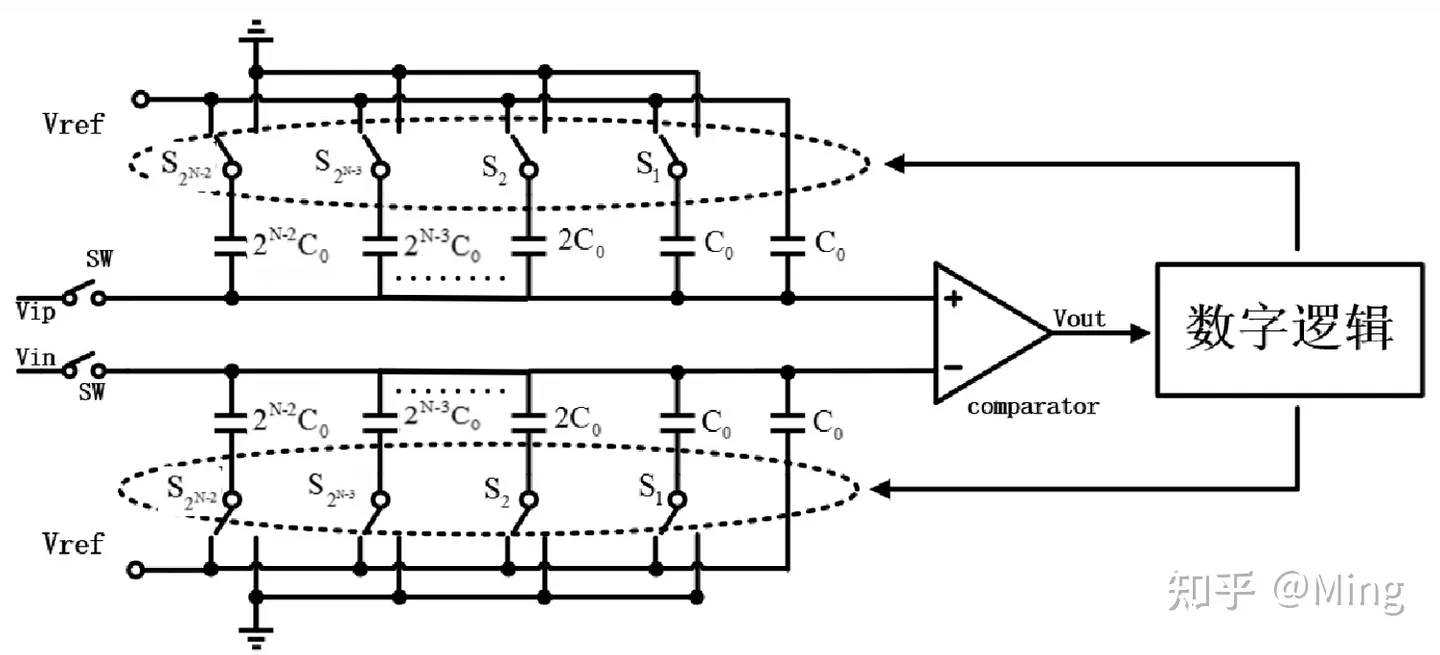

图1是N位单调差分CDAC的架构图,由两组CDAC阵列组成。每一组CDAC都由N-1个具有二进制比例关系的电容构成,每位电容值与低于该位权重所有电容之和相等,另外还有一个冗余单位电容来满足二进制比例关系。对于 N 位的单调差分CDAC架构,单边需要的总电容数目为2^(N-1) 。

图1 单调开关切换时序的CDAC架构

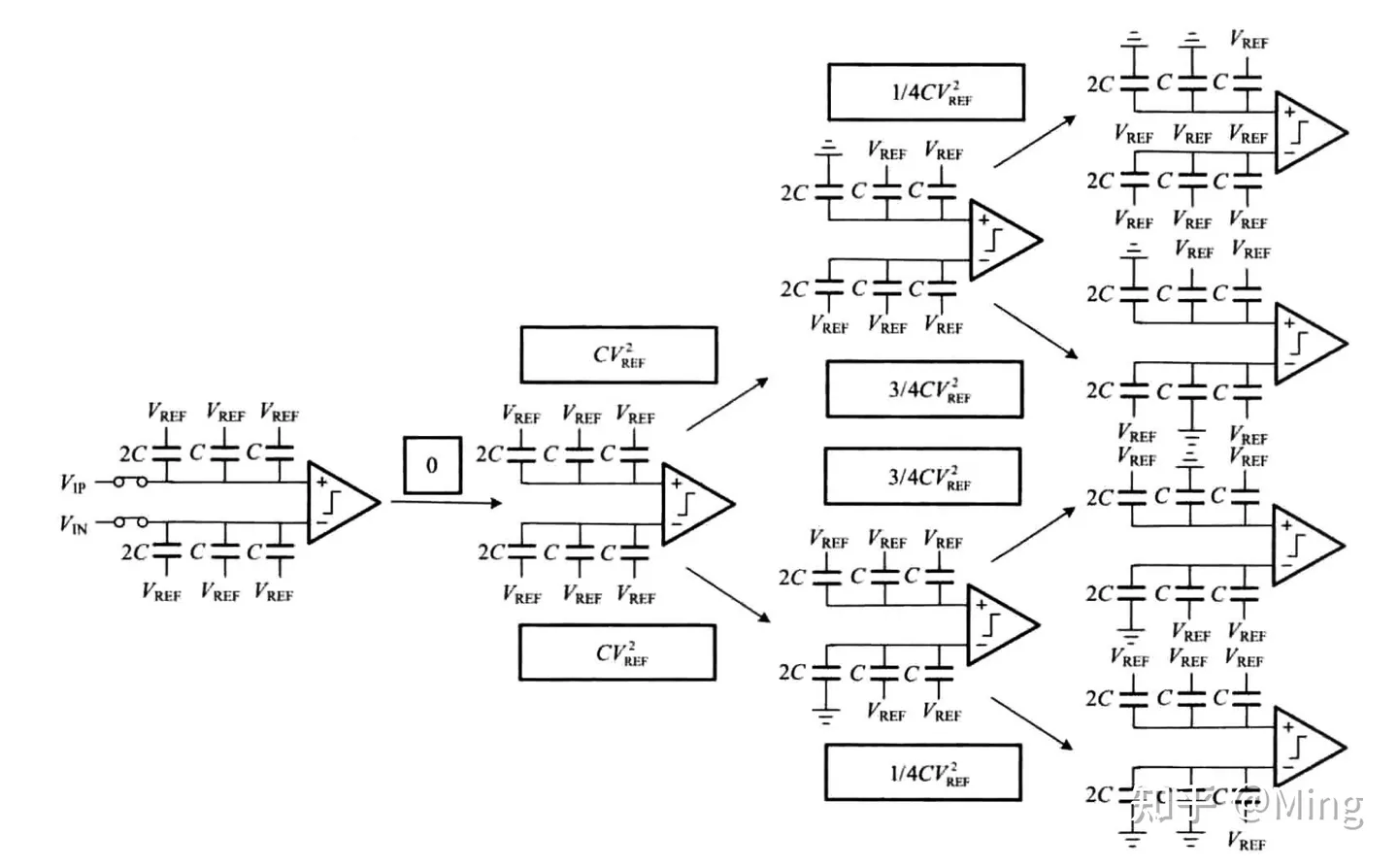

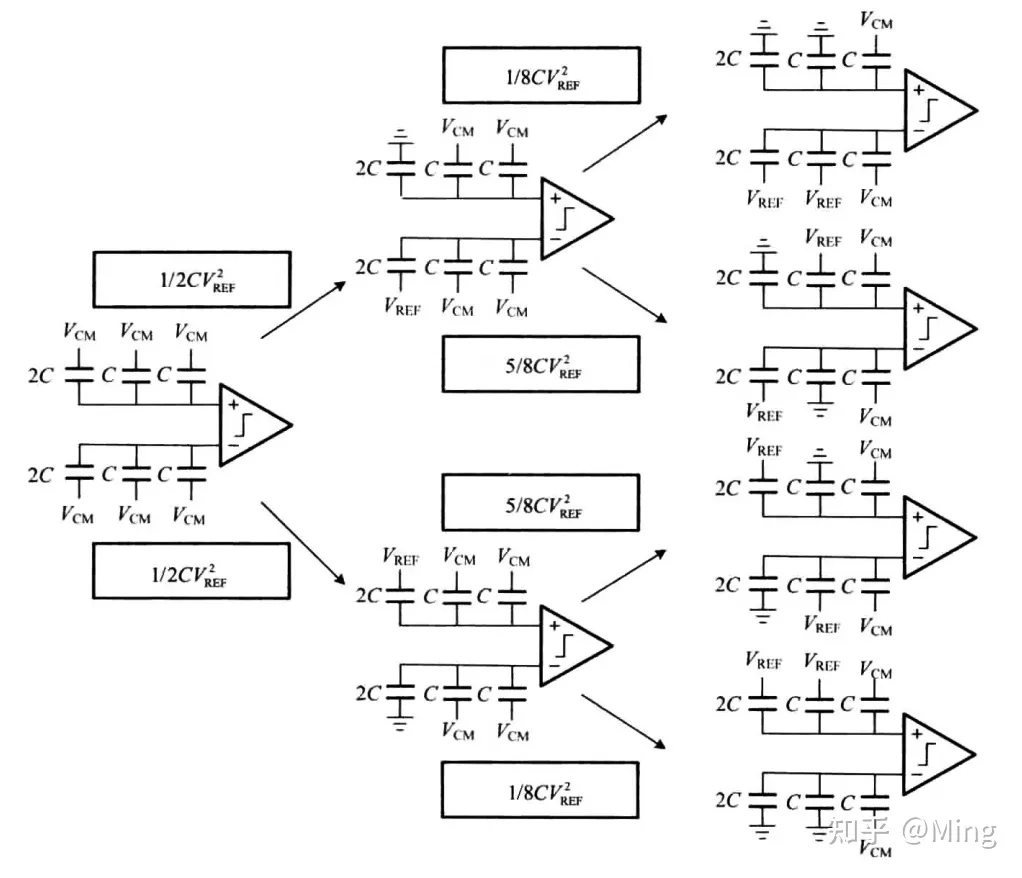

图2是3bit SAR ADC 单调电容开关时序的功耗示意图,具体分两个过程:采样和电荷再分配。在采样时,信号经开关采样保持至电容阵列上极板,下极板均复位到Vref处;在电荷再分配时,依据比较结果把 VP 和 VN 较大一端当位权重电容底板电压由Vref切换至gnd,电压较小的一端则保持不变。这种单端电压切换过程导致了输入共模电压的不断下降,从而对比较器提出了极高的要求。

图2. 3bit SAR ADC 单调电容开关时序的功耗示意图

2 Vcm-based开关切换

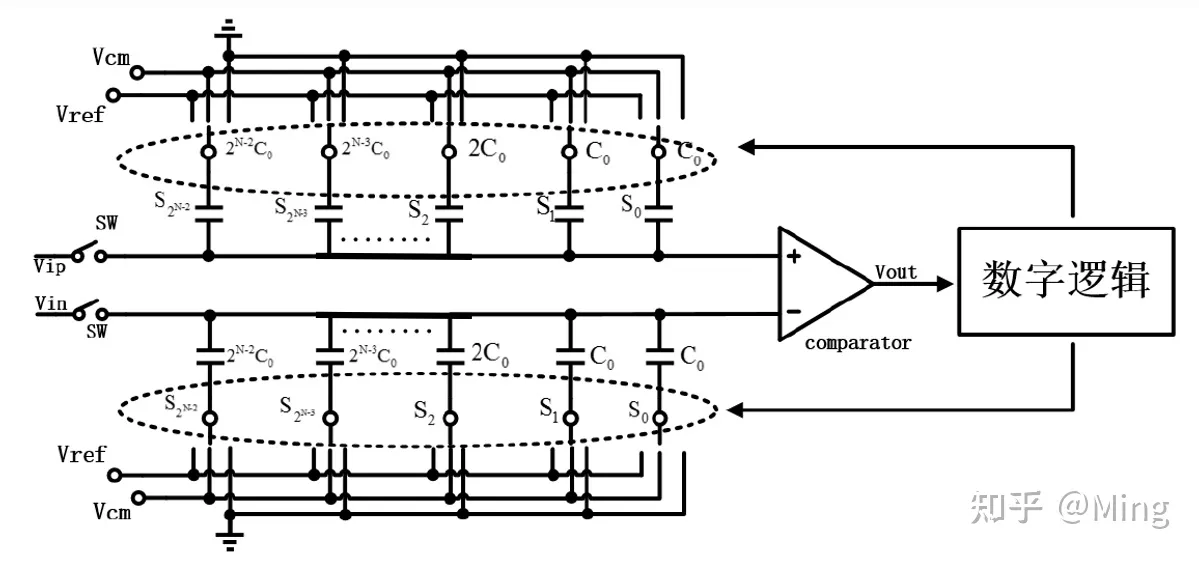

图3是Vcm-based的CDAC 架构图,由两组电容阵列组成与单调 DAC 阵列不一样的是,通过引入Vcm使得该架构能将冗余电容也加入再分配过程。对于N位Vcm-based的CDAC差分架构来说,单边需要的电容数目为2^(N-1) .

图3 Vcm-based CDAC架构

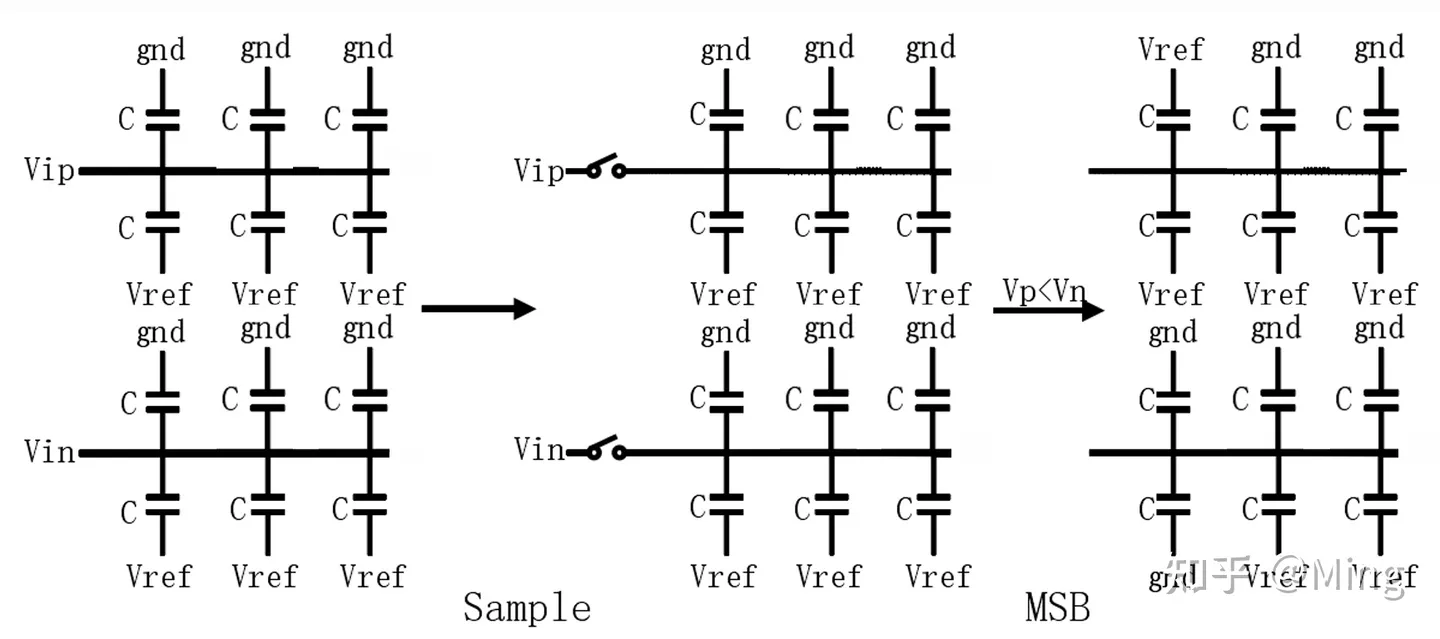

图 4为3位Vcm-based的 DAC 架构切换过程。在采样时,下极板复位到Vcm处;电荷再分配时,依据比较结果,将较大端当前位电容底板切换至 gnd,较小端则切换至Vref。切换到冗余位时,根据两端的大小只将其中较小的那端的冗余电容底板由Vcm切换到Vref,而另一端不变。该架构每次切换过程中两组电容阵列的电位都发生了变化,这让共模电平保持在Vcm。

图4. 3bit SAR ADC Vcm-based开关时序的功耗示意图

3 电容分裂技术

图 5为电容分裂CDAC架构切换过程。在采样时,可以理解成原先时1个电容接着Vcm,现在分裂成两个,一个复位至 Vref,另一个则复位至 gnd,效果是一样的。在电荷再分配时,依据比较结果将较大端的当前位电容底板为 Vref 电压切换至 gnd,较小端的当前位电容底板由 gnd 电压切换到 Vref。和Vcm-based CDAC架构相同,每次切换过程中两组电容阵列的电位都发生了改变,让共模电平保持在 Vcm。

图 5. 电容分裂CDAC架构切换过程

4 桥接CDAC架构

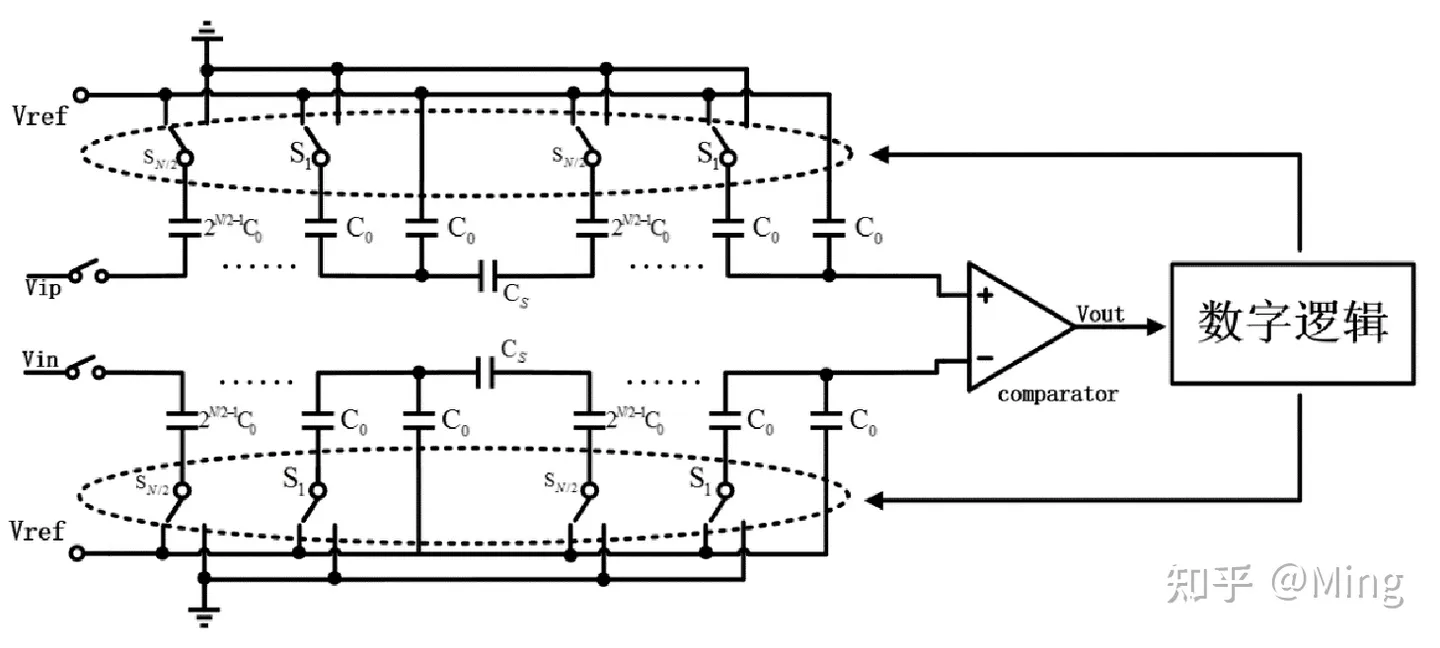

图6是桥接CDAC的架构图,其由两组电容阵列组成。与其他电荷分配型CDAC架构不同,桥接CDAC架构由两级权重电容阵列组成:高位电容阵列和低位电容阵列。高低阵列之间由桥接电容 连接,这种架构能够极大降低总电容数。对于N位的桥接CDAC,若高低电容阵列数目相同(MSB位数=LSB位数=N/2),那么单边所需单位电容数目为 2^(N/2-1)。

图6. 桥接CDAC架构

桥接CDAC架构的切换方式与单调CDAC架构类似。在采样时,输入信号经开关保持至高位电容阵列和桥接电容上极板处,同时高低阵列下极板处于 Vref。在电荷再分配时,其切换方式与单调CDAC相同,以高到低的顺序依次切换。桥接CDAC架构每次再分配都只改变其中一端的电压,故其双端的共模电平和单调架构是一样,开关切换会导致共模电压不断变化。

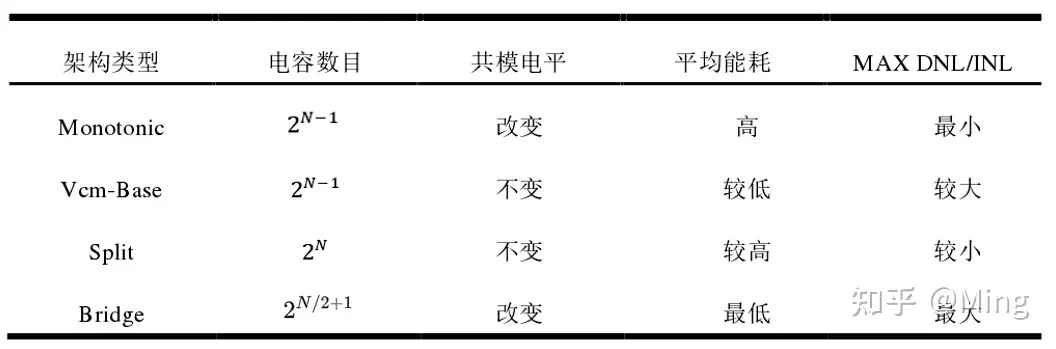

总结:选什么架构由spec去抉择,对能耗要求比较高,就可以采用Vcm-based或者Sanyal开关切换时序;对面积要求比较高,就可以采用桥接电容架构;对DNL/INL要求比较高,用单调开关切换时序也可以。前期要多多调研,本文内容可能会存在一些错误,还请以相关教材为准。

图7 各个架构的性能比较

本文详细解释了SARADC(逐次逼近型模数转换器)的工作原理,包括采样、比较、逐次逼近过程,强调了其高精度、低功耗和可扩展性。文章还介绍了不同电容切换策略(如单调、Vcm-based和桥接)及其在能耗、面积和精度需求方面的适用性。

本文详细解释了SARADC(逐次逼近型模数转换器)的工作原理,包括采样、比较、逐次逼近过程,强调了其高精度、低功耗和可扩展性。文章还介绍了不同电容切换策略(如单调、Vcm-based和桥接)及其在能耗、面积和精度需求方面的适用性。

1010

1010

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?