连续处理时候, done状态之后要立即拿下一组的byte1

module top_module(

input clk,

input [7:0] in,

input reset, // Synchronous reset

output [23:0] out_bytes,

output done); //

// FSM from fsm_ps2

// New: Datapath to store incoming bytes.

reg b3;

assign b3 = in[3];

parameter BYTE1 = 4'b0001;

parameter BYTE2 = 4'b0010;

parameter BYTE3 = 4'b0100;

parameter DONE = 4'b1000;

reg [7:0] byte1, byte2, byte3;

reg [3:0] state, next;

// State flip-flops (sequential)

always @(posedge clk) begin

if(reset)

state = BYTE1;

else

state = next;

end

// State transition logic (combinational)

always @(*) begin

if(reset ==0) begin

case (state)

BYTE1: begin

if(b3)

next = BYTE2;

else

next = BYTE1;

end

BYTE2: begin

next = BYTE3;

end

BYTE3: begin

next = DONE;

end

DONE : begin

if(b3)

next = BYTE2;

else

next = BYTE1;

end

default: begin

next = BYTE1;

end

endcase

end

else

next = BYTE1;

end

always @(posedge clk) begin

case (state)

BYTE1: begin

byte1 = in;

end

BYTE2: begin

byte2 = in;

end

BYTE3: begin

byte3 = in;

end

DONE: begin

if (next == BYTE2)

byte1 = in;

end

endcase

end

// Output logic

assign done = (state == DONE)? 1'b1: 1'b0;

assign out_bytes = {byte1, byte2, byte3};

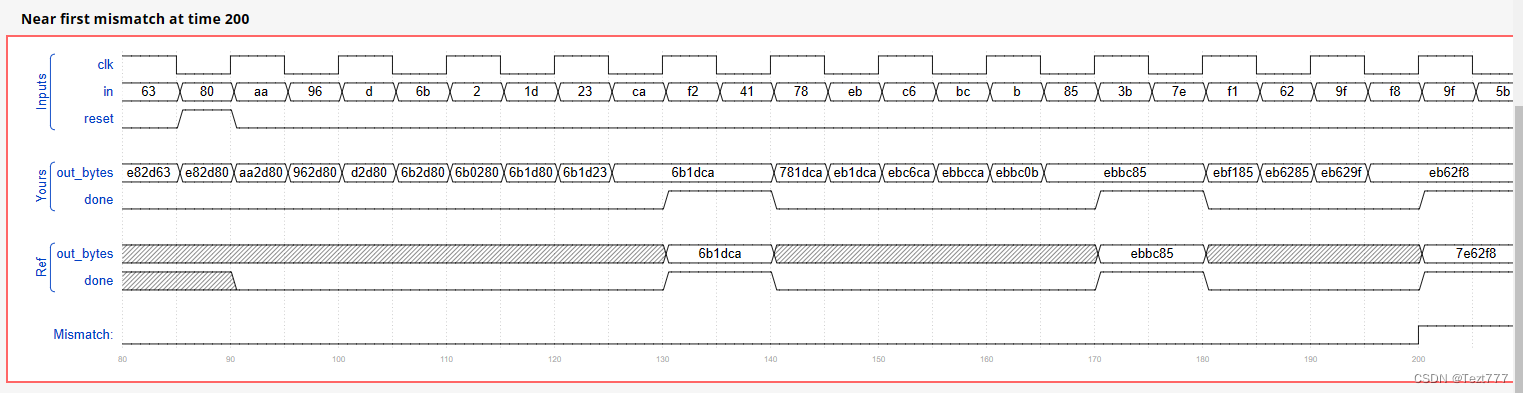

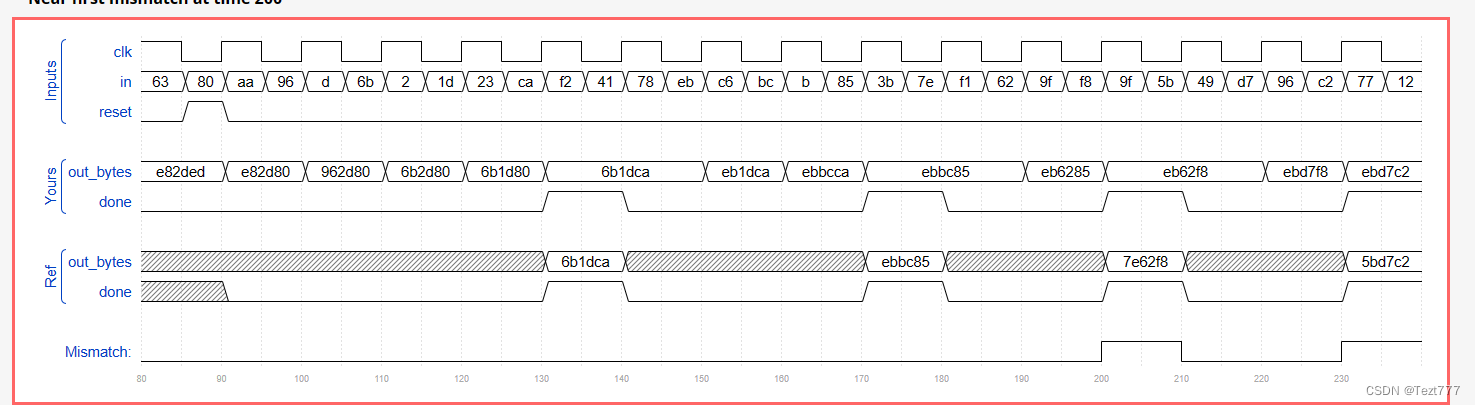

endmodule容易出错地方就是处理byte1, 错误示例波形:

921

921

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?