本系列文章将向大家推荐一个学习 Verilog 的好去处:HDLBits.Wire - HDLBitshdlbits.01xz.net

HDLBits 在提供 Verilog 基础语法教程的同时,还能够在线仿真你的 Verilog 模块,将你的输出与正确的时序比较,可以说真的是很棒了。

首先送上传送门。

作者今天被安利了一个很棒的 Verilog 学习网站:HDLBits 。然后发现知乎上还没有与 HDLBits 相关的话题,便写下这篇文章向大家推荐。

Verilog 基础教程

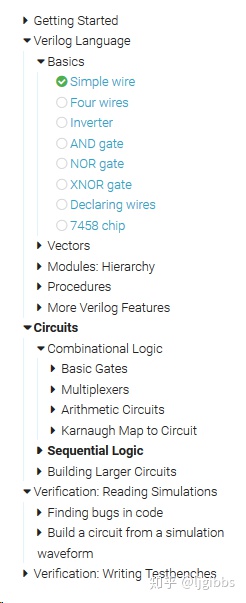

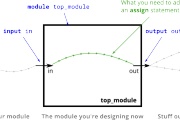

HDLBits 有一系列的 Verilog 基础知识,从最简单的 wire 的概念开始,包括了 Verilog 的基础语法,由逻辑门与触发器组成的电路,组合时序电路的概念,模块层级概念,testbench 的编写等等。

完整地对 Verilog 的语法进行整理就已经很棒了,我一直没有发现这样系统整理 Verilog 语法的中文网站,比如像菜鸟教程这样的网站,提供了大量软件语言的语法学习与备忘查询,大多数语言还支持在线编译执行。

Verilog 在线仿真

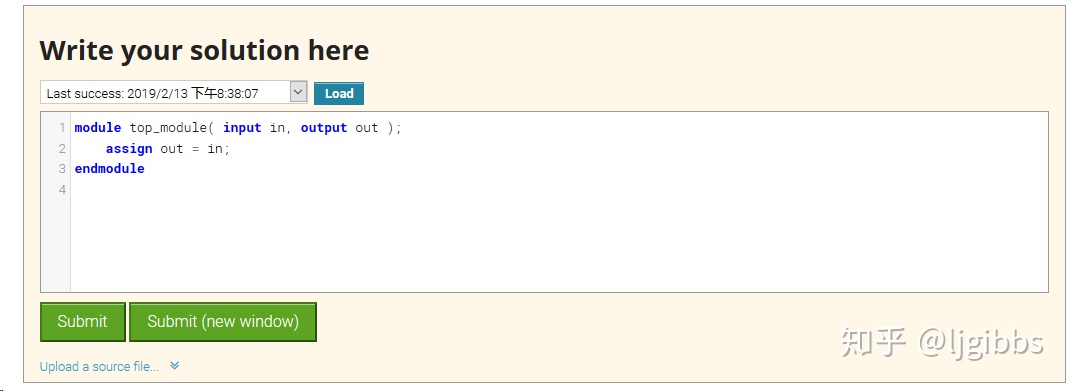

HDLBits 还提供了类似上图中,在线执行 c 语言代码的功能,可以在线对 Verilog 代码进行仿真,观察输出的时序。

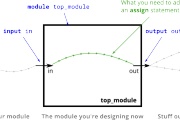

比如在 Wire 的教程中,就需要你实现一个模块,实现 wire 连线的功能。

假如非常睿智,写错成 assign out = ~ in; 那么提交之后,网站会指出你的时序同正确时序的差异:

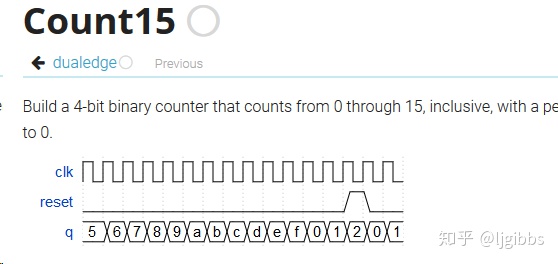

每个知识条目下,基本都有相应的练习,比如这个计数器。

如果你突然发现自己有点不确定怎么实现这个计数器了,那赶紧上 HDLBits 操练下吧。

Wire - HDLBitshdlbits.01xz.net

另外,简单注册之后,你的程序和进度就可以保存了。

作者也是刚刚接触这个网站,如果这个网站足够有趣的话,似乎又可以开始一个系列文章来一起探索一下 HDLBits

评论区的朋友给出了他的180题解法,欢迎大家移步参考,这里搬运下链接

https://github.com/xiaop1/Verilog-Practicegithub.com我和几位小伙伴一起整理翻译了 HDLBits 的题目(目前完成 2/3 了),附上了我们的答案与解析,以及随手穿插其中有关 Verilog 的理解分享。收录在我们的专栏:HDLBits 中文导学 中。欢迎关注,点赞,并向我们投稿你有关 Verilog,HDLBits 的相关见解!

声明

我们和作者邮件通信过,我们涉及 HDLBits 的中文翻译,图片应用以及解析一般没有版权问题。

转载最好请注明原作者和我们二次创作的链接。对 HDLBits 本身的再创作,最好可以联系下原作者。

HDLBits 中文导学zhuanlan.zhihu.com

2628

2628

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?