中值滤波的目的是滤除椒盐噪声,就是那种像是在图像上撒了盐粒子一样玩意儿。这一篇就来谈谈如何在FPGA上实现中值滤波。

数字滤波器的设计其实就是模板的设计。

本实验选取3x3模板,中值滤波也很简单,求模板上三行三列像素值的中值就可以了。

那么,如何求中值呢?

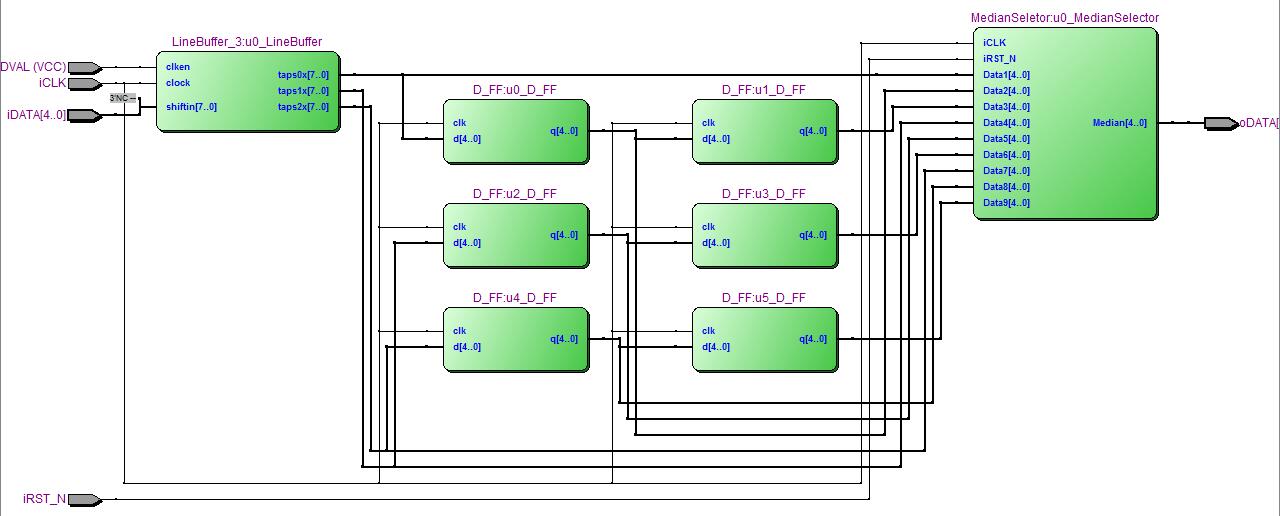

先看一下 RTL Viewer:

1)第一步 搭建LineBuffer

搭建LineBuffer方法,已经在上篇博客 “图像高斯滤波的FPGA实现--实时高速” 中详细介绍,目的和原理完全相同。读者可参阅上篇。

2)第二步 搭建三个移位寄存器

因为LineBuffer只是提供了三根管子,输出的是每根管子的末尾像素值,只有三个。但我们需要3x3=9个像素值,所以需要在每根管子的后面加上2个D触发器,目的是延时得到各行的其余两个像素!!

D触发器的程序如下;

module D_FF

(

clk,

d,

q

);

input clk;

input [4:0]d;

output reg [4:0]q;

always@(posedge clk)

q <= d;

endmodule

很简单吧~

3)第三步 得到了3x3个像素之后,就需要把这9个像素值的中值提取出来,方法如下:

如下图:

First:先将每行元素按从大到小排列,得到右方的九宫格

Second:求

最大值列(第1列)的最小值:Min_of_Max、

中值列(第1列)的中值:Med_of_Med、

最小值列(第1列)的最大值:Max_of_Min、

Third:求Min_of_Max、Med_of_Med、Max_of_Min这三者的中值,得到Med_of_Nine即为9个像素的全体中值! 完毕

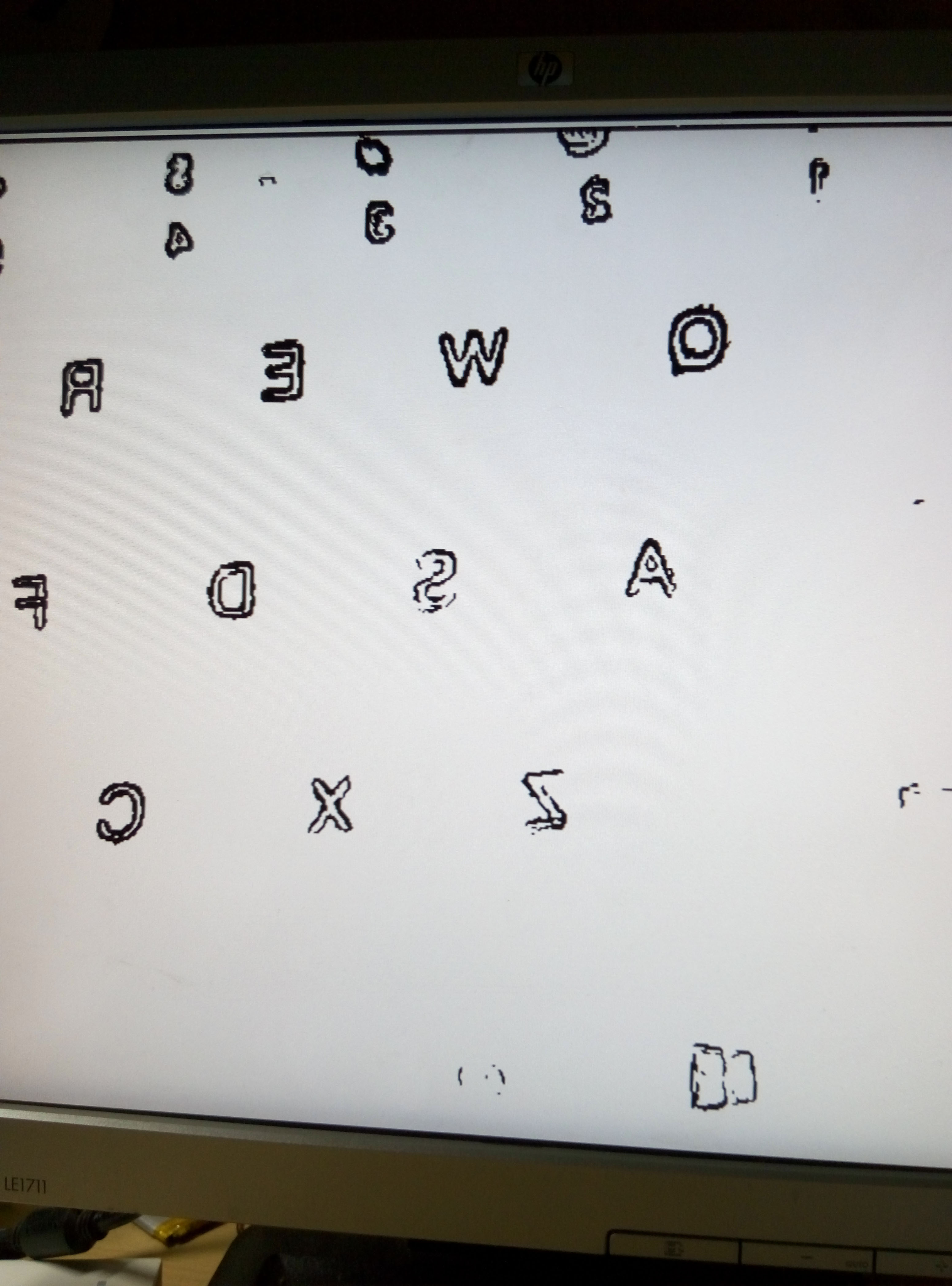

效果图如下,前一张是未经中值滤波的边缘提取,后一张是经过中值滤波的边缘提取。 可以明显看出,滤波去噪后的边缘提取图干净了许多!

原理说完了,下面贴上第三步的Verilog HDL源码

module MedianSeletor

(

input iCLK,

input iRST_N,

input [4:0] Data1,

input [4:0] Data2,

input [4:0] Data3,

input [4:0] Data4,

input [4:0] Data5,

input [4:0] Data6,

本文介绍了如何在FPGA上实现中值滤波以去除椒盐噪声。通过搭建LineBuffer和使用移位寄存器获取3x3像素矩阵,然后通过排序算法找出中值,最终实现高速实时的中值滤波效果。

本文介绍了如何在FPGA上实现中值滤波以去除椒盐噪声。通过搭建LineBuffer和使用移位寄存器获取3x3像素矩阵,然后通过排序算法找出中值,最终实现高速实时的中值滤波效果。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7577

7577

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?