与标准的串行接口IIC不同,SPI是一个同步协议接口,所有的传输都参照一个共同的时钟,这个同步时钟信号由主机(处理器)产生,接收数据的外设(从设备)使用时钟来对串行比特流的接收进行同步化。可能会有许多芯片连到主机的同一SPI接口上,这时主机通过触发从设备的片选输入引脚来选择接收数据的从设备,没有被选中的外设将不会参与SPI传输。

SPI主要使用4个信号:主机输出/从机输入(MOSI)、主机输入/从机输出(MISO)、串行SCLK或SCK和外设芯片(CS)。有些处理器有SPI接口专用的芯片选择,称为从机选择(SS)。

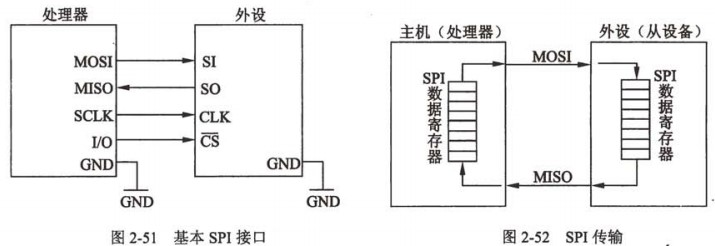

MOSI信号由主机产生,从机接收。在有些芯片上, MOSI只被简单的标为串行输入(SI),或者串行数据输入(SDI)。 MISO信号由从机产生,不过还是在主机的控制下产生的。在一些芯片上, MISO有时被称为串行输出(SO)或串行数据输出(SDO)。外设片选信号通常只是由主机的备用I/O引脚产生的。图2-51是微处理器通过SPI和外设进行连接的示意图。

主机和外设都包含一个串行移位寄存器,主机通过向它的SPI串行寄存器写入一个字节来发起一次传输。寄存器是通过MOSI信号线将字节传送给外设,外设也将自己移位寄存器中的内容通过MISO信号线返回给主机,如图2-52所示。这样,两个移位寄存器中的内容就被交换了。外设的写操作和读操作是同步完成的,因此SPI成为一个很有效的协议。

如果只是进行写操作,主机只需忽略收到的字节;反过来,如果主机要读取外设的一个字节,就必须发送一个空字节来引发从机的传输。

当主机发送一个连续的数据流时,有些外设能够进行多字节传输。许多拥有SPI接口的存储器芯片都以这种方式工作。在这种传输方式下,SPI外设的芯片选择端必须在整个传输过程中保持低电平。比如,存储器芯片会希望在一个“写”命令之后紧接着收到的是4个地址字节(起始地址),这样后面接收到的数据就可以存储到该地址。一次传输可能会涉及千字节的移位或更多的信息。

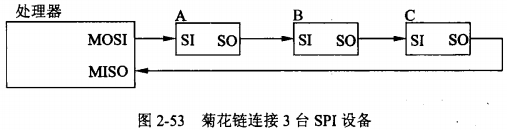

其他外设只需要一个单字节(比如一个发给A/D转换器的命令),有些甚至还支持菊花链连接,如图2-53所示。

在这个例子中,主机处理器从其SPI接口发送3个字节的数据。第1个字节发送给外设A,当第2个字节发送给外设A的 时候,第1字节已移出了 A,而传送给了 B。同样,主机想要从外设A读取一个结果,它必须再发送一个3字节(空字节)的序列,这样就可以把A中的数据移到B中,然后再移到C中,最后送回到主机。在这个过程中,主机还依次从B和C接收到字节。

注意,菊花链连接不一定适用于所有的SPI设备,特别是要求多字节传输的(比如存储器芯片)设备。另外,要对外设芯片的数据表进行仔细分析,确定能对它做什么而不能做什么。如果芯片的数据表中没有明确提到菊花链连接,那么该芯片不支持这种连接的几率为50%。

根据时钟极性和时钟相位的不同,SPI有4个工作模式。时钟极性有高、低两极:时钟极性为低电平时,空闲时时钟(SCK)处于低电平,传输时跳转到髙电平;时钟极性为高电平时,空闲时时钟处于高电平,传输时跳转到低电平。

时钟相位有两个:时钟相位0和时钟相位1,对于时钟相位0,如果时钟极性是低电平,MOSI和MISO输出在(SCK)的上升沿有效。如果时钟电平极性为髙,对于时钟相位0,这些输出在SCK的下降沿有效。 MISO输出的第X位是一个未定义的附加位,是SPI接口特有的情况。用户不必担心这个位,因为SPI接口将忽略该位。

参考资料:《嵌入式系统设计师》第2.4.5章节

8万+

8万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?