参考优秀博文,总结整体流程以及配置过程中出现的问题。

ChipScope是配合Xilinx Ise使用的片内逻辑分析工具。此处是ICON核和ILA核的使用方法。ILA核提供触发和跟踪功能,根据用户设置的触发条件捕获数据;然后在ICON的控制下,通过边界扫描口将数据上传到PC;最后在Analyzer中显示出信号波形。

1.生成project,需添加正确的.v以及.ucf文件,run Synthesize。

2.生成cdc文件

选择chipscope definition and connection file,命名,点击next。

点击finish

成功生成cdc文件

3.配置核

双击生成的cdc文件,启动chipscope pro core inserter,点击两次next,进入ILA设置界面。

trigger parameters界面,number of input trigger ports设置要观察波形的组数,trigger width设置每组观察的信号的数目。设置完成后点击next。

capture parameters界面,data depth设置信号采集的时钟周期数,采集数目越多,观察信号的时间越长。设置完点击next。

net connections界面。此时net connections端口列表显示红色字体,表示端口没有完全连接;当全部端口都与具体信号连接时,字体变为黑色。

双击clock ports打开select net对话框。

首先连接时钟信号,在右边net selections框中点clock signals,选择时钟的信道CH0,在左下方的信号列表中找到时钟信号,单击选中,然后单击右下方make connections按钮,完成clk信号的连接。

net selections框中点trigger/data signals,用同样的方法连接所有想要观察的信号。如果之前设置观察多组信号,可点击右下方TP0/TP1切换信号组。连接完成后点击下方OK退出select net对话框。

点击return to project navigator退出core inserter,并保存设置。

4. Implement

此时报错license缺失,下载一个license重新导入。点击ISE内HELP,选择manage license。

点击copy license添加license文件

导入成功后再次Implement。如果Implement过程中报错端口连接不完全,应返回ILA配置检查端口是否全部连接。

5.Generate Programming File

右键单击Generate Programming File,点击properties,在startup options中将start-up clock设为JTAG clock,点击ok。

运行Generate Programming File,生成.bit文件。

6.利用Analyzer观察信号波形

运行process框中的analyze design using chipscope,进入chipscope pro analyzer。

7.下载插件,使prom口可作为jtag口使用。

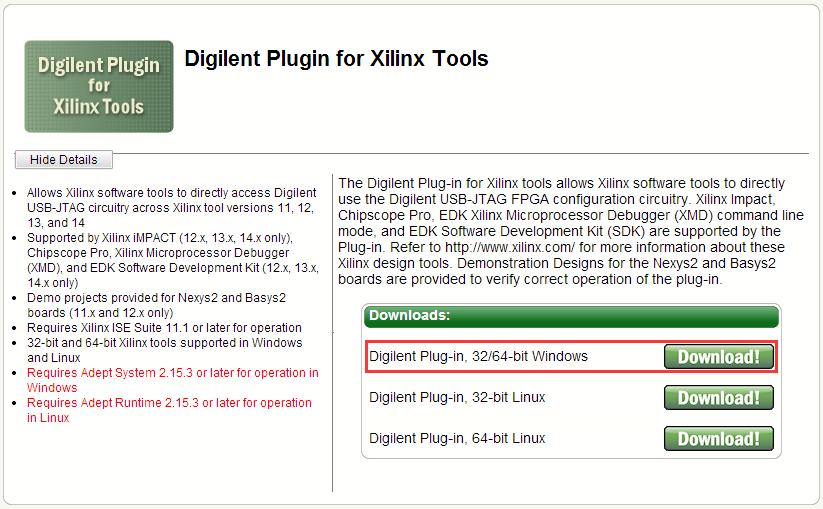

下载地址:http://www.digilentinc.com/Products/Detail.cfm?NavPath=2,66,768&Prod=DIGILENT-PLUGIN

windows系统下则选择如下(32位或64位适用):

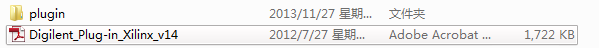

下载完成后解压,选择相应版本,得到一个文件夹以及一个使用说明:

按照使用说明内首先将所需文件复制到对应目录下(本机目录与其对应不上,在安装目录下找到几个相似的复制进去尝试之后就可以了- -)

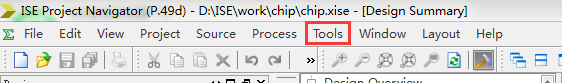

文件放置完毕后回到ISE,在Tools内找到iMPACT打开(ps:以下过程必须连上板子,否则检测不到设备无法完成设置)

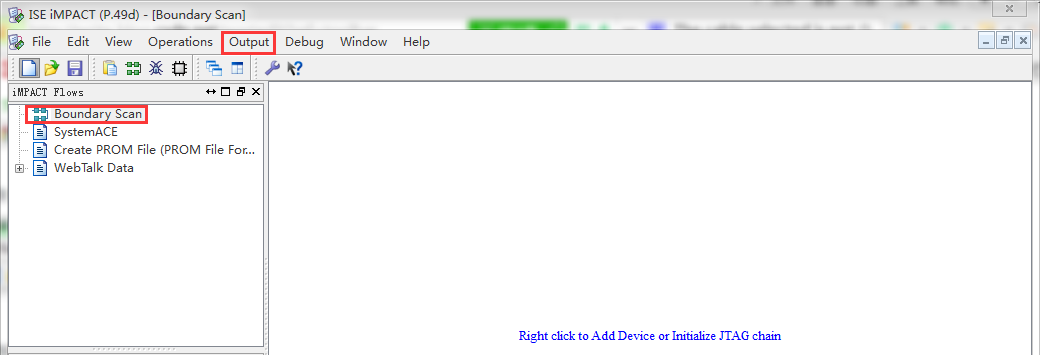

双击Boundary Scan,再点击Output,选择Cable Setup

选择Digilent USB JTAG Cable,再点击OK

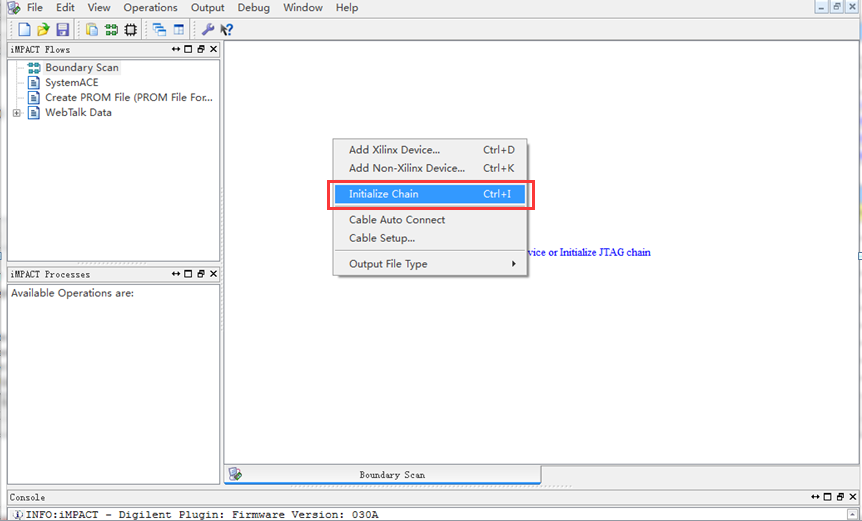

下图框内右键选择Initialize Chain

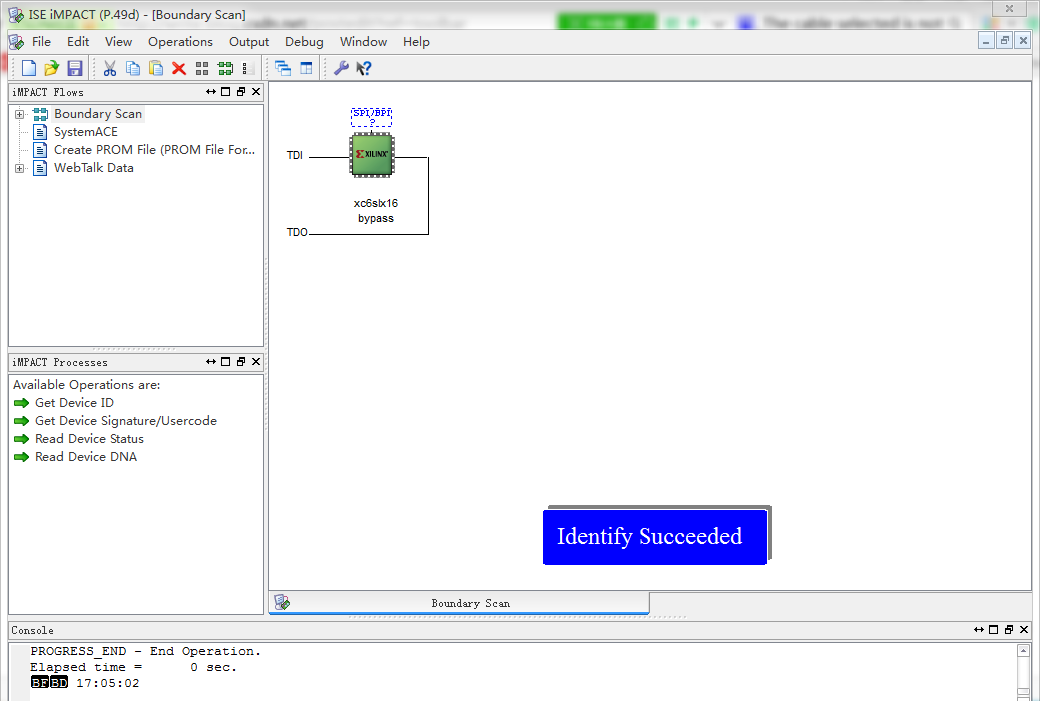

成功设置。

主体流程参考于以下的博客:

http://blog.csdn.net/c602273091/article/details/43453011

http://blog.csdn.net/rill_zhen/article/details/8115756

5万+

5万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?