本文将会介绍一个半加器的例子,它的真值表如下所示:

| 输入 | 输入 | 输出 | 输出 |

| a | b | s | co |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

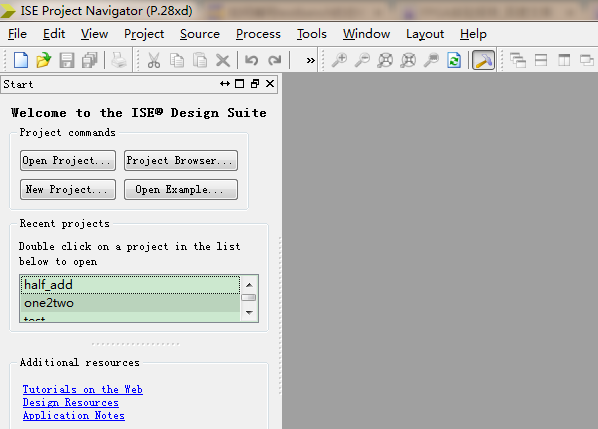

1、打开软件ISE Design Suite 14.2。

界面如下图所示。

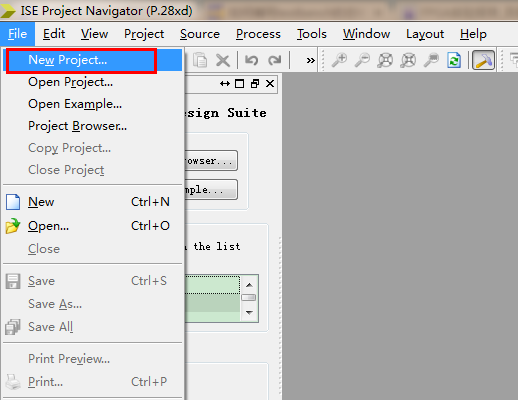

2、首先我们新建一个名为half的工程。

File->New Project...

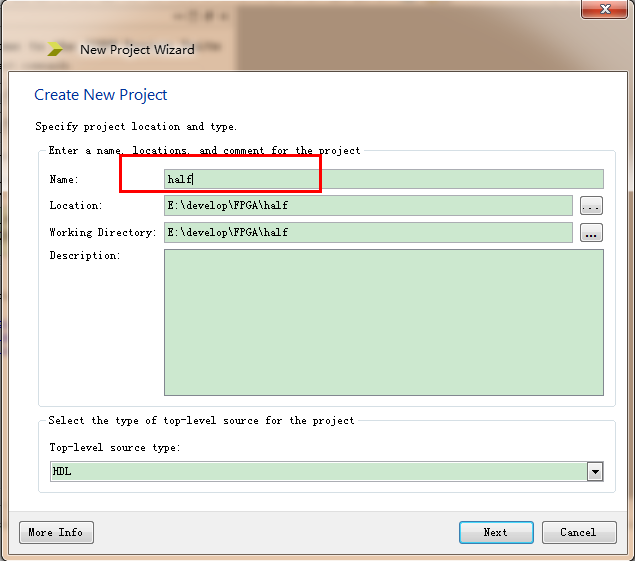

在Name处填写half工程名,并选择好路径。

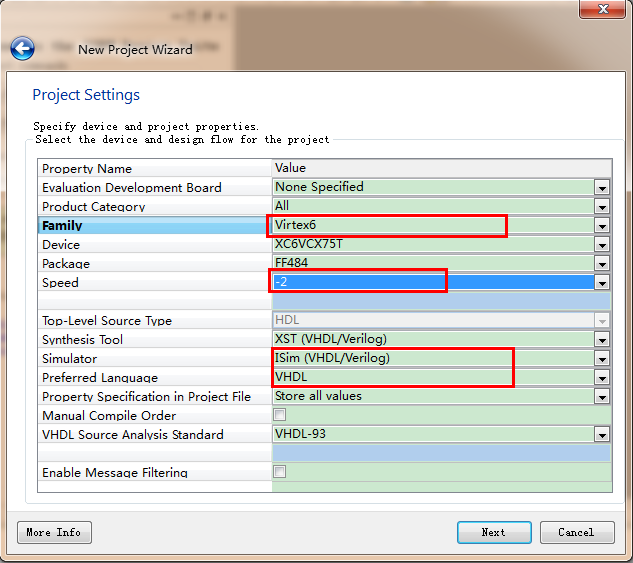

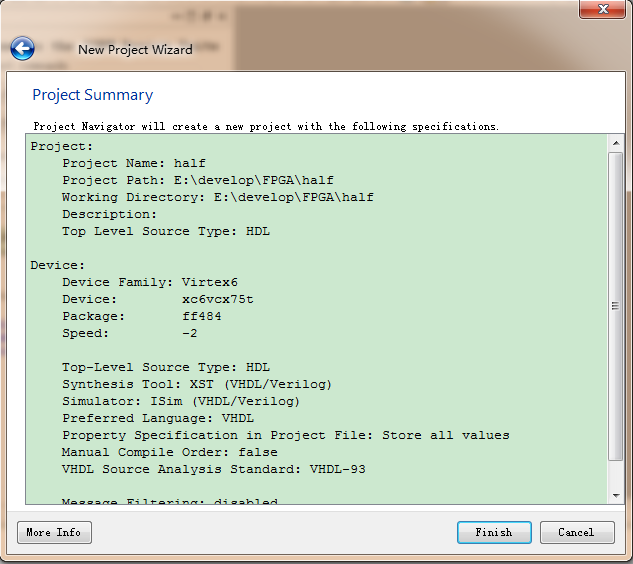

按照下图截图中所示,设置好相关参数。

Next之后如下图所示,点击Finish即可。

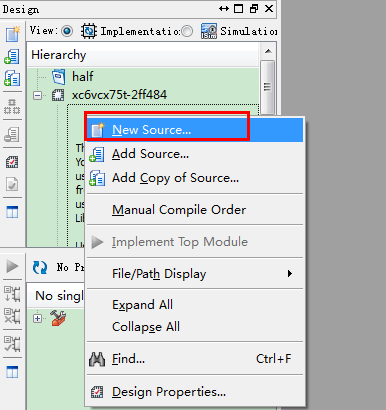

3、在新建的工程中新建vhd文件。

在Hierarchy区域中右键单击

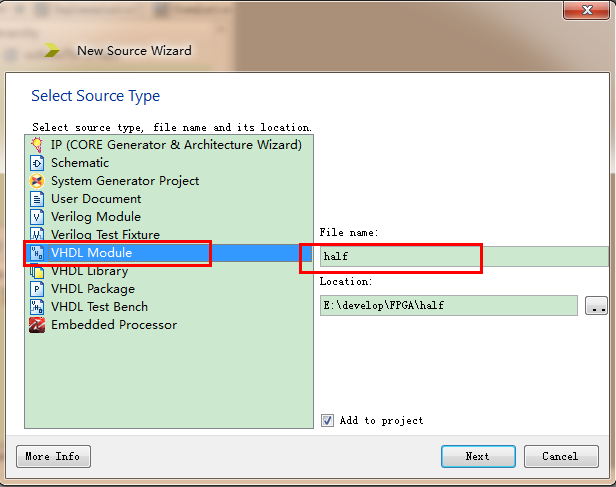

选择并填写文件名(可以写成half,也可以写成其它名称)

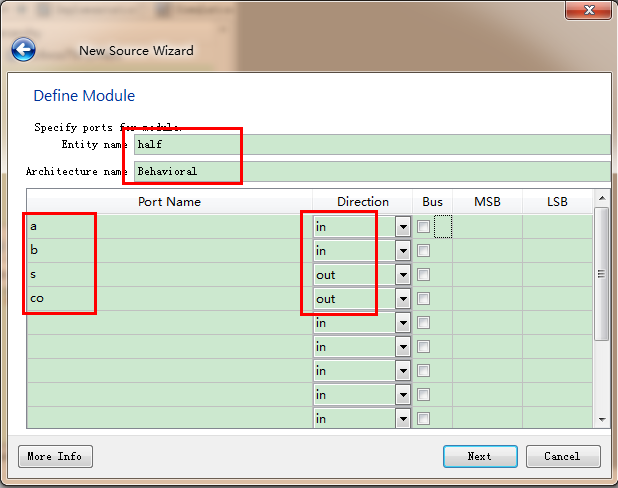

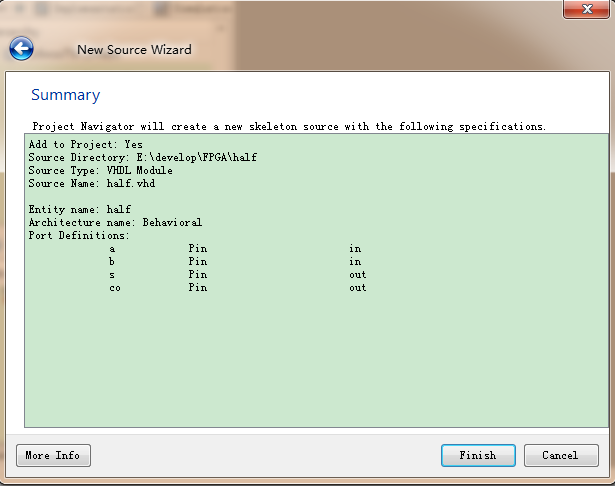

下图为新建文件的信息,点击Finish即可。

4、编辑half.vhd文件,实现相应的逻辑。

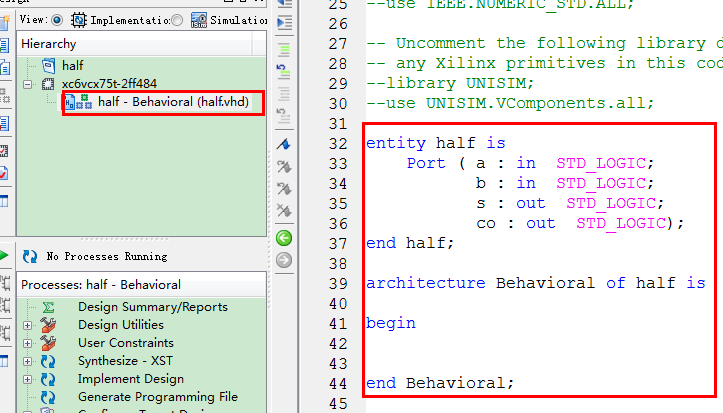

编辑之前如图所示。

编辑后如下图所示。

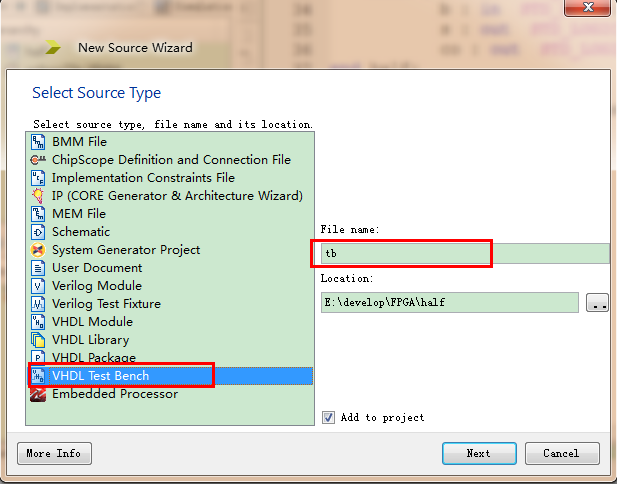

5、新建test bench文件tb.vhd

将half加入到tb中。

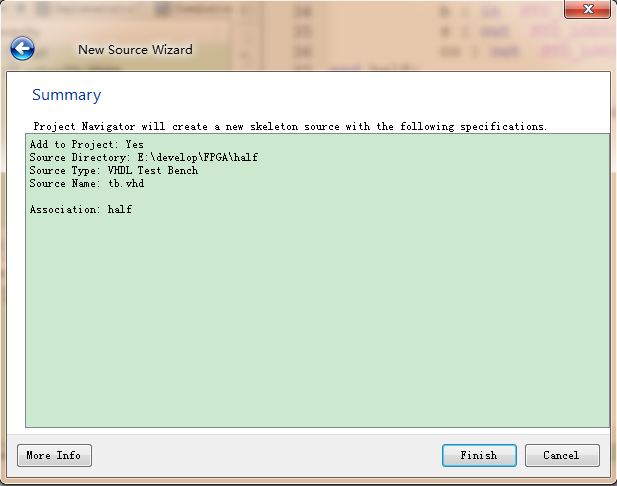

显示的结果,点击Finish即可。

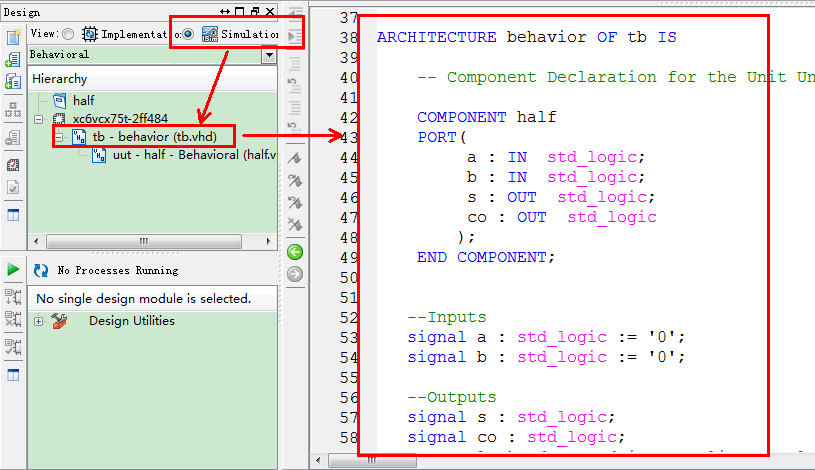

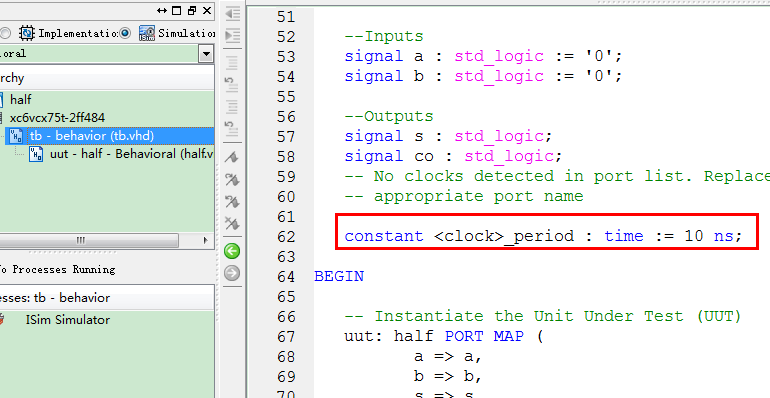

6、编辑tb.vhd文件并显示结果

编辑tb.vhd文件的路径

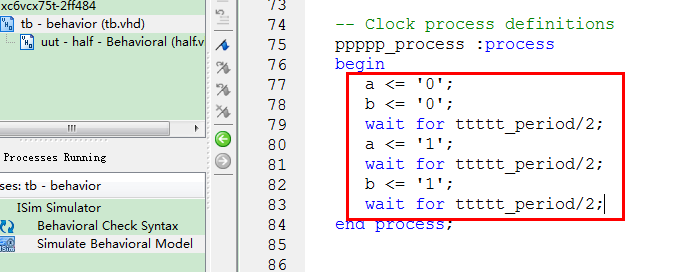

原红色区域中的代码。

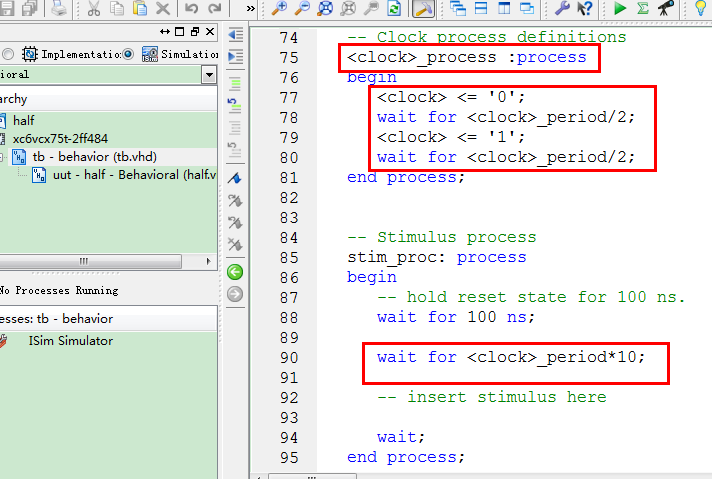

6.1、结果1

修改了红色区域中的代码。

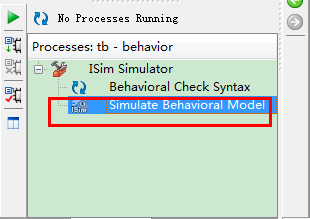

双击运行。

结果图下图所示:

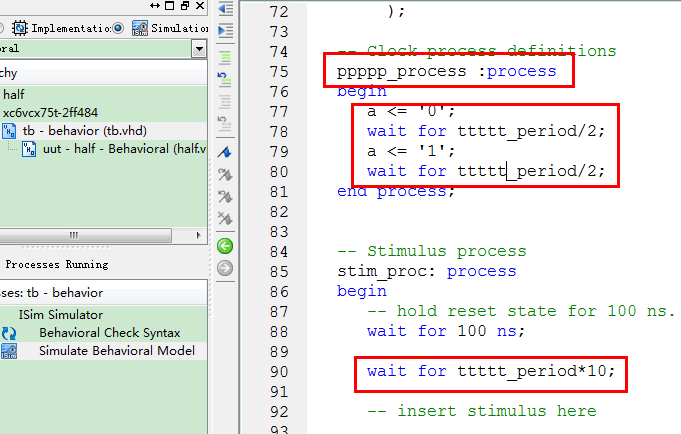

6.2、结果2

在结果1的基础之上,在红色区域中的代码进行了修改。

结果如下图所示:

参考文章:

http://wenku.baidu.com/view/ce80705ebe23482fb4da4c59.html

http://baike.baidu.com/link?url=1ZVh4Ub0UAR9zB2deYFSsGd6C-Mn6AeGpT_7sNvozqW-xIjfTy6y57udRH_MdjUE

博主也是新手一个,在终于知道怎么编写test bench之后,决定写一个ISE14.2的入门,就有了这篇记录。其实我也不太懂其中的比较深层次的原因,现在只是在比葫芦画瓢,现在我把我的瓢放出来给大家看看,也是希望大家也能从这个步骤中有比较感性的认识,大家共同进步,谢谢。

如果有什么意见或者疑问,欢迎跟帖留言。

3155

3155

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?