Cadence allegro 17.4 PCB DRC检查

1、检查连接是否全部完成

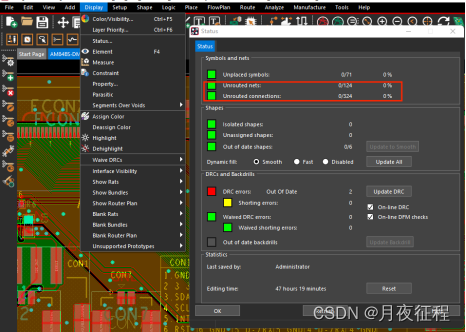

选择菜单 “Display—Status” 如图1-1 所示。

查看图 1-1 中标记处是否为“0%”。

图 1-1

2、检查Dangling Lines、Via

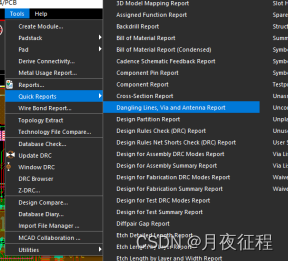

选择菜单“Tools-Quick Reports-Dangling Lines、Via and Antenna Report ”如图2-1 图2-2所示

图 2-1

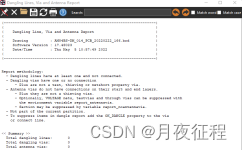

图 2-2

3、查看有无孤铜,无网络铜皮,查看图3-1中标记处是否为0

图 3-1

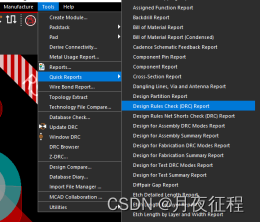

4、检查DRC

在PCB设计中,需要对DRC进行检查,确认目前存在的DRC是否可以忽略

操作步骤如下

选择菜单“Tool-Quick Reports-Design Rules Check (DRC) Report”如图4-1 图4-2

图 4-1

图 4-2

本文详细介绍了如何使用Cadence Allegro 17.4进行PCB设计的检查,包括连接完整性、悬空线条和via检查、孤铜和无网络铜皮的排查,以及DRC设计规则检查。通过菜单“Display—Status”、“Tools-QuickReports”等选项,确保设计符合规范,避免潜在问题。

本文详细介绍了如何使用Cadence Allegro 17.4进行PCB设计的检查,包括连接完整性、悬空线条和via检查、孤铜和无网络铜皮的排查,以及DRC设计规则检查。通过菜单“Display—Status”、“Tools-QuickReports”等选项,确保设计符合规范,避免潜在问题。

1336

1336

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?