iPod、电话、互联网移动通讯器……这不是三个独立的设备!我们称之为 iPhone!今天,苹果将重新定义电话。它来了。

—— 史蒂夫·乔布斯,2007年1月9日

新的信息和通讯技术,尤其是高速互联网,正在改变公司经营方式,改造公共服务交付,并使创新民主化。高速互联网连接增加10%,经济增长将增加1.3%。

—— 世界银行,2009年7月28日

1.1 Introduction

计算机技术在自从第一个通用电子计算机问世的约70年间取得了令人难以置信的进步。如今,花费不到500美元就能购买一部性能相当于1993年花费5000万美元购买的世界最快计算机的手机。这种快速改进既得益于计算机建设技术的进步,也得益于计算机设计的创新。

尽管技术改进历史上一直较为稳定,但由于更好的计算机架构带来的进步则不那么一致。在电子计算机的头25年里,这两种力量都作出了重要贡献,提供了每年约25%的性能提升。1970年代末,微处理器的出现改变了这一局面。微处理器能够借助集成电路技术的进步,导致了更高的性能提升率——每年约35%的增长。

这一增长率,加上大规模生产的微处理器带来的成本优势,导致计算机行业中越来越多的部分基于微处理器。此外,计算机市场的两个重大变化使得新的架构比以往更容易取得商业成功。首先,汇编语言编程的虚拟消除减少了对目标代码兼容性的需求。其次,标准化的、供应商独立的操作系统的创建,如UNIX及其克隆Linux,降低了推出新架构的成本和风险。

这些变化使得在1980年代初期成功开发出一系列新的架构成为可能,这些架构的指令集较为简化,被称为RISC(精简指令集计算机)架构。基于RISC的计算机将设计师的关注集中在两种关键的性能技术上:利用指令级并行性(最初通过流水线技术,后来通过多指令发射)和使用缓存(最初采用简单形式,后来采用更复杂的组织和优化)。

基于RISC的计算机提高了性能标准,迫使先前的架构要么跟上要么被淘汰。Digital Equipment 的Vax架构无法跟上,因此被RISC架构取代。英特尔迎接了这一挑战,主要通过将80x86指令内部转换为类似RISC的指令,从而能够采纳许多最初由RISC设计开创的创新。随着1990年代末晶体管数量的激增,转换复杂x86架构的硬件开销变得微不足道。在低端应用中,如手机,x86转换开销在功耗和硅面积上的成本促使RISC架构ARM成为主流。

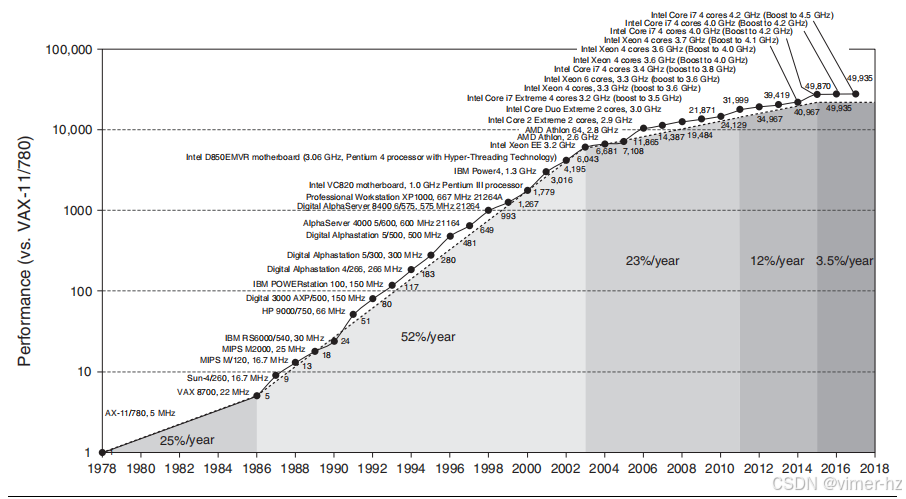

图1.1显示,架构和组织上的增强使得性能在17年内以每年超过50%的速度持续增长——这一增长率在计算机行业中前所未有。

这种在20世纪的剧烈增长率产生了四重影响。首先,它显著增强了计算机用户的能力。在许多应用中,最高性能的微处理器超越了不到20年前的超级计算机。

图1.1 处理器性能在40年间的增长。这张图展示了与VAX 11/780相比的程序性能,性能通过SPEC整数基准测试来衡量(见第1.8节)。在1980年代中期之前,处理器性能的增长主要受技术驱动,年均增长约22%,即每3.5年性能翻倍。从1986年开始,增长率提高到约52%,即每2年翻倍,这归因于以RISC架构为代表的更先进的架构和组织理念。到2003年,这种增长使得性能与22%增长率下的性能相比,差异大约达到25倍。由于Dennard缩放的终结和可用的指令级并行性的限制,2003年之后单处理器性能增长减缓至每年23%,即每3.5年翻倍。(自2007年以来最快的SPECintbase性能已开启了自动并行化,因此单处理器速度较难衡量。这些结果限于通常每芯片四核的单芯片系统。)从2011年到2015年,年增长率低于12%,即每8年翻倍,部分原因是Amdahl定律的并行性限制。自2015年以来,随着摩尔定律的终结,年增长率仅为3.5%,即每20年翻倍!浮点计算的性能遵循相同的趋势,但在每个阴影区域通常有1%到2%的年增长差异。第27页的图1.11展示了这些时期的时钟频率改进。由于SPEC测试随着时间的推移有所变化,新机器的性能通过一个缩放因子来估算,该因子与不同版本的SPEC(SPEC89、SPEC92、SPEC95、SPEC2000和SPEC2006)性能相关。目前SPEC2017的结果还不够多,无法绘制。

其次,成本性能的显著提升催生了新类型的计算机。个人计算机和工作站在1980年代随着微处理器的问世而出现。过去十年间,智能手机和平板电脑的兴起,使许多人将其作为主要的计算平台,取代了PC。这些移动客户端设备越来越多地使用互联网访问包含10万台服务器的数据中心,这些数据中心被设计成像单一庞大计算机一样运行。

第三,摩尔定律预测的半导体制造进步导致了微处理器计算机在整个计算机设计领域的主导地位。传统上由现成逻辑或门阵列构建的迷你计算机被使用微处理器构建的服务器所取代。即使是主机计算机和高性能超级计算机,也都是微处理器的集合。

这些硬件创新带来了计算机设计的复兴,强调了架构创新和技术进步的有效利用。这种增长率的加成效应使得到2003年,高性能微处理器的速度比仅依赖于技术(包括改进的电路设计)所能获得的速度快7.5倍,即52%每年相比于35%每年。

这种硬件复兴影响了软件开发。从1978年至今性能提升了50,000倍,使现代程序员能够用生产力换取性能。如今,很多编程工作使用像Java和Scala这样的托管编程语言,取代了以性能为导向的语言如C和C++。此外,更具生产力的脚本语言如JavaScript和Python,以及编程框架如AngularJS和Django,也越来越受欢迎。为了保持生产力并尽量弥补性能差距,采用即时编译器和基于跟踪的编译的解释器正在取代传统的编译器和链接器。软件部署也在改变,互联网服务的软件(SaaS)取代了需要安装和在本地计算机上运行的传统包装软件。

应用程序的性质也在变化。语音、声音、图像和视频变得越来越重要,以及对用户体验至关重要的可预测响应时间。一个激动人心的例子是Google翻译。该应用程序允许你将手机对准一个物体,图像通过无线网络传输到数据中心,数据中心识别照片中的文字并将其翻译成你的母语。你也可以对着它说话,它会将你说的话翻译成另一种语言的音频输出。它可以翻译90种语言的文本和15种语言的语音。

然而,图1.1也显示了这一17年的硬件复兴已经结束。根本原因是曾经存在几十年的半导体工艺的两个特性不再适用。

1974年,罗伯特·丹纳德观察到,即使在硅片的面积相同的情况下,随着晶体管数量的增加,功率密度保持不变,这是因为每个晶体管的尺寸变小。令人惊讶的是,晶体管可以更快但使用更少的功率。由于电流和电压无法继续下降而仍维持集成电路的可靠性,丹纳德缩放在2004年左右结束。这一变化迫使微处理器行业转向使用多个高效的处理器或核心,而不是单个低效的处理器。确实,2004年英特尔取消了其高性能单处理器项目,并与其他公司一起宣布,提升性能的道路将是通过每片芯片上的多个处理器,而不是通过更快的单处理器。这一里程碑标志着一个历史性的转变,从完全依赖指令级并行(ILP)——该书前三版的主要关注点——转向数据级并行(DLP)和线程级并行(TLP),这些内容在第四版中介绍,并在第五版中扩展。第五版还增加了WSC和请求级并行(RLP),在本版中进行了扩展。虽然编译器和硬件在不需要程序员注意的情况下隐式地利用ILP,但DLP、TLP和RLP是显式并行的,需要重构应用程序以利用显式并行。在某些情况下,这很容易;但在许多情况下,这是对程序员的重大新负担。阿姆达尔定律(第1.9节)规定了每片芯片上有用核心数量的实际限制。如果任务的10%是串行的,那么并行所能带来的最大性能收益是10,无论你在芯片上放多少个核心。最近结束的第二个观察是摩尔定律。1965年,戈登·摩尔著名地预测,每片芯片上的晶体管数量每年翻一番,1975年修正为每两年翻一番。这个预测持续了大约50年,但现在不再成立。例如,在2010年版中,最新的英特尔微处理器有1,170,000,000个晶体管。如果摩尔定律继续下去,我们可以预期2016年的微处理器将有18,720,000,000个晶体管。实际上,相应的英特尔微处理器只有1,750,000,000个晶体管,偏差了摩尔定律预测值的10倍。

由于以下因素:

- 晶体管性能的提升因摩尔定律放缓和丹纳德缩放的结束而变得不再显著,

- 微处理器的功耗预算不变,

- 单一功耗高的处理器被多个节能处理器取代,以及

- 实现阿姆达尔定律的多处理器限制,

导致处理器性能的提升速度放缓,即性能的翻倍周期从1986年至2003年间的每1.5年变为每20年(见图1.1)。

改善能效-性能-成本的唯一途径是专业化。未来的微处理器将包括多个领域特定的核心,这些核心在某一类计算上表现卓越,但远胜于通用核心。本版新增的第七章介绍了领域特定架构。

本书讨论了使过去一个世纪内惊人增长率成为可能的架构理念及相关编译器改进、剧烈变化的原因,以及面向21世纪的架构理念、编译器和解释器的挑战和初步有希望的方法。核心是量化的计算机设计和分析方法,使用程序的实证观察、实验和模拟作为工具。本书体现了这种设计风格和方法。本章的目的是为接下来的章节和附录奠定量化基础。

本书不仅旨在解释这种设计风格,还希望激发您为这一进步做出贡献。我们相信,这种方法将为未来的计算机提供服务,就像它曾经服务于隐式并行计算机一样。

1.2 Classes of Computers

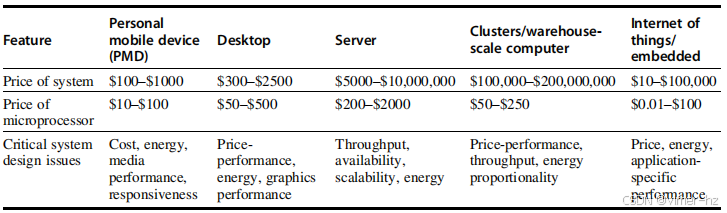

这些变化为我们在新世纪如何看待计算、计算应用和计算机市场奠定了基础。自个人计算机问世以来,我们未曾见过如此显著的计算机外观和使用方式的变化。这些计算机使用方式的变化导致了五个不同的计算市场,每个市场都有其独特的应用、需求和计算技术。图1.2总结了这些主流计算环境类别及其重要特征。

图1.2 总结了五种主流计算类别及其系统特征。2015年的销售情况包括约16亿台个人移动设备(其中90%为手机)、2.75亿台台式电脑和1500万台服务器。销售的嵌入式处理器总数接近190亿。在2015年,共出货了148亿台基于ARM技术的芯片。请注意,服务器和嵌入式系统的系统价格范围广泛,从USB密钥到网络路由器不等。服务器的价格范围来自于对高端事务处理所需的大规模多处理器系统的需求。

物联网/嵌入式计算机

嵌入式计算机存在于日常机器中:微波炉、洗衣机、大多数打印机、网络交换机以及所有汽车。物联网(IoT)指的是那些连接到互联网的嵌入式计算机,通常是无线连接的。当嵌入传感器和执行器时,IoT设备能够收集有用的数据并与物理世界互动,导致各种“智能”应用的出现,如智能手表、智能温控器、智能扬声器、智能汽车、智能家居、智能电网和智能城市。

嵌入式计算机的处理能力和成本范围最广泛。它们包括从成本仅为一分钱的8位到32位处理器,到用于汽车和网络交换机的高端64位处理器,其成本可达100美元。尽管嵌入式计算市场中的计算能力范围非常大,但价格是设计此类计算机时的关键因素。当然,性能要求确实存在,但主要目标通常是以最低价格满足性能需求,而不是以更高的价格获取更多性能。预计到2020年,IoT设备的数量将从200亿到500亿不等。

本书的大部分内容适用于嵌入式处理器的设计、使用和性能,无论是现成的微处理器还是将与其他专用硬件组装的微处理器核心。不幸的是,驱动其他计算机类别的定量设计和评估的数据尚未成功扩展到嵌入式计算领域(例如,见第1.8节中的EEMBC挑战)。因此,目前我们只能依赖定性描述,这些描述与本书其余部分不太契合。因此,嵌入式部分集中在附录E中。我们认为,将嵌入式内容放在单独的附录中可以改善文本的思路流,同时让读者了解不同需求如何影响嵌入式计算。

个人移动设备(PMD)

个人移动设备(PMD)是我们用来指代一系列具有多媒体用户界面的无线设备的术语,例如手机、平板电脑等。考虑到整个产品的消费者价格为几百美元,成本是一个主要关注点。虽然能源效率的重视通常由电池使用驱动,但对使用更便宜的包装(塑料而非陶瓷)和缺乏风扇冷却的要求也限制了总功耗。我们在第1.5节中更详细地讨论了能源和功率的问题。PMD上的应用程序通常是基于网页的和媒体导向的,比如之前提到的Google翻译示例。能源和尺寸要求导致使用闪存(第2章)进行存储,而不是磁盘。

PMD中的处理器通常被视为嵌入式计算机,但我们将它们保留为一个独立类别,因为PMD是可以运行外部开发软件的平台,并且它们具有许多桌面计算机的特征。其他嵌入式设备在硬件和软件的复杂性上更为有限。我们将运行第三方软件的能力作为非嵌入式和嵌入式计算机之间的分界线。

响应性和可预测性是媒体应用的关键特性。实时性能要求意味着应用程序的某个部分有一个绝对的最大执行时间。例如,在PMD上播放视频时,处理每个视频帧的时间是有限的,因为处理器必须很快接受和处理下一个帧。在某些应用中,存在更为细致的要求:不仅要约束特定任务的平均时间,还要约束超过最大时间的实例数量。这种方法——有时称为软实时——当偶尔错过时间限制但不会错过太多时是可以接受的。实时性能往往高度依赖于应用程序。

许多PMD应用中的其他关键特性是需要最小化内存和有效利用能源。能源效率受电池电力和热量散发的驱动。内存可能占据系统成本的相当大一部分,因此在这种情况下优化内存大小非常重要。内存大小的重要性转化为对代码大小的重视,因为数据大小由应用程序决定。

桌面计算

第一个市场可能也是目前在金额上仍然最大的是桌面计算。桌面计算涵盖了从售价不到300美元的低端上网本到售价2500美元的高端重配置工作站。自2008年以来,每年生产的桌面计算机中,超过一半是电池驱动的笔记本电脑。桌面计算的销售正在下降。

在价格和能力的广泛范围内,桌面市场往往被驱动以优化性价比。系统的性能(主要以计算性能和图形性能来衡量)与价格的结合是这个市场客户最关心的,因此也是计算机设计师关注的重点。因此,最新的高性能微处理器和降低成本的微处理器通常会首先出现在桌面系统中(详见第1.6节关于计算机成本问题的讨论)。

桌面计算在应用程序和基准测试方面也相对有较好的特征,但随着基于网页的互动应用程序的增加,性能评估面临新的挑战。

服务器

随着1980年代桌面计算的兴起,服务器的角色也逐渐扩大,提供更大规模和更可靠的文件和计算服务。这些服务器已经成为大规模企业计算的支柱,取代了传统的大型计算机。

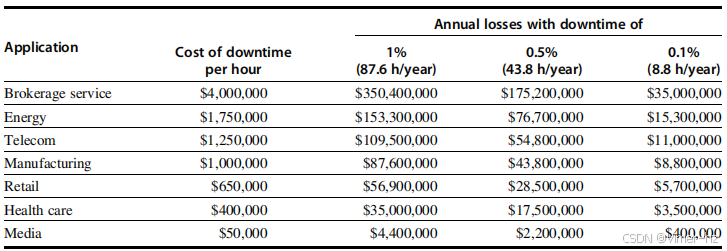

对于服务器来说,不同的特性是重要的。首先,可靠性至关重要(我们在第1.7节中讨论了可靠性)。考虑一下运行银行自动取款机或航空公司订票系统的服务器。这些服务器的故障比单台桌面计算机的故障要严重得多,因为它们必须全天候、每周七天不间断地运行。图1.3估算了服务器应用程序停机的收入损失成本。

图1.3 显示了系统不可用时成本的估算(四舍五入至最近的10万美元),通过分析停机的成本(即立即损失的收入),假设三种不同的可用性水平,并且停机时间分布均匀。这些数据来自Landstrom(2014),由应急计划研究公司收集和分析。

服务器系统的第二个关键特性是可扩展性。服务器系统通常会根据服务需求的增加或功能要求的扩展而增长。因此,扩展计算能力、内存、存储和I/O带宽的能力至关重要。最后,服务器设计的目标是高效的吞吐量。也就是说,服务器的整体性能——如每分钟交易数或每秒服务的网页数——是关键。对单个请求的响应仍然重要,但整体效率和成本效益(即单位时间内处理的请求数量)是大多数服务器的关键指标。我们将在第1.8节中回到不同计算环境下性能评估的问题。

集群/仓库规模计算机

软件即服务(SaaS)在搜索、社交网络、视频观看和共享、多玩家游戏、在线购物等应用领域的增长,导致了一类计算机的出现,即集群。集群是由通过局域网连接的台式计算机或服务器集合组成的,作为一个更大的计算机系统进行操作。每个节点运行自己的操作系统,节点之间通过网络协议进行通信。仓库规模计算机(WSC)是集群中最大的,它们设计成可以让成千上万台服务器作为一个整体来工作。第6章描述了这一类极其大型的计算机。

由于WSC的规模庞大,价格性能和功耗是关键因素。正如第6章所解释的,仓库的大部分成本与仓库内部计算机的电力和冷却相关。WSC的年折旧计算机和网络设备的成本为4000万美元,因为它们通常每隔几年就会更换一次。当你购买如此大量的计算时,你需要明智地购买,因为价格性能提升10%意味着每个WSC每年节省400万美元(4000万美元的10%);像亚马逊这样的公司可能有100个WSC!

WSC与服务器相关,因为可用性至关重要。例如,亚马逊在2016年的销售额为1360亿美元。由于一年大约有8800小时,平均每小时收入约为1500万美元。在圣诞购物的高峰时段,潜在损失将高出很多倍。正如第6章所解释的,WSC与服务器的区别在于WSC使用冗余、便宜的组件作为构建块,依赖软件层来捕捉和隔离在这种规模计算中会发生的许多故障,以提供所需的可用性。而WSC的可扩展性由连接计算机的局域网处理,而不是像服务器那样的集成计算机硬件。

超级计算机与WSC相关,因为它们都同样昂贵,价格在数亿美元,但超级计算机通过强调浮点性能和运行大型、通信密集型的批处理程序(这些程序可以运行数周)来与WSC区分开来。相比之下,WSC强调交互式应用、大规模存储、可靠性和高互联网带宽。

**平行性类别和并行体系结构**

在所有四类计算机中,多层次的平行性现已成为计算机设计的主要驱动力,能源和成本是主要的制约因素。应用程序中基本上有两种平行性:

1. **数据级平行性(DLP)**:这是因为有许多数据项可以同时进行操作。

2. **任务级平行性(TLP)**:这是因为创建了可以独立并且大部分时间并行操作的任务。

计算机硬件可以以四种主要方式利用这两种应用程序平行性:

1. **指令级平行性** 利用编译器的帮助在适度的水平上利用数据级平行性,使用诸如流水线技术的思想;在中等水平上使用诸如猜测执行的思想。

2. **向量体系结构、图形处理单元(GPU)和多媒体指令集** 通过将单个指令应用于数据集合来利用数据级平行性。

3. **线程级平行性** 在紧密耦合的硬件模型中利用数据级平行性或任务级平行性,这种模型允许并行线程之间的交互。

4. **请求级平行性** 利用程序员或操作系统指定的大部分解耦任务之间的平行性。

当Flynn(1966年)研究1960年代的并行计算工作时,他发现了一种简单的分类方法,我们今天仍在使用它的缩写。这些分类针对数据级平行性和任务级平行性。他考察了指令和数据流中的平行性,并将所有计算机划分为以下四类:

1. **单指令流,单数据流(SISD)**——这一类别是单处理器。程序员将其视为标准的顺序计算机,但它可以利用指令级平行性。第3章涵盖了使用ILP技术(如超标量和猜测执行)的SISD体系结构。

2. **单指令流,多数据流(SIMD)**——多个处理器使用不同的数据流执行相同的指令。SIMD计算机通过将相同的操作应用于多个数据项来利用数据级平行性。每个处理器有自己的数据内存(因此,SIMD中的“MD”),但有一个单独的指令内存和控制处理器,负责提取和分派指令。第4章涵盖了数据级平行性及三种利用它的体系结构:向量体系结构、标准指令集的多媒体扩展和GPU。

3. **多指令流,单数据流(MISD)**——到目前为止,没有建造出这种类型的商业多处理器,但它完整了这种简单分类。

4. **多指令流,多数据流(MIMD)**——每个处理器提取自己的指令并操作自己的数据,主要针对任务级平行性。一般来说,MIMD比SIMD更灵活,因此更具通用性,但其成本也相对较高。例如,MIMD计算机也可以利用数据级平行性,尽管开销可能比SIMD计算机更高。这种开销意味着粒度大小必须足够大,以有效利用平行性。第5章涵盖了紧密耦合的MIMD体系结构,这些体系结构利用线程级平行性,因为多个协作线程并行操作。第6章涵盖了松散耦合的MIMD体系结构——特别是集群和仓库规模计算机——这些结构利用请求级平行性,其中许多独立任务可以自然地并行进行,几乎不需要通信或同步。

这一分类法是一个粗略模型,因为许多并行处理器是SISD、SIMD和MIMD类别的混合体。尽管如此,它在我们将要讨论的计算机设计空间上提供了一个有用的框架。

1.3 Defining Computer Architecture

计算机设计师面临的任务十分复杂:确定新计算机的重要属性,然后在成本、电力和可用性限制内,设计出最大化性能和能效的计算机。这个任务涉及多个方面,包括指令集设计、功能组织、逻辑设计和实现。实现可能包括集成电路设计、封装、电源和散热。优化设计需要对编译器、操作系统、逻辑设计和封装等广泛技术有深入了解。

几十年前,“计算机架构”这个术语通常仅指指令集设计。计算机设计的其他方面被称为实现,常常暗示实现不够有趣或挑战性较小。我们认为这种看法是不正确的。架构师或设计师的工作远不止于指令集设计,其他方面的技术难题可能比指令集设计中的更具挑战性。我们将在快速回顾指令集架构之后,描述计算机架构师面临的更大挑战。

指令集架构:计算机架构的狭隘视角

在本书中,我们使用“指令集架构”(ISA)来指代实际的程序员可见指令集。ISA 作为软件和硬件之间的界限。这一指令集架构的简要回顾将使用 80x86、ARMv8 和 RISC-V 的例子来说明 ISA 的七个维度。最受欢迎的 RISC 处理器来自 ARM(高级 RISC 机器),在 2015 年出货了 148 亿片,相当于 80x86 处理器出货量的 50 倍。附录 A 和 K 提供了更多关于这三种 ISA 的细节。

RISC-V(“RISC 五”)是加州大学伯克利分校开发的现代 RISC 指令集,响应了业界的需求,免费开放供使用。除了完整的软件栈(编译器、操作系统和模拟器)外,还有多个 RISC-V 实现可供定制芯片或现场可编程门阵列使用。RISC-V 在第一个 RISC 指令集问世 30 年后开发,继承了其前身的优良理念——大量寄存器、易于流水线的指令和精简的操作集,同时避免了它们的遗漏或错误。它是一个免费的、开放的、优雅的 RISC 架构示例,因此包括 AMD、Google、HP 企业、IBM、微软、英伟达、高通、三星和西部数据在内的 60 多家公司加入了 RISC-V 基金会。我们在本书中使用 RISC-V 的整数核心 ISA 作为示例 ISA。

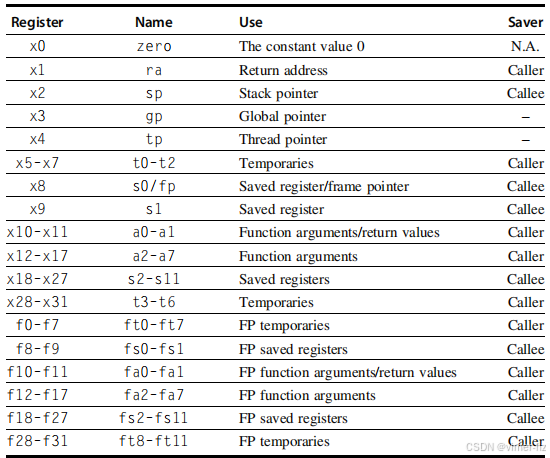

1. ISA 类别——今天几乎所有的 ISA 都被归类为通用寄存器架构,其中操作数可以是寄存器或内存位置。80x86 具有 16 个通用寄存器和 16 个可以存储浮点数据的寄存器,而 RISC-V 拥有 32 个通用寄存器和 32 个浮点寄存器(见图 1.4)。这一类别中的两个流行版本是寄存器-内存 ISA,例如 80x86,它可以在许多指令中访问内存,以及加载-存储 ISA,例如 ARMv8 和 RISC-V,它只能通过加载或存储指令访问内存。自 1985 年以来公布的所有 ISA 都是加载-存储类型。

图 1.4 RISC-V 寄存器、名称、用途及调用约定。除了 32 个通用寄存器(x0–x31),RISC-V 还有 32 个浮点寄存器(f0–f31),它们可以存储 32 位单精度数或 64 位双精度数。跨过程调用保持不变的寄存器标记为“被调用者”保存。

2. 内存寻址——几乎所有的桌面和服务器计算机,包括 80x86、ARMv8 和 RISC-V,都使用字节寻址来访问内存操作数。一些架构(如 ARMv8)要求对象必须对齐。如果在字节地址 A 处访问一个大小为 s 字节的对象,当且仅当 A mod s = 0 时,该访问才是对齐的。(参见第 A-8 页的图 A.5。)80x86 和 RISC-V 不要求对齐,但如果操作数对齐,访问速度通常会更快。

3. 寻址模式——除了指定寄存器和常数操作数外,寻址模式还指定内存对象的地址。RISC-V 的寻址模式包括寄存器模式、立即数模式(用于常数)和位移模式,其中常数偏移量被加到寄存器上以形成内存地址。80x86 支持这三种模式,加上三种位移变体:无寄存器(绝对寻址)、两个寄存器(基于索引加位移),以及两个寄存器中一个寄存器乘以操作数的字节大小(基于缩放索引和位移)。它还有类似于最后三种模式的更多模式,但不包括位移字段,并且支持寄存器间接寻址、索引寻址和基于缩放索引的寻址。ARMv8 除了 RISC-V 的三种寻址模式外,还支持 PC 相对寻址、两个寄存器之和,以及两个寄存器之和,其中一个寄存器乘以操作数的字节大小。它还支持自增和自减寻址,其中计算出的地址替代形成地址时所用的寄存器之一的内容。

4. 操作数的类型和大小——像大多数指令集架构一样,80x86、ARMv8 和 RISC-V 支持 8 位(ASCII 字符)、16 位(Unicode 字符或半字)、32 位(整数或字)、64 位(双字或长整数)以及 IEEE 754 浮点数(32 位单精度和 64 位双精度)。80x86 还支持 80 位浮点数(扩展双精度)。

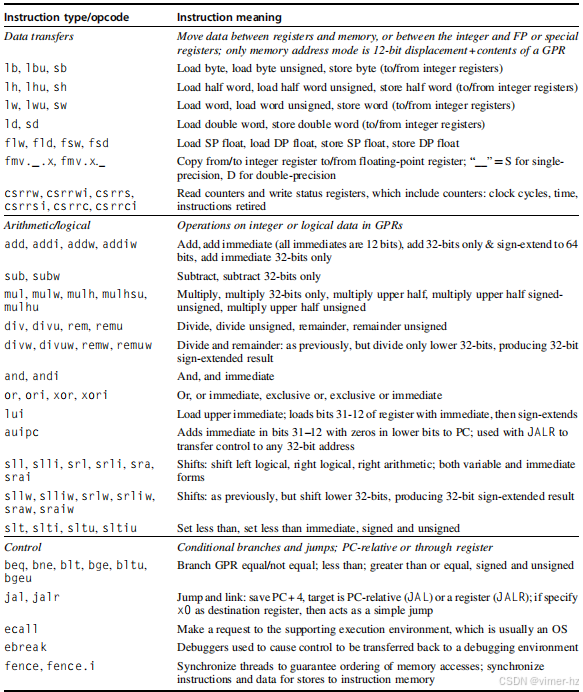

5. 操作——操作的一般类别包括数据传输、算术逻辑、控制(下文讨论)和浮点运算。RISC-V 是一种简单且易于流水线化的指令集架构,代表了 2017 年使用的 RISC 架构。图 1.5 总结了整数 RISC-V ISA,图 1.6 列出了浮点 ISA。80x86 具有更丰富、更大规模的操作集(见附录 K)。

图 1.5 RISC-V 指令集的一个子集。RISC-V 有一个基础指令集(R64I),并提供可选扩展:乘除运算(RVM)、单精度浮点(RVF)、双精度浮点(RVD)。此图包含了 RVM,而下一个图展示了 RVF 和 RVD。附录 A 提供了有关 RISC-V 的更多详细信息。

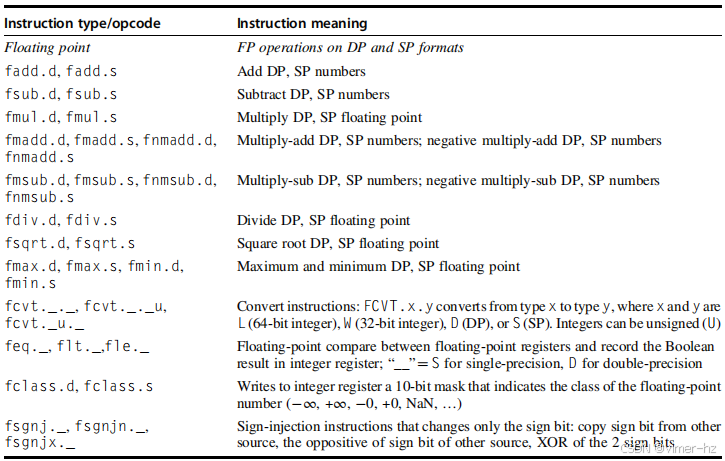

图 1.6 RISC-V 的浮点指令。RISC-V 有一个基础指令集(R64I),并提供可选的单精度浮点(RVF)和双精度浮点(RVD)扩展。SP = 单精度;DP = 双精度。

6. 控制流指令——几乎所有的指令集架构,包括这三种,都支持条件分支、无条件跳转、过程调用和返回。三者都使用 PC 相对寻址,其中分支地址由一个加到 PC 的地址字段指定。存在一些小的差异。RISC-V 的条件分支(BE、BNE 等)测试寄存器的内容,而 80x86 和 ARMv8 的分支测试算术/逻辑操作的条件码位。ARMv8 和 RISC-V 的过程调用将返回地址放在寄存器中,而 80x86 的调用(CALLF)将返回地址放在内存中的栈上。

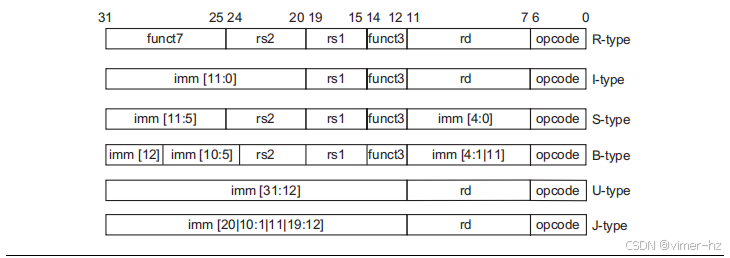

7. ISA 编码——编码有两种基本选择:固定长度和可变长度。所有 ARMv8 和 RISC-V 指令都是 32 位长,这简化了指令解码。图 1.7 显示了 RISC-V 的指令格式。80x86 的编码是可变长度的,范围从 1 到 18 字节。可变长度指令可能占用的空间比固定长度指令少,因此为 80x86 编译的程序通常比为 RISC-V 编译的同一程序要小。注意,之前提到的选择将影响指令如何编码成二进制表示。例如,寄存器数量和寻址模式数量对指令大小有显著影响,因为寄存器字段和寻址模式字段在单条指令中可以出现多次。(注意,ARMv8 和 RISC-V 后来提供了扩展,称为 Thumb-2 和 RV64IC,分别提供 16 位和 32 位长度的指令,以减少程序大小。这些紧凑版本的 RISC 架构的代码大小小于 80x86。见附录 K。)

图 1.7 基础 RISC-V 指令集架构格式。所有指令都是 32 位长。R 格式用于整数寄存器到寄存器的操作,如 ADD、SUB 等。I 格式用于加载和立即数操作,如 LD 和 ADDI。B 格式用于分支,J 格式用于跳转和链接。S 格式用于存储。为存储操作设置单独的格式使得三个寄存器说明符(rd、rs1、rs2)在所有格式中始终保持相同的位置。U 格式用于宽立即数指令(LUI、AUIPC)。

计算机架构师在指令集架构(ISA)设计之外面临的其他挑战在当前尤为突出,因为指令集之间的差异很小,而应用领域却各不相同。因此,从本书第四版开始,除了这一简要回顾之外,大部分指令集的材料都放在附录中(请参见附录 A 和 K)。

真正的计算机架构:设计组织和硬件以满足目标和功能需求

计算机的实现包含两个组成部分:组织和硬件。组织指计算机设计的高层次方面,如内存系统、内存互连以及内部处理器或中央处理单元(CPU)的设计(在这里实现算术、逻辑、分支和数据传输)。微架构这个术语也用来代替组织。例如,两个具有相同指令集架构但不同组织的处理器是 AMD Opteron 和 Intel Core i7。这两个处理器都实现了 x86 指令集,但它们的流水线和缓存组织非常不同。

由于每个微处理器都有多个处理器,"核心"这个术语也被用来指代处理器。因此,"多核"这一术语逐渐流行开来。鉴于几乎所有芯片都有多个处理器,中央处理单元(CPU)这个术语的使用逐渐减少。

硬件指计算机的具体细节,包括详细的逻辑设计和计算机的封装技术。通常,一系列计算机中包含具有相同指令集架构和非常相似组织的计算机,但它们在硬件实现的细节上有所不同。例如,Intel Core i7 和 Intel Xeon E7 几乎相同,但提供不同的时钟频率和内存系统,使得 Xeon E7 更适合服务器计算机。

在本书中,"架构"一词涵盖计算机设计的三个方面——指令集架构、组织或微架构以及硬件。

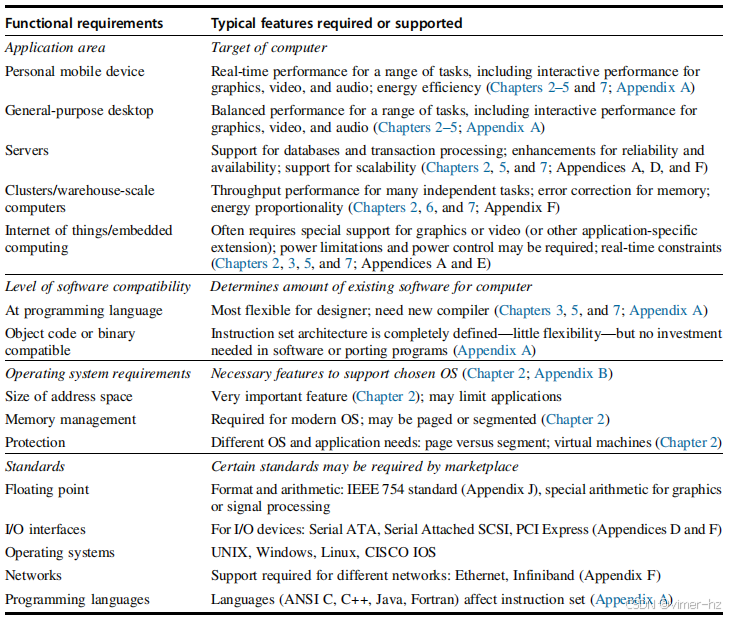

计算机架构师必须设计计算机以满足功能需求,同时达到价格、功耗、性能和可用性目标。图 1.8 总结了在设计新计算机时需要考虑的要求。架构师通常还必须确定功能需求,这可能是一项重要任务。这些需求可能是市场驱动的特定功能。应用软件通常决定计算机的使用方式,从而驱动某些功能需求的选择。如果针对特定指令集架构存在大量软件,架构师可能决定新计算机应实现现有的指令集。对于某一应用类别的大型市场可能会促使设计师在计算机中加入使其在该市场上具有竞争力的需求。后续章节将深入探讨这些要求和特性。

图 1.8 总结了架构师面临的一些最重要的功能需求。左侧列描述了需求的类别,而右侧列给出了具体的例子。右侧列还包含了涉及这些具体问题的章节和附录的参考。

架构师还必须关注技术和计算机使用中的重要趋势,因为这些趋势不仅影响未来的成本,还影响架构的持久性。

1.4 Trends in Technology

如果一个指令集架构要取得成功,它必须设计得能够经受计算机技术的快速变化。毕竟,一个成功的新指令集架构可能会持续几十年,例如,IBM 大型机的核心已经使用了超过 50 年。架构师必须为技术变化做好规划,以延长成功计算机的使用寿命。为了规划计算机的演变,设计师必须了解实现技术的快速变化。五种实现技术的变化速度非常快,对于现代实现至关重要:

■ 集成电路逻辑技术——历史上,晶体管密度每年大约增长 35%,四年内增加四倍。芯片面积的增长则较难预测且较慢,年增长范围为 10% 至 20%。两者的综合效应使得芯片上晶体管数量的传统增长率约为每年 40%–55%,即每 18–24 个月翻倍。这个趋势被称为摩尔定律。设备速度的提升则较慢,如下文所述。令人震惊的是,摩尔定律已不再成立。每片芯片上的设备数量仍在增加,但增长速度正在减缓。与摩尔定律时代不同,我们预计每一代新技术的翻倍时间将会被拉长。

■ 半导体 DRAM(动态随机存取内存)——这一技术是主内存的基础,我们将在第 2 章讨论它。DRAM 的增长已经显著放缓,从过去每三年翻四倍的速度减缓。2014 年时,8-gigabit DRAM 已开始出货,但 16-gigabit DRAM 要到 2019 年才能达到这一水平,并且似乎不会出现 32-gigabit DRAM(Kim, 2005)。第 2 章提到了一些可能在 DRAM 达到容量极限时取代它的技术。

■ 半导体 Flash(电可擦除可编程只读内存)——这种非易失性半导体存储器是 PMD 的标准存储设备,其快速增长的容量推动了其迅猛的发展速度。近年来,Flash 芯片的容量每年增加约 50%–60%,大约每 2 年翻倍。目前,Flash 存储器每比特的价格比 DRAM 便宜 8–10 倍。第 2 章描述了 Flash 存储器。

■ 磁盘技术——在 1990 年之前,磁盘的密度每年增加约 30%,每三年翻一倍。此后密度增幅上升至每年 60%,并在 1996 年增加到每年 100%。2004 年至 2011 年间,密度增幅回落至每年约 40%,即每两年翻一倍。最近,磁盘的改进速度减缓至每年不到 5%。增加磁盘容量的一种方法是保持相同的面积密度,增加更多的盘片,但在 3.5 英寸的硬盘中,已经有七个盘片叠在一英寸的深度内。最多还能再加一到两个盘片。提升真实密度的最后希望是使用一个小激光器在每个磁盘读写头上,将 30 纳米的点加热到 400°C,以便在其冷却之前进行磁性写入。目前尚不清楚热辅助磁记录(HAMR)是否能够经济且可靠地制造,尽管 Seagate 宣布计划在 2018 年开始有限生产 HAMR。HAMR 是硬盘驱动器在面积密度方面持续改进的最后机会,硬盘驱动器每比特的成本比 Flash 便宜 8–10 倍,比 DRAM 便宜 200–300 倍。此技术对服务器和仓储规模的存储至关重要,我们在附录 D 中详细讨论了这一趋势。

■ 网络技术——网络性能既依赖于交换机的性能,也依赖于传输系统的性能。我们在附录 F 中讨论了网络技术的趋势。

这些迅速变化的技术塑造了计算机的设计,考虑到速度和技术的提升,这种计算机的使用寿命可能为 3 到 5 年。关键技术如闪存的变化足够大,以至于设计师必须为这些变化进行规划。实际上,设计师们常常会设计出符合下一个技术发展的产品,因为当产品开始大规模生产时,下一代技术可能会更具成本效益或具有性能优势。传统上,成本的下降速度大约与密度的增加速度相同。

尽管技术不断改进,这些提高的影响可能会以离散的跃进形式出现,通常是因为达到了允许新功能的临界点。例如,当 MOS 技术在 1980 年代初期达到每片芯片上能够容纳 25,000 到 50,000 个晶体管的水平时,就可以制造出单芯片的 32 位微处理器。到 1980 年代末,第一层缓存也可以放在芯片上。通过消除处理器内部和处理器与缓存之间的芯片交叉,显著提高了成本效益和能效。这种设计在技术达到一定水平之前是完全不可行的。随着多核微处理器和每代核心数量的增加,即使是服务器计算机也越来越趋向于将所有处理器集成在单个芯片上。这种技术的临界点并不罕见,对各种设计决策有着重大影响。

**性能趋势:带宽与延迟**

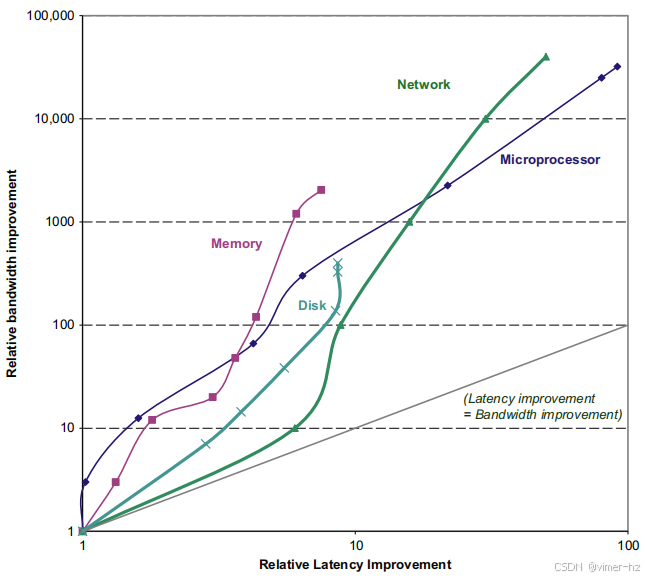

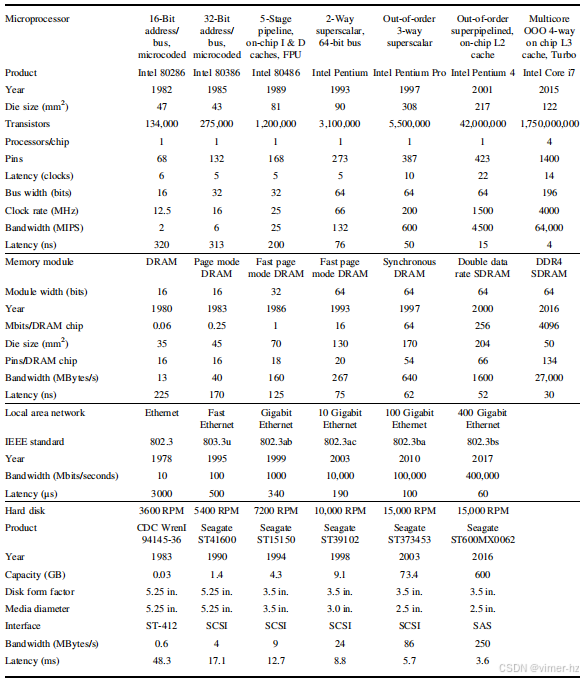

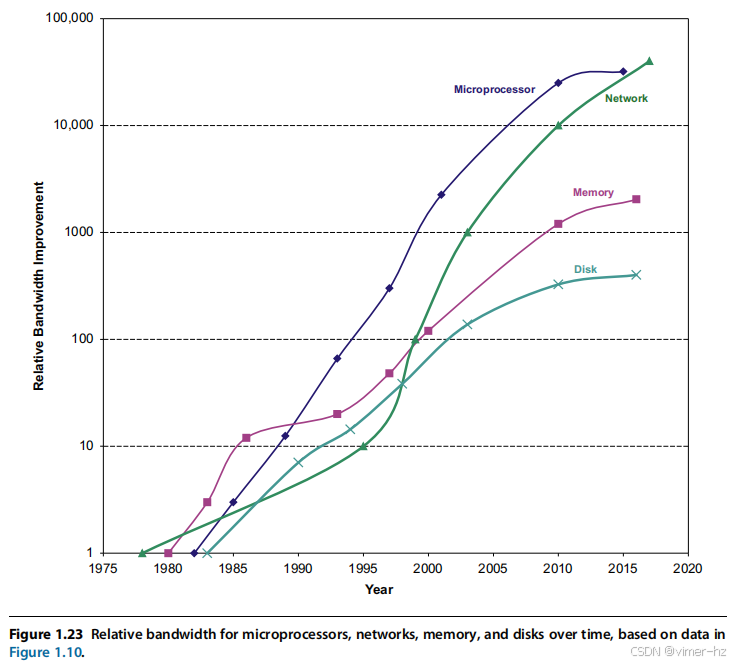

正如我们将在第1.8节中看到的,带宽或吞吐量是指在给定时间内完成的总工作量,例如磁盘传输的每秒兆字节数。相对而言,延迟或响应时间是指事件开始和完成之间的时间,例如磁盘访问的毫秒数。图1.9 绘制了微处理器、内存、网络和磁盘技术里程碑的带宽和延迟的相对改进。图1.10 对这些例子和里程碑进行了更详细的描述。

性能是微处理器和网络的主要区别因素,因此它们在带宽和延迟方面取得了最大的提升:带宽提高了32,000–40,000倍,而延迟降低了50–90倍。对于内存和磁盘来说,容量通常比性能更为重要,因此容量的提升更多,但带宽的进步仍然远远大于延迟的改进,带宽的提升达到400–2,400倍,而延迟的改进只有8–9倍。

显然,带宽在这些技术领域中超越了延迟,并且可能会继续保持这种趋势。一个简单的经验法则是,带宽的增长至少是延迟改进的平方倍。计算机设计师应据此进行规划。

**图1.9** 图示了图1.10中带宽和延迟里程碑的对数-对数图,相对于第一个里程碑。注意,延迟改善了8–91倍,而带宽提高了约400–32,000倍。除了网络技术外,我们注意到,在过去六年里,其他三种技术的延迟和带宽改进都较为温和:延迟改进了0%–23%,带宽改进了23%–70%。更新自Patterson, D., 2004年,延迟滞后于带宽。《计算机通讯协会通讯》47 (10), 71–75。

图1.10展示了在25至40年期间,微处理器、内存、网络和磁盘的性能里程碑。微处理器的里程碑包括多个IA-32处理器的代际进展,从16位总线的微编码80286到64位总线、多核、乱序执行的超级流水线Core i7。内存模块的里程碑从16位宽的普通DRAM发展到64位宽的第三代双倍数据率同步DRAM。以太网的速度从10 Mbit/s提升到400 Gbit/s。磁盘的里程碑基于旋转速度,从3600 RPM提升到15,000 RPM。每种情况展示的是最佳带宽,而延迟是指在没有争用的情况下完成一个简单操作的时间。更新自Patterson, D., 2004. 延迟滞后于带宽。Commun. ACM 47 (10), 71–75。

**晶体管性能与电线缩放**

集成电路工艺的特征由特征尺寸决定,即晶体管或电线在x或y维度上的最小尺寸。特征尺寸从1971年的10μm减少到2017年的0.016μm;实际上,我们已经更换了单位,因此2017年的生产被称为“16 nm”,7 nm芯片也在研发中。由于每平方毫米硅片上的晶体管数量由晶体管的表面积决定,因此晶体管的密度随着特征尺寸的线性减少而二次增加。

然而,晶体管性能的提升则更为复杂。随着特征尺寸的缩小,器件在水平维度上以平方的速度缩小,同时在垂直维度上也会缩小。垂直维度的缩小需要降低工作电压,以维持晶体管的正常操作和可靠性。这种缩放因素的组合导致了晶体管性能与工艺特征尺寸之间复杂的相互关系。粗略地说,在过去,晶体管性能随着特征尺寸的减小线性提高。晶体管数量随着线性提高的晶体管性能而二次增长,这既是挑战也是计算机架构师创造的机会!在微处理器的早期,密度的提高被用来快速从4位、8位、16位、32位到64位微处理器的发展。最近,密度的提高支持了每芯片多个处理器的引入、更宽的SIMD单元以及第2到第5章中讨论的许多预测执行和缓存的创新。

尽管晶体管一般会随着特征尺寸的减少而性能提升,但集成电路中的电线则不然。特别是,电线的信号延迟与其电阻和电容的乘积成正比。尽管特征尺寸缩小时,电线变得更短,但每单位长度的电阻和电容却会变差。这种关系复杂,因为电阻和电容依赖于工艺的详细方面、电线的几何形状、电线上的负载,甚至是与其他结构的邻接。偶尔有一些工艺改进,如引入铜,可以在一次性提高电线延迟方面提供帮助。

然而,总体而言,与晶体管性能相比,电线延迟的缩放效果较差,为设计师带来了额外的挑战。除了功耗限制外,电线延迟已经成为大型集成电路的主要设计障碍,通常比晶体管开关延迟更为关键。越来越多的时钟周期被信号在电线上的传播延迟消耗,但现在功耗在设计中比电线延迟扮演了更重要的角色。

1.5 Trends in Power and Energy in Integrated Circuits

今天,能源是几乎所有计算机类别面临的最大挑战。首先,必须将电力引入并在芯片上分配,现代微处理器使用数百个引脚和多个互连层来处理电源和接地。其次,电力作为热量散发出去,必须被移除。

**电力和能源:系统视角**

系统架构师或用户应如何考虑性能、电力和能源?从系统设计者的角度看,有三个主要关注点。首先,处理器的最大功耗是多少?满足这一需求对于确保正常操作至关重要。例如,如果处理器试图抽取超过电源系统可提供的电力(通过抽取超过系统能供给的电流),通常会导致电压下降,从而可能导致设备故障。现代处理器在功耗上差异很大,具有高峰电流,因此它们提供了电压调整方法,使处理器能够在更宽的范围内降低速度并调节电压。这显然会降低性能。

其次,什么是持续功耗?这个指标通常被称为热设计功耗(TDP),因为它决定了冷却需求。TDP既不是峰值功耗(通常高出1.5倍),也不是在特定计算期间实际消耗的平均功耗(可能更低)。系统的典型电源通常会超出TDP,而冷却系统通常设计为匹配或超出TDP。如果冷却不足,处理器的结温可能超过其最大值,从而导致设备故障甚至永久损坏。现代处理器提供了两种帮助管理热量的功能,因为最高功耗(因此热量和温度升高)可能超过TDP规定的长期平均值。首先,当热温度接近结温极限时,电路会降低时钟频率,从而减少功耗。如果这种方法不成功,第二种热过载保护机制会激活,关闭芯片。

设计师和用户需要考虑的第三个因素是能效。请记住,功率只是单位时间的能量:1瓦特=1焦耳每秒。比较处理器时,选择能量还是功率作为指标更合适?通常,能量是更好的指标,因为它与特定任务和完成该任务所需的时间相关。特别地,完成工作负载所需的能量等于平均功率乘以工作负载的执行时间。因此,如果我们想知道哪种处理器对特定任务更高效,我们需要比较执行任务的能量消耗(而不是功率)。例如,处理器A的平均功耗可能比处理器B高20%,但如果A在B所需时间的70%内完成任务,其能量消耗将是1.2×0.7=0.84,这显然更好。

有人可能会认为,在大型服务器或云计算中,考虑平均功率就足够了,因为工作负载通常被假定为无限的,但这具有误导性。如果我们的云计算中使用的是处理器B而不是A,那么在消耗相同能量的情况下,云计算完成的工作将会更少。使用能量来比较不同选择可以避免这个陷阱。无论是对于大型云计算还是智能手机,比较能量总是正确的,因为云计算的电费和智能手机的电池寿命都由能量消耗决定。

什么时候功耗是一个有用的度量?主要的合法用途是作为限制:例如,一个空气冷却的芯片可能被限制在100瓦特。如果工作负载固定,可以将其用作指标,但这只是每任务能量的真实指标的一个变体。

微处理器中的能量和功率

在微处理器中,CMOS芯片的传统主要能量消耗来源于切换晶体管,也称为动态能量。每个晶体管所需的能量与晶体管驱动的电容负载和电压的平方的乘积成正比。

这个公式表示逻辑转换脉冲的能量,例如从0到1再到0,或从1到0再到1。单次转换(0到1或1到0)的能量则为:

每个晶体管所需的功率仅仅是单次转换的能量乘以转换频率的乘积。

对于一个固定的任务,降低时钟频率可以减少功率,但不会减少能量。显然,通过降低电压可以大幅减少动态功率和能量,因此在过去的20年里,电压从5伏降到了不到1伏。电容负载则是由连接到输出端的晶体管数量和技术决定的,技术决定了导线和晶体管的电容值。

**示例**

一些现代微处理器设计为具有可调电压,因此电压降低15%可能会导致频率降低15%。这对动态能量和动态功率的影响是什么?

**答案**

由于电容未改变,能量的变化比例是电压的比例。

这将能量减少到原始能量的大约72%。对于功率,我们需要计算频率的比例。

将功率减少到原始功率的大约61%。

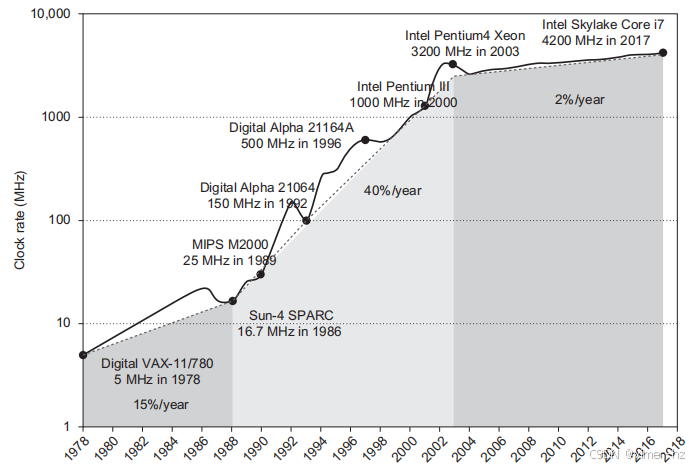

随着我们从一个处理过程移动到下一个,晶体管切换数量和切换频率的增加主导了负载电容和电压的减少,导致功耗和能量的总体增长。早期的微处理器消耗不到1瓦,而第一代32位微处理器(如Intel 80386)约消耗2瓦,而4.0 GHz的Intel Core i7-6700K则消耗95瓦。鉴于这些热量必须从约1.5厘米见方的芯片中散发出来,我们已接近空气冷却的极限,这也是我们近十年来一直面临的困境。根据前述公式,如果我们不能降低电压或增加每芯片的功率,则时钟频率的增长预计将会放缓。图1.11显示,自2003年以来,即使是每年表现最优的微处理器,时钟频率的增长确实变得缓慢。值得注意的是,这段时钟频率平稳的时期对应于图1.1中性能改善缓慢的阶段。分配功率、去除热量和防止热点变得越来越困难。现在,能源是使用晶体管的主要限制因素,以前则是原材料硅的面积。因此,现代微处理器提供了许多技术来提高能效,尽管时钟频率保持平稳和电压恒定:

图1.11 显示了微处理器时钟频率的增长情况。从1978年到1986年,时钟频率每年提高不到15%,而性能每年提高22%。在1986年到2003年期间的“文艺复兴时期”,性能每年提高了52%,而时钟频率几乎每年增加了40%。从那时起,时钟频率几乎保持平稳,每年增长不到2%,而单核处理器性能最近仅提高了3.5%每年。

1. **做好无事的处理**。如今,大多数微处理器会关闭闲置模块的时钟以节省能量和动态功率。例如,如果没有浮点指令执行,则浮点单元的时钟会被禁用。如果某些核心闲置,则它们的时钟也会停止。

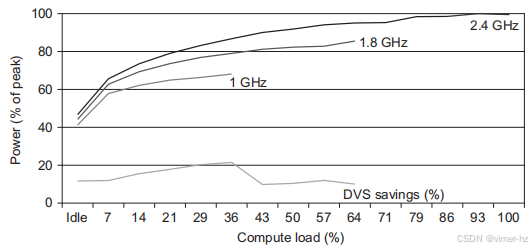

2. **动态电压-频率调整(DVFS)**。第二种技术直接来源于前述公式。PMD、笔记本电脑甚至服务器在低活动期间不需要以最高时钟频率和电压运行。现代微处理器通常提供几个时钟频率和电压选项,以使用较低的功率和能量。图1.12展示了在工作负载缩小时,服务器通过DVFS的潜在功率节省情况,分别为3种不同的时钟频率:2.4、1.8和1 GHz。总体服务器功率节省约为每两步10%–15%。

图1.12 显示了使用AMD Opteron微处理器、8 GB DRAM和一个ATA磁盘的服务器的能耗节省情况。在1.8 GHz时,服务器最多可以处理三分之二的工作负载而不会造成服务级别违规,而在1 GHz时,服务器只能安全地处理三分之一的工作负载(参见Barroso和Hölzle, 2009年,第5.11图)。

3. **针对典型情况设计**。由于PMD和笔记本电脑常常处于闲置状态,内存和存储提供低功耗模式以节省能量。例如,DRAM具有一系列逐渐降低功耗的模式,以延长PMD和笔记本电脑的电池寿命,还有提案提出当磁盘未使用时以更慢的速度旋转以节省功率。然而,在这些模式下无法访问DRAM或磁盘,因此必须返回完全活动模式以进行读写,无论访问率多低。如前所述,PC的微处理器已被设计为在高操作温度下重负荷使用,依赖于芯片上的温度传感器检测何时应自动减少活动以避免过热。这种“紧急减速”允许制造商设计更典型的情况,然后依靠这一安全机制,以防有人运行的程序消耗的功率远超出正常范围。

4. **超频**。英特尔在2008年开始提供Turbo模式,在这种模式下,芯片会判断在短时间内以更高的时钟频率运行是安全的,可能只在几个核心上运行,直到温度开始上升。例如,3.3 GHz的Core i7在短时间内可以以3.6 GHz运行。实际上,自2008年以来,图1.1中显示的每年最高性能的微处理器都提供了约10%的临时超频。对于单线程代码,这些微处理器可以关闭所有核心,只保留一个核心并让其以更高的速度运行。需要注意的是,尽管操作系统可以关闭Turbo模式,但一旦启用后没有通知,因此程序员可能会因为环境温度变化而发现他们的程序性能有所波动!

虽然动态功率通常被认为是CMOS中功耗的主要来源,但静态功率也成为了一个重要问题,因为即使晶体管处于关闭状态,泄漏电流仍会流动。

![]()

也就是说,静态功率与设备数量成正比。因此,即使晶体管处于空闲状态,增加晶体管数量也会增加功耗,而且晶体管尺寸较小的处理器中电流泄漏增加。因此,为了控制泄漏导致的损耗,低功耗系统甚至关闭非活动模块的电源(电源门控)。2011年的目标是使泄漏占总功耗的25%,但在高性能设计中,泄漏有时远远超过这一目标。这些芯片的泄漏可能高达50%,部分原因是需要电力来维持存储值的大容量SRAM缓存。(SRAM中的S代表静态。)停止泄漏的唯一希望是关闭芯片子集的电源。

最后,由于处理器只是整个系统能源成本的一部分,使用一个更快但能效较低的处理器来让其余系统进入睡眠模式是有意义的。这种策略被称为“竞速停止”。能源的重要性提高了对创新效率的审查,因此主要评估标准现在是每焦耳的任务数或每瓦特的性能,而不是过去的每平方毫米硅的性能。这一新指标影响了并行性的方法,我们将在第4章和第5章中看到。

计算机架构的变革源于能源限制

随着晶体管改进的减缓,计算机架构师必须寻找其他途径以提高能效。如今,在给定的能量预算下,设计一个晶体管数量过多以至于无法同时开启的微处理器已变得简单。这种现象被称为“黑硅”,因为芯片的大部分由于热限制而无法在任何时刻都保持启用。这一观察促使架构师重新审视处理器设计的基础,以寻求更高的能源成本性能。

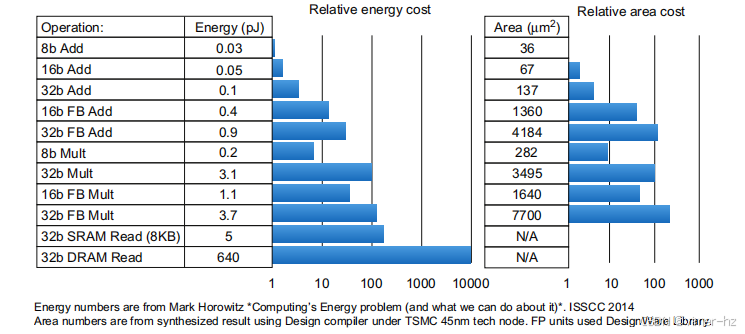

图1.13列出了现代计算机构建块的能源成本和面积成本,揭示了意外的比例差异。例如,32位浮点加法所用的能量是8位整数加法的30倍。面积差异更大,达到60倍。然而,最大的差距在于内存;32位DRAM访问所需的能量是8位加法的20,000倍。小型SRAM的能效是DRAM的125倍,这突显了缓存和内存缓冲区的精确使用的重要性。

图1.13 比较了算术运算的能量和芯片面积,以及对SRAM和DRAM访问的能量成本。[Azizi][Dally]。面积数据基于TSMC 45纳米技术节点。

新的设计原则是最小化每任务的能量,再结合图1.13中的相对能量和面积成本,启发了计算机架构的新方向,这将在第7章中描述。特定领域处理器通过减少广泛的浮点运算并部署专用内存以减少对DRAM的访问来节省能量。它们利用这些节省来提供比传统处理器多10到100倍的(更窄的)整数运算单元。尽管这些处理器仅执行有限的任务,但它们比通用处理器在速度和能效上表现得更为出色。就像医院有全科医生和医疗专家一样,在这个注重能效的世界里,计算机可能会是能够执行任何任务的通用核心与在某些方面表现极其出色且更具成本效益的专用核心的组合。

1.6 Trends in Cost

尽管在某些计算机设计中——特别是超级计算机——成本往往不那么重要,但对成本敏感的设计变得越来越重要。事实上,在过去的35年里,利用技术进步降低成本并提高性能一直是计算机行业的一个主要主题。教科书通常忽略成本与性能的关系,因为成本会发生变化,从而使书籍过时,并且这些问题复杂且在行业领域之间有所不同。然而,对于计算机架构师来说,了解成本及其因素对于做出明智的决策是至关重要的,特别是在成本是一个问题的情况下是否应该在设计中加入新功能(可以想象,如果架构师在设计摩天大楼时没有关于钢梁和混凝土成本的信息,那将是怎样的情景!)。本节将讨论影响计算机成本的主要因素以及这些因素随时间变化的情况。

**时间、产量与商品化的影响**

即使没有显著的基础实施技术改进,制造计算机组件的成本随着时间的推移也会下降。推动成本下降的基本原则是学习曲线——制造成本随着时间的推移而降低。学习曲线的最佳测量方式是通过良率的变化来衡量——即通过测试程序的制造设备的百分比。无论是芯片、板卡还是系统,良率提高一倍的设计将使成本降低一半。

理解学习曲线如何提高良率对于预测产品生命周期内的成本至关重要。例如,DRAM每兆字节的价格长期以来已下降。由于DRAM的价格通常与成本密切相关——除非出现短缺或过剩——价格和成本紧密跟踪。

微处理器的价格也会随时间下降,但由于它们不像DRAM那样标准化,价格与成本之间的关系更为复杂。在激烈竞争的时期,价格通常与成本紧密跟踪,尽管微处理器供应商可能很少以亏损的价格出售。

产量是决定成本的第二个关键因素。增加产量会以多种方式影响成本。首先,它减少了通过学习曲线所需的时间,这部分与制造的系统(或芯片)数量成正比。其次,产量降低了成本,因为它提高了采购和制造效率。作为经验法则,一些设计师估计,每增加一倍产量,成本大约下降10%。此外,产量减少了每台计算机必须摊销的开发成本,从而使成本和售价更加接近,同时仍能获利。

商品化是指由多个供应商以大批量销售的产品,且这些产品基本上是相同的。超市货架上几乎所有的产品都是商品化产品,如标准DRAM、闪存、显示器和键盘。在过去30年里,个人计算机行业的大部分已成为一个商品化业务,专注于生产运行微软Windows的台式机和笔记本电脑。

由于许多供应商提供几乎相同的产品,市场竞争非常激烈。当然,这种竞争缩小了成本和售价之间的差距,但也降低了成本。成本降低的原因在于商品化市场具有体量和明确的产品定义,这使得多个供应商能够竞争构建商品化产品的组件。因此,由于组件供应商之间的竞争和供应商能够实现的体量效率,总体产品成本更低。这种竞争使得计算机业务的低端能够实现比其他领域更好的性价比,并在低端取得了更大的增长,尽管利润非常有限(这是任何商品化业务的典型情况)。

**集成电路的成本**

为什么计算机架构书籍中会有关于集成电路成本的部分?在竞争日益激烈的计算机市场中,标准部件——例如硬盘、闪存、DRAM等——已经占据了系统成本的很大一部分,因此集成电路的成本也成为了不同计算机成本中越来越重要的组成部分,尤其是在高需求和对成本敏感的市场中。事实上,随着PMD(便携式多媒体设备)越来越依赖于系统芯片(SOC),集成电路的成本占据了PMD成本的很大一部分。因此,计算机设计师必须了解芯片的成本,以便更好地理解当前计算机的成本。

图1.16:这个200毫米直径的硅片上装有RISC-V芯片,由SiFive设计。它包含两种类型的RISC-V芯片,使用了较旧、更大的加工工艺线。FE310芯片的尺寸为2.65毫米 × 2.72毫米,而SiFive测试芯片的尺寸为2.89毫米 × 2.72毫米。该硅片包含1846个FE310芯片和1866个测试芯片,共计3712个芯片。

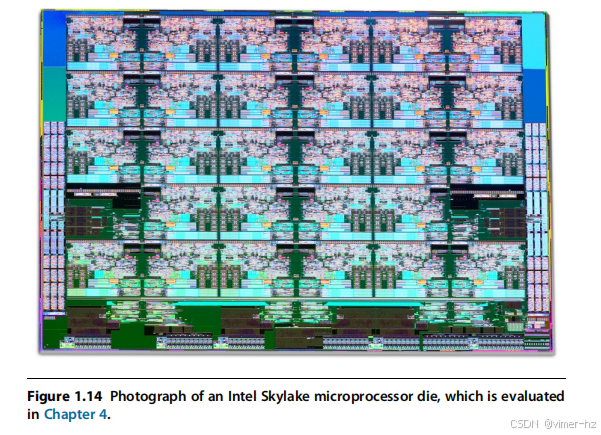

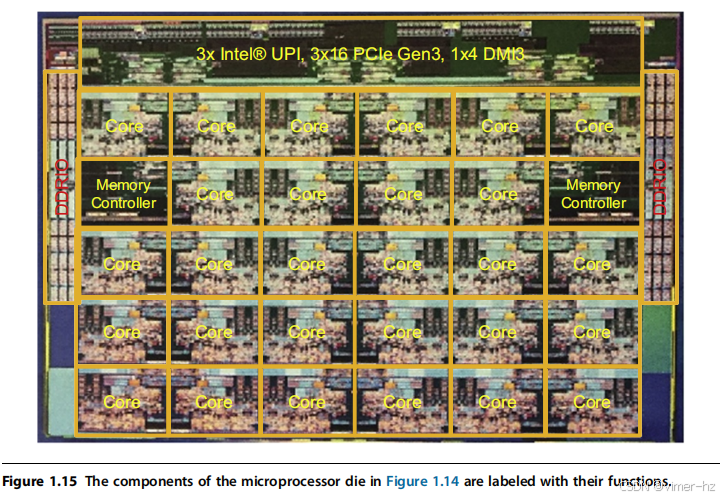

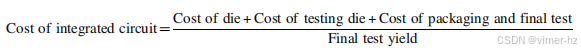

尽管集成电路的成本已呈指数下降,但硅片制造的基本过程并没有改变:硅片仍然被测试并切割成芯片,然后进行封装(参见图1.14-1.16)。因此,封装集成电路的成本是

在本节中,我们将重点讨论芯片的成本,并在最后总结测试和封装中的关键问题。要学会预测每片硅片上的良品数量,首先需要了解每片硅片上能放置多少个芯片,然后预测这些芯片中有多少会正常工作。接下来,预测成本就变得简单了。

![]()

这个芯片成本方程的初始项最有趣的特点是其对芯片尺寸的敏感性,如下所示。

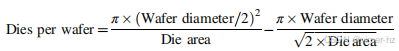

每片硅片上的芯片数量大致是硅片面积除以芯片面积。它可以通过以下公式更准确地估算:

第一个项是硅片面积(πr²)与芯片面积的比率。第二项补偿了“方块在圆孔中”的问题——圆形硅片边缘附近的矩形芯片。用圆的周长(πd)除以方形芯片的对角线大致可以得到边缘上芯片的数量。

例子:找出对于侧边长为1.5厘米和1.0厘米的芯片,300毫米(30厘米)硅片上每种芯片的数量。

答案:当芯片面积为2.25平方厘米时,

![]()

由于较大芯片的面积是较小芯片面积的2.25倍,因此每片硅片上大约有2.25倍数量的较小芯片。

![]()

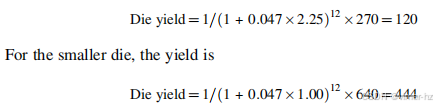

然而,这个公式只给出了每片硅片上芯片的最大数量。关键问题是:硅片上良品芯片的比例是多少,或芯片的良率是多少?一种简单的集成电路良率模型假设缺陷在硅片上随机分布,且良率与制造工艺的复杂性成反比,得出以下结果:

![]()

这个 Bose-Einstein 公式是通过观察许多制造线的良率而发展出的经验模型(Sydow,2006),至今仍然适用。硅片良率考虑了完全坏的硅片,因此不需要测试。为了简化,我们假设硅片良率为100%。每单位面积的缺陷数是随机制造缺陷的度量。2017年,对于28纳米工艺节点,缺陷数通常为每平方英寸0.08–0.10;对于更新的16纳米节点为0.10–0.30,因为这取决于工艺的成熟度(回忆一下之前提到的学习曲线)。相应的度量是28纳米工艺的每平方厘米0.012–0.016缺陷,16纳米工艺为0.016–0.047。最后,N 是一个称为工艺复杂性因子的参数,用来衡量制造难度。对于2017年的28纳米工艺,N 为7.5–9.5;对于16纳米工艺,N 在10到14之间。

示例:假设缺陷密度为每平方厘米0.047,N为12,计算边长分别为1.5厘米和1.0厘米的芯片的良品率。

答案:总芯片面积分别为2.25平方厘米和1.00平方厘米。对于较大的芯片,良品率为

结论是每片晶圆上的良品芯片数量。大尺寸芯片中不到一半是良品,而小尺寸芯片中接近70%是良品。

尽管许多微处理器的面积在1.00到2.25平方厘米之间,低端嵌入式32位处理器的面积有时仅为0.05平方厘米,用于嵌入式控制(如廉价的物联网设备)的处理器通常小于0.01平方厘米,而高端服务器和GPU芯片的面积可以达到8平方厘米。

考虑到对商品产品(如DRAM和SRAM)的巨大价格压力,设计师们已经加入了冗余以提高良品率。多年来,DRAM中通常会包括一些冗余存储单元,以容纳一定数量的缺陷。设计师们在标准SRAM和用于微处理器缓存的大型SRAM阵列中也使用了类似的技术。GPU为了同样的原因在84个处理器中包含了4个冗余处理器。显然,冗余条目的存在可以显著提高良品率。

在2017年,使用28纳米技术处理直径300毫米(12英寸)的晶圆的成本在4000到5000美元之间,而16纳米晶圆的成本约为7000美元。假设处理后的晶圆成本为7000美元,那么1.00平方厘米的芯片的成本大约为16美元,而2.25平方厘米芯片的成本约为58美元,几乎是稍大两倍的芯片成本的四倍。

计算机设计师应记住芯片成本的哪些因素?制造工艺决定了晶圆成本、晶圆良品率以及单位面积的缺陷数量,因此设计师唯一可以控制的是芯片面积。在实际操作中,由于单位面积的缺陷数量较少,良品芯片的数量以及每个芯片的成本大致随着芯片面积的平方增长。计算机设计师通过在芯片上包含或排除哪些功能以及I/O引脚的数量来影响芯片大小,从而影响成本。

在计算机中使用之前,芯片必须经过测试(以区分良品和不良品)、封装,并在封装后再次测试。这些步骤都增加了显著的成本,使总成本增加了一半。

上述分析集中在生产功能芯片的可变成本上,这对于大批量集成电路来说是合适的。然而,对于低批量(少于100万件)的集成电路,固定成本中的一个非常重要的部分是掩模组的成本。集成电路过程中的每一步都需要一个单独的掩模。因此,对于现代高密度制造工艺(最多有10层金属层),16纳米的掩模成本约为400万美元,28纳米的掩模成本约为150万美元。

好消息是,半导体公司提供了“穿梭测试”服务,以大幅降低小型测试芯片的成本。它们通过将许多小设计放置在一个芯片上来摊销掩模成本,然后再将这些芯片拆分成更小的部分用于每个项目。因此,TSMC在2017年提供了80到100个未测试的28纳米工艺芯片,每个芯片的尺寸为1.57×1.57毫米,价格为30,000美元。尽管这些芯片很小,但它们为架构师提供了数百万个晶体管。例如,几个RISC-V处理器可以适配在这样的芯片上。

尽管穿梭测试有助于原型设计和调试,但它们并不能解决生产数万到十几万件的小批量生产问题。由于掩模成本可能继续上升,一些设计师正在将可重构逻辑纳入设计中,以增强零件的灵活性,从而减少掩模的成本影响。

### 成本与价格

随着计算机的商品化,制造一个产品的成本与产品售价之间的差距正在缩小。这些差距用于支付公司的研究与开发(R&D)、市场营销、销售、制造设备维护、建筑租金、融资成本、税前利润以及税费。许多工程师会惊讶地发现,大多数公司在研发上的支出仅占其收入的4%(在普通PC业务中)到12%(在高端服务器业务中),这些支出包括所有的工程费用。

### 制造成本与运营成本

在本书的前四版中,“成本”指的是建造计算机的成本,而“价格”指的是购买计算机的价格。随着Web规模计算(WSC)的出现,这些系统包含数以万计的服务器,运营计算机的成本在购买成本之外也变得相当重要。经济学家将这两种成本称为资本支出(CAPEX)和运营支出(OPEX)。

如第六章所示,服务器和网络的摊销购买价格大约是运营一个WSC的月度成本的一半,假设IT设备的短期寿命为3-4年。尽管这些基础设施的摊销期为10-15年,但每月运营成本中约40%用于电力消耗以及分配电力和冷却IT设备的基础设施。因此,为了降低WSC的运营成本,计算机架构师需要高效地使用能源。

1.7 Dependability

历史上,集成电路是计算机中最可靠的组件之一。尽管其引脚可能会受到威胁,通信通道可能会出现故障,但芯片内部的故障率非常低。随着特征尺寸逐渐缩小到16纳米及以下,这种传统观念正在发生变化,因为瞬态故障和永久性故障变得更加普遍,因此架构师必须设计系统以应对这些挑战。本节简要概述了可靠性问题,将术语和方法的正式定义留给附录D的第D.3节。

计算机在不同的抽象层次上设计和构建。我们可以递归地深入计算机,看到组件逐渐扩展为完整的子系统,直到我们遇到单个晶体管。尽管一些故障是广泛存在的,如电源丧失,但许多故障可以限制在模块中的单一组件。因此,一个层次的模块的完全失败在更高层次的模块中可能仅被视为组件错误。这种区分有助于找到构建可靠计算机的方法。

一个困难的问题是决定系统是否正常运行。这一理论问题在互联网服务普及后变得具体化。基础设施提供商开始提供服务水平协议(SLA)或服务水平目标(SLO),以保证其网络或电力服务的可靠性。例如,如果他们未能满足每月一定小时的协议,他们将向客户支付罚金。因此,SLA可以用于决定系统是运行还是停机。

系统在服务水平协议(SLA)方面在两种状态之间交替:

1. 服务完成,指按照规定交付服务。

2. 服务中断,指交付的服务与SLA不符。

这些状态之间的转换由故障(从状态1到状态2)或恢复(从状态2到状态1)引起。量化这些转换会产生两个主要的可靠性度量:

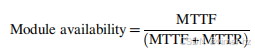

- 模块可靠性是指从参考初始时刻起,服务完成的持续时间(或等效地,故障时间)。因此,平均故障时间(MTTF)是一种可靠性度量。MTTF的倒数是故障率,通常以每十亿小时操作的故障数表示,或称为FIT(故障数)。例如,MTTF为1,000,000小时等于10^9 / 10^6或1000 FIT。服务中断的测量为平均修复时间(MTTR)。平均故障间隔时间(MTBF)是MTTF和MTTR之和。虽然MTBF广泛使用,但MTTF通常是更合适的术语。如果一组模块的寿命呈指数分布——即模块的年龄对故障概率无关——则该集合的总体故障率是模块故障率的总和。

- 模块可用性是指相对于完成和中断这两种状态之间交替的服务完成情况。对于具有修复功能的非冗余系统,模块可用性是

请注意,可靠性和可用性现在是可量化的度量标准,而不再是可靠性的同义词。根据这些定义,如果我们对组件的可靠性做出一些假设,并且假设故障是独立的,那么我们可以定量估计系统的可靠性。

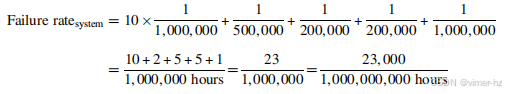

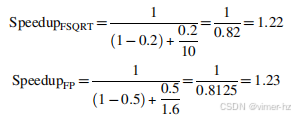

例子:假设一个磁盘子系统包含以下组件及其MTTF:

- 10个磁盘,每个磁盘的MTTF为1,000,000小时

- 1个ATA控制器,MTTF为500,000小时

- 1个电源,MTTF为200,000小时

- 1个风扇,MTTF为200,000小时

- 1根ATA电缆,MTTF为1,000,000小时

使用简化假设:寿命呈指数分布,故障是独立的,计算整个系统的MTTF。

答案:故障率的总和是

应对故障的主要方法是冗余,既可以是时间上的冗余(重复操作以查看是否仍然出错),也可以是资源上的冗余(让其他组件接管故障组件的工作)。一旦组件被替换且系统完全修复,系统的可靠性被认为和新系统一样好。让我们通过一个例子来量化冗余的好处。

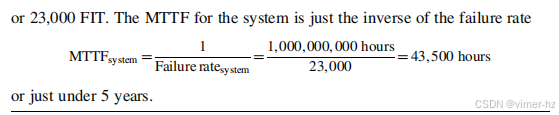

例子:磁盘子系统通常配备冗余电源以提高可靠性。使用上述组件和MTTF,计算冗余电源的可靠性。假设一个电源足以运行磁盘子系统,我们正在添加一个冗余电源。

答案:我们需要一个公式来显示当可以容忍一次故障且仍能提供服务时的预期情况。为了简化计算,我们假设组件的寿命呈指数分布且故障之间没有依赖性。冗余电源的MTTF是一个电源故障的平均时间除以另一个电源在第一个电源更换之前故障的概率。因此,如果第二次故障发生的可能性很小,那么这对电源的MTTF就会很大。

由于我们有两个电源且故障是独立的,一个电源故障的平均时间是MTTF电源/2。第二次故障的概率的一个很好的近似值是MTTR除以另一个电源故障的平均时间。因此,冗余电源对的合理近似值是

使用上述MTTF数字,如果我们假设人类操作员平均需要24小时才能发现电源故障并进行更换,那么故障容错电源对的可靠性是

1.8 Measuring, Reporting, and Summarizing Performance

当我们说一台计算机比另一台计算机更快时,我们指的是什么?手机用户可能会说一台计算机更快是因为一个程序运行的时间更短,而亚马逊网站管理员可能会说一台计算机更快是因为它每小时完成的事务更多。手机用户希望减少响应时间——即事件开始和完成之间的时间,也称为执行时间。WSC(大规模数据中心)操作员希望提高吞吐量——即在给定时间内完成的总工作量。

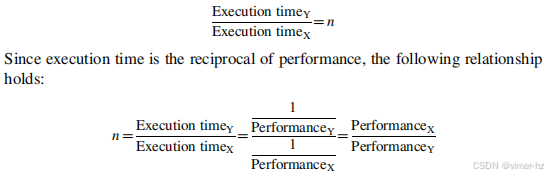

在比较设计方案时,我们通常希望比较两台不同计算机的性能,比如X和Y。在这里,“X比Y更快”这个短语指的是在给定任务上X的响应时间或执行时间低于Y。特别地,“X比Y快n倍”将意味着

短语“X的吞吐量是Y的1.3倍”在这里表示计算机X在单位时间内完成的任务数量是计算机Y的1.3倍。

不幸的是,在比较计算机性能时,时间并不总是被引用的指标。我们的观点是,唯一一致且可靠的性能度量是实际程序的执行时间,而所有提出的替代时间作为指标或实际程序作为测量对象的方法,最终都导致了误导性的声明或计算机设计中的错误。

即使是执行时间也可以根据我们统计的内容定义不同。最直接的时间定义称为挂钟时间、响应时间或经过时间,即完成任务的延迟,包括存储访问、内存访问、输入/输出活动、操作系统开销——所有内容。由于多程序设计,处理器在等待I/O时可能会处理其他程序,这可能不会最小化一个程序的经过时间。因此,我们需要一个术语来考虑这种活动。CPU时间承认了这种区别,指的是处理器计算的时间,不包括等待I/O或运行其他程序的时间。(显然,用户看到的响应时间是程序的经过时间,而不是CPU时间。)

那些经常运行相同程序的计算机用户将是评估新计算机的理想候选人。为了评估新系统,这些用户只需比较他们工作负载的执行时间——即他们在计算机上运行的程序和操作系统命令的混合体。然而,只有少数人处于这种理想状况。大多数人必须依赖其他方法来评估计算机,通常依靠其他评估者,希望这些方法能预测新计算机的性能。一种方法是基准程序,这是许多公司用来确定计算机相对性能的程序。

基准测试

测量性能的最佳基准选择是实际应用程序,例如第1.1节中提到的Google Translate。尝试运行比实际应用程序简单得多的程序通常会导致性能误区。以下是一些例子:

■ 核心程序,它们是实际应用程序中的小型关键部分。

■ 玩具程序,例如Quicksort,是由100行代码组成的初学者编程作业。

■ 合成基准,它们是为了模拟真实应用程序的特征和行为而发明的假程序,例如Dhrystone。

这三种基准方法如今都不再被信任,通常因为编译器作者和架构师可以密谋使计算机在这些替代程序上的表现看起来比在实际应用程序上更快。令人遗憾的是——尽管我们在本书第四版中抛弃了使用合成基准来表征性能的错误观念,因为我们认为所有计算机架构师都同意这已不再可信——合成程序Dhrystone在2017年仍然是嵌入式处理器最广泛引用的基准测试!

另一个问题是基准测试运行的条件。提高基准测试性能的一种方法是使用基准测试特定的编译器标志;这些标志通常会引起对许多程序来说非法的转换或会降低其他程序的性能。为了限制这种情况并提高结果的显著性,基准测试开发人员通常要求供应商为同一语言中的所有程序(如C++或C)使用一个编译器和一组标志。除了编译器标志的问题,另一个问题是是否允许源代码修改。对此问题有三种不同的解决方法:

1. 不允许修改源代码。

2. 允许修改源代码,但实际上几乎不可能。例如,数据库基准依赖于标准的数据库程序,这些程序有数千万行代码。数据库公司极不可能为某台特定计算机进行性能提升的修改。

3. 允许源代码修改,只要修改后的版本产生相同的输出。

基准设计者面临的关键问题是,允许修改源代码是否会反映实际应用,并为用户提供有用的见解,或者这些修改是否仅仅降低了基准作为真实性能预测工具的准确性。正如第七章所述,领域特定的架构师在为明确定义的任务创建处理器时,通常会选择第三种方案。

为了避免将所有资源集中于一个方案,基准应用程序的集合,称为基准套件,是衡量处理器在各种应用程序中性能的一个受欢迎的方式。当然,这些集合的质量取决于其组成的单个基准程序。然而,基准套件的一个关键优势是,它们能够通过其他基准程序来减少任何一个基准程序的弱点。基准套件的目标是准确地描述两台计算机的实际相对性能,特别是针对客户可能运行的、不在套件中的程序。

一个警示性的例子是电子设计新闻嵌入式微处理器基准联盟(EEMBC)的基准测试。这是一组41个核心程序,用于预测不同嵌入式应用的性能:汽车/工业、消费、网络、办公自动化和电信。EEMBC报告了未经修改的性能和“完全疯狂”性能,其中几乎允许任何操作。由于这些基准测试使用小核心程序,并且由于报告选项,EEMBC并没有成为一个良好的嵌入式计算机相对性能的预测工具。这种不成功是为什么Dhrystone,EEMBC试图替代的基准,遗憾地仍然在使用的原因。

最成功的标准化基准应用程序套件之一是SPEC(标准性能评估公司),其起源于20世纪80年代末期的努力,旨在提供更好的工作站基准。正如计算机行业随时间演变一样,对不同基准套件的需求也随之发展,目前有SPEC基准覆盖了许多应用程序类别。所有SPEC基准套件及其报告结果都可以在http://www.spec.org找到。

尽管我们在接下来的许多部分中将重点讨论SPEC基准,但也有许多基准被开发用于运行Windows操作系统的PC。

桌面基准

桌面基准测试分为两大类:处理器密集型基准测试和图形密集型基准测试,尽管许多图形基准测试也包括密集的处理器活动。SPEC最初创建了一个专注于处理器性能的基准集(最初称为SPEC89),它已经发展到第六代:SPEC CPU2017,继SPEC2006、SPEC2000、SPEC95、SPEC92和SPEC89之后。SPEC CPU2017包括10个整数基准测试(CINT2017)和17个浮点基准测试(CFP2017)。

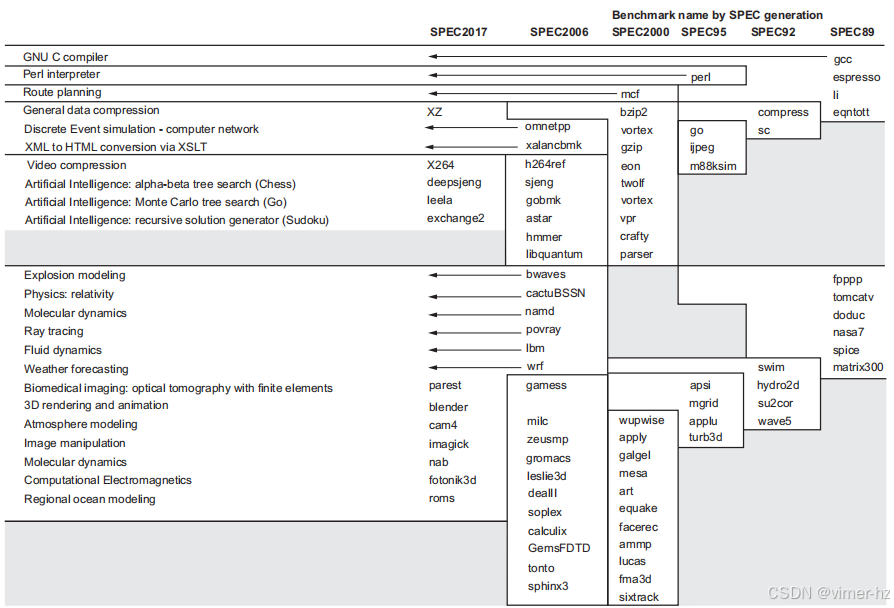

Figure 1.17 describes the current SPEC CPU benchmarks and their ancestry

图1.17展示了SPEC2017程序及SPEC基准测试随时间的演变,其中整数程序在上方,浮点程序在下方。在10个SPEC2017整数程序中,有5个用C编写,4个用C++编写,1个用Fortran编写。对于浮点程序,分布为3个用Fortran,2个用C++,2个用C,6个用混合C、C++和Fortran编写。图中显示了1989年、1992年、1995年、2000年、2006年和2017年版本中的82个程序。Gcc是该组的“资深者”。只有3个整数程序和3个浮点程序存活了三代或更多代。虽然有些程序从一代延续到另一代,但程序的版本会变化,基准的输入或大小通常会扩大,以增加运行时间并避免测量中的扰动或被除CPU时间以外的其他因素主导执行时间。左侧的基准描述仅适用于SPEC2017,不适用于早期版本。来自不同SPEC代的同一行程序通常无关,例如,fpppp不像bwaves那样是CFD代码。

SPEC基准测试是经过修改的实际程序,旨在提高可移植性并最小化I/O对性能的影响。整数基准测试包括C编译器的一部分、go程序和视频压缩。浮点基准测试包括分子动力学、光线追踪和天气预测。SPEC CPU套件对桌面系统和单处理器服务器的处理器基准测试都很有用。我们将在本书中看到这些程序的数据。然而,这些程序与现代编程语言和环境、以及第1.1节中描述的Google翻译应用程序相去甚远。它们中近一半至少部分是用Fortran编写的!它们甚至是静态链接的,而不是像大多数实际程序那样动态链接的。虽然SPEC2017应用程序本身可能真实,但并不令人振奋。SPECINT2017和SPECFP2017是否捕捉到21世纪计算的激动人心之处尚不明确。

在第1.11节中,我们将描述在开发SPEC CPU基准套件过程中出现的陷阱,以及维护有用且具有预测性的基准套件面临的挑战。

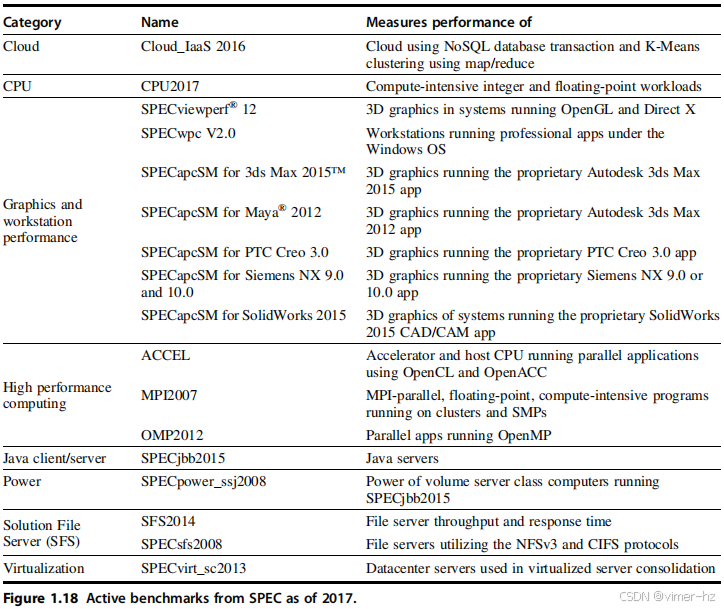

SPEC CPU2017专注于处理器性能,但SPEC提供了许多其他基准测试。图1.18列出了2017年活跃的17个SPEC基准测试。

服务器基准测试

正如服务器有多种功能一样,也有多种类型的基准测试。最简单的基准测试可能是面向处理器吞吐量的测试。SPEC CPU2017 使用 SPEC CPU 基准来构建一个简单的吞吐量基准,通过运行每个 SPEC CPU 基准的多个副本(通常与处理器数量相同),并将 CPU 时间转换为速率,从而测量多处理器的处理速率。这得出了一个叫做 SPECrate 的测量值,它衡量了请求级并行性。为了测量线程级并行性,SPEC 提供了所谓的高性能计算基准,涉及 OpenMP 和 MPI 以及 GPU 等加速器(见图 1.18)。

除了 SPECrate,大多数服务器应用程序和基准测试都涉及显著的 I/O 活动,包括存储或网络流量的基准测试,如文件服务器系统、网页服务器以及数据库和事务处理系统的基准测试。SPEC 提供了文件服务器基准(SPECSFS)和 Java 服务器基准(详见附录 D)。SPECvirt_Sc2013 评估虚拟化数据中心服务器的端到端性能。另一个 SPEC 基准测量功耗,详见第 1.10 节。

事务处理(TP)基准测试测量系统处理数据库访问和更新的事务能力。航空公司预订系统和银行 ATM 系统是 TP 的典型简单示例;更复杂的 TP 系统涉及复杂的数据库和决策制定。20 世纪 80 年代中期,一群关注的工程师成立了供应商独立的事务处理委员会(TPC),旨在创建现实且公平的 TP 基准。TPC 基准测试描述详见 http://www.tpc.org。

第一个 TPC 基准测试,TPC-A,于 1985 年发布,此后被多个不同的基准测试取代和增强。TPC-C 于 1992 年首次创建,模拟复杂的查询环境。TPC-H 模拟即席决策支持——查询相互独立,无法利用过去的查询知识来优化未来的查询。TPC-DI 基准测试是一个新的数据集成(DI)任务,也称为 ETL,是数据仓库的重要部分。TPC-E 是一个在线事务处理(OLTP)工作负载,模拟经纪公司客户账户。

考虑到传统关系数据库和 “No SQL” 存储解决方案之间的争议,TPCx-HS 测量使用 Hadoop 文件系统运行 MapReduce 程序的系统,TPC-DS 测量使用关系数据库或基于 Hadoop 的系统的决策支持系统。TPC-VMS 和 TPCx-V 测量虚拟化系统的数据库性能,而 TPC-Energy 为所有现有 TPC 基准增加了能源指标。

所有 TPC 基准都以每秒事务数来衡量性能。此外,它们包括响应时间要求,以确保吞吐量性能仅在响应时间限制内进行测量。为了模拟现实世界系统,更高的事务处理速率也与更大的系统相关,包括用户和应用事务的数据库。最后,基准系统的成本也必须包括在内,以便准确比较成本性能。TPC 修改了定价政策,以便为所有 TPC 基准提供单一规范,并允许验证 TPC 发布的价格。

**报告性能结果**

报告性能测量结果的指导原则应是可重复性——列出另一个实验者需要的所有信息,以便能够重复实验结果。SPEC 基准测试报告要求对计算机和编译器标志进行详尽描述,并且必须公布基准结果和优化结果。除了硬件、软件和基准调优参数的描述外,SPEC 报告还包含实际的性能时间,这些数据以表格形式和图形形式展示。TPC 基准测试报告则更为详尽,因为它必须包括基准审计结果和成本信息。这些报告是寻找计算系统真实成本的绝佳来源,因为制造商在高性能和成本效益上竞争。

**总结性能结果**

在实际计算机设计中,必须评估大量设计选择在一系列被认为相关的基准测试中的相对定量效益。同样,消费者在选择计算机时会依赖于基准测试的性能测量,这些基准测试理想情况下应与用户的应用程序类似。在这两种情况下,拥有一系列基准测试的测量结果是有用的,这样可以确保重要应用程序的性能与一或多个基准测试的结果相似,并且可以理解性能的变异性。在最佳情况下,该系列基准测试类似于应用空间的统计有效样本,但这样的样本需要比大多数系列中典型的更多的基准测试,并且需要随机抽样,这几乎没有基准测试系列使用。

一旦选择用基准测试系列来测量性能,我们希望能够用一个唯一的数字来总结该系列的性能结果。一种简单的方法是比较系列中程序执行时间的算术平均值。另一种方法是为每个基准添加一个权重因子,使用加权算术平均值作为总结性能的单一数字。一种方法是使用使所有程序在某个参考计算机上执行相等时间的权重,但这会使结果偏向于参考计算机的性能特征。

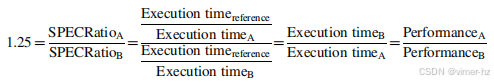

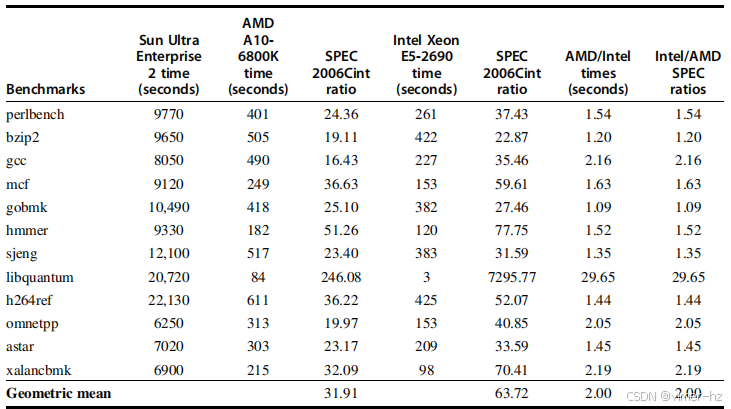

而不是选择权重,我们可以通过将参考计算机上的时间除以被评估计算机上的时间来规范化执行时间,从而得到与性能成比例的比率。SPEC 使用这种方法,称这种比率为 SPECRatio。它具有特别有用的属性,符合我们在本书中基准测试计算机性能的方式——即比较性能比率。例如,假设计算机 A 在某基准测试中的 SPECRatio 是计算机 B 的 1.25 倍;那么我们知道

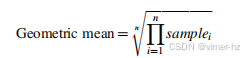

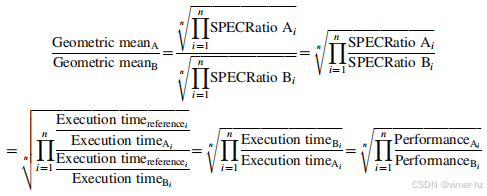

注意,当比较作为比率进行时,参考计算机上的执行时间会被消除,选择参考计算机也变得无关紧要,这正是我们始终使用的方法。图 1.19 给出了一个例子。由于 SPECRatio 是比率而非绝对执行时间,均值必须使用几何均值来计算。(因为 SPECRatios 没有单位,所以算术上比较 SPECRatios 是没有意义的。)公式是

在 SPEC 的情况下,samplei 是程序 i 的 SPECRatio。使用几何均值确保了两个重要属性:

1. 比率的几何均值等于几何均值的比率。

2. 几何均值的比率等于性能比率的几何均值,这意味着选择参考计算机是不相关的。

因此,使用几何均值的理由是充分的,特别是当我们使用性能比率进行比较时。

例子:证明几何均值的比率等于性能比率的几何均值,并且 SPECRatio 的参考计算机不重要。

解答:假设有两台计算机 A 和 B,以及每台计算机的一组 SPECRatios。

也就是说,计算机 A 和 B 的 SPECRatios 的几何均值比率等于 A 和 B 在所有基准测试中的性能比率的几何均值。图 1.19 使用 SPEC 的例子展示了这一有效性。

图 1.19 显示了 Sun Ultra 5(SPEC2006 的参考计算机)的 SPEC2006Cint 执行时间(以秒为单位),以及 AMD A10 和 Intel Xeon E5-2690 的执行时间和 SPECRatios。最后两列展示了执行时间比率和 SPEC 比率的比率。该图示例明了参考计算机在相对性能中的不相关性。执行时间的比率与 SPECRatios 的比率完全一致,几何均值的比率(63.72/31.91 ÷ 20.86 ≈ 2.00)与比率的几何均值(2.00)完全相同。第 1.11 节讨论了 libquantum,它的性能比其他 SPEC 基准测试高几个数量级。

1.9 Quantitative Principles of Computer Design

现在我们已经了解了如何定义、测量和总结性能、成本、可靠性、能耗和功耗,我们可以探索在计算机设计和分析中有用的指导方针和原则。本节介绍了设计中的重要观察点,以及用于评估替代方案的两个方程。

利用并行性

利用并行性是提高性能的重要方法之一。本书的每一章都有如何通过利用并行性来增强性能的示例。这里我们给出三个简短的例子,后续章节将对此进行详细阐述。

第一个例子是系统级别的并行性使用。为了提高典型服务器基准测试(如 SPECSFS 或 TPC-C)的吞吐量性能,可以使用多个处理器和多个存储设备。处理请求的工作负载可以在处理器和存储设备之间分配,从而提高吞吐量。能够扩展内存以及处理器和存储设备的数量被称为可扩展性,这对于服务器来说是一项宝贵的资产。将数据分布在多个存储设备上进行并行读写实现了数据级并行性。SPECSFS 还依赖于请求级并行性来使用多个处理器,而 TPC-C 则利用线程级并行性来加快数据库查询的处理速度。

在单个处理器级别,利用指令间的并行性对于实现高性能至关重要。实现这一点的最简单方法之一是通过流水线技术。(流水线技术在附录 C 中有更详细的解释,并且是第 3 章的主要内容。)流水线技术的基本思想是重叠指令执行,以减少完成指令序列的总时间。对流水线技术的一个关键见解是,并非每条指令都依赖于其直接前驱,因此可能可以完全或部分地并行执行这些指令。流水线技术是 ILP(指令级并行性)的最著名示例。

并行性还可以在详细的数字设计级别上得到利用。例如,集合关联缓存使用多个内存银行,这些内存银行通常会并行搜索以找到所需的项目。算术逻辑单元使用进位前瞻技术,这种技术利用并行性将计算和数值加法的过程从线性时间缩短到对数时间。这些都是数据级并行性的更多示例。

**局部性原理**

从程序的属性中得到了一些重要的基本观察。我们经常利用的最重要的程序属性是局部性原理:程序倾向于重用最近使用过的数据和指令。一个广泛接受的经验法则是,程序的90%执行时间花费在仅10%的代码上。局部性的一个含义是,我们可以基于程序最近的访问情况,合理地预测程序在不久的将来会使用哪些指令和数据。局部性原理也适用于数据访问,尽管它对数据访问的影响没有对代码访问那么强烈。

已经观察到两种不同类型的局部性。时间局部性表明,最近访问过的项很可能会很快再次被访问。空间局部性则表明,地址相近的项往往会在时间上紧密地被引用。我们将在第二章中看到这些原理的应用。

**关注常见情况**

计算机设计中也许最重要和最普遍的原则是关注常见情况:在进行设计权衡时,优先考虑频繁发生的情况而非不常见的情况。这个原则适用于确定如何分配资源,因为如果某种情况很常见,则改善的效果会更显著。关注常见情况不仅适用于能源管理,还适用于资源分配和性能优化。处理器的指令获取和解码单元可能比乘法器使用得更频繁,因此应优先优化它。这个原则也适用于可靠性方面。如果一个数据库服务器有50个存储设备与每个处理器配对,那么存储的可靠性将主导系统的整体可靠性。

此外,常见情况往往比不常见情况更简单,可以更快地处理。例如,在处理器中添加两个数字时,我们可以预期溢出是一个罕见的情况,因此可以通过优化更常见的没有溢出的情况来提高性能。这种强调可能会使溢出发生时的处理变慢,但如果这种情况很少见,那么通过优化正常情况来提升整体性能。

在本文中,我们将看到许多应用这一原则的实例。在应用这一简单原则时,我们必须决定什么是频繁发生的情况,并评估通过使这些情况更快处理可以提高多少性能。一条称为阿姆达尔定律的基本法则可以用来量化这一原则。

**阿姆达尔定律**

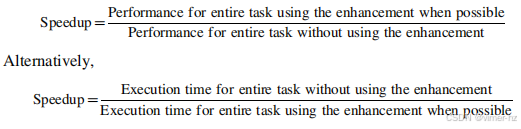

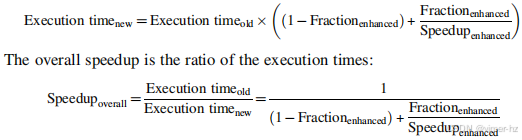

通过改进计算机的某些部分所能获得的性能提升可以使用阿姆达尔定律来计算。阿姆达尔定律指出,通过使用某种更快的执行模式所获得的性能提升受到该更快模式可以使用时间比例的限制。

阿姆达尔定律定义了通过使用特定特性所能获得的加速比。那么,加速比是什么呢?假设我们可以对计算机进行某种增强,从而在使用时提高性能。加速比是

加速比告诉我们,在使用增强功能的计算机上,任务运行速度相比于原始计算机提高了多少。阿姆达尔定律为我们提供了一种快速找到某项增强的加速比的方法,这依赖于两个因素:

1. 在原始计算机上可以利用增强功能的计算时间比例——例如,如果一个总执行时间为100秒的程序中,有40秒的时间可以使用增强功能,那么这个比例就是40/100。这个值称为Fractionenhanced,始终小于或等于1。

2. 增强执行模式带来的改进,即如果整个程序都使用增强模式,任务会运行得多快——这个值是原始模式的时间与增强模式的时间之比。如果增强模式对于程序的一部分需要4秒,而原始模式下是40秒,那么改进比为40/4,即10。我们称这个值为Speedupenhanced,始终大于1。

使用原始计算机加上增强模式的执行时间将是使用未增强部分的时间加上使用增强部分的时间。

例子

假设我们想要提升用于网页服务的处理器。新处理器在网页服务应用中的计算速度比旧处理器快10倍。假设原始处理器在40%的时间里忙于计算,而在60%的时间里等待I/O,那么通过引入增强功能所获得的总体加速比是多少?

答案

阿姆达尔定律表达了收益递减法则:通过对部分计算的改进所获得的加速增益会随着改进的增加而递减。阿姆达尔定律的一个重要推论是,如果增强功能仅能用于任务的一部分,那么我们不能使任务的加速比超过1减去那个比例的倒数。

在应用阿姆达尔定律时,一个常见的错误是混淆“转换为使用增强功能的时间比例”和“增强功能使用后的时间比例”。如果我们不是测量可以使用增强功能的计算时间,而是测量增强功能使用后的时间,那么结果将是不正确的!

阿姆达尔定律可以作为指导,帮助我们了解增强功能将如何改善性能,以及如何分配资源以提高性价比。显然,目标是将资源投入与时间支出的比例相匹配。阿姆达尔定律特别适用于比较两个方案的整体系统性能,但它也可以用于比较两种处理器设计方案,如以下示例所示。

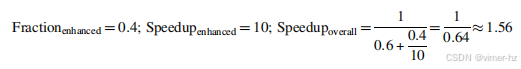

示例

在图形处理器中,一个常见的变换是平方根。浮点数(FP)平方根的实现性能差异很大,特别是在为图形设计的处理器中。假设浮点平方根(FSQRT)在一个关键的图形基准测试中占用了20%的执行时间。一个提议是提升FSQRT硬件,将这一操作的速度提高10倍。另一种方案是将所有浮点指令在图形处理器中的执行速度提高1.6倍;浮点指令负责应用程序执行时间的一半。设计团队认为,他们可以用与快速平方根相同的努力使所有浮点指令速度提高1.6倍。比较这两种设计方案。

答案

我们可以通过比较这两种方案的加速比来进行比较:

提升浮点操作的整体性能稍微更好,因为频率更高。

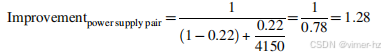

阿姆达尔定律不仅适用于性能。让我们重新审视第39页中的可靠性示例,假设通过冗余将电源的可靠性从200,000小时提高到830,000,000小时的平均无故障时间(MTTF),即提高了4150倍。

示例

磁盘子系统故障率的计算是

因此,可以改进的故障率比例是每百万小时中5次故障,相对于整个系统的23次故障,即0.22。

答案

可靠性改进将是

尽管一个模块的可靠性提高了令人印象深刻的4150倍,但从系统的角度来看,这一变化带来的好处是可测量的但相对较小。

在前面的示例中,我们需要新版本和改进版本所消耗的比例;通常很难直接测量这些时间。在下一部分中,我们将看到另一种进行此类比较的方法,这种方法基于一个将CPU执行时间分解为三个独立组件的方程式。如果我们知道某个替代方案如何影响这三个组件,就可以确定它的整体性能。此外,通常可以在硬件实际设计之前构建模拟器来测量这些组件。

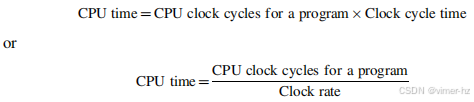

处理器性能方程

几乎所有计算机都是使用以恒定频率运行的时钟构建的。这些离散的时间事件称为时钟周期、时钟周期或时钟周期。计算机设计师通过时钟周期的持续时间(例如,1纳秒)或频率(例如,1 GHz)来表示时钟周期的时间。程序的CPU时间可以用两种方式来表示:

除了执行程序所需的时钟周期数外,我们还可以计算执行的指令数,即指令路径长度或指令计数(IC)。如果我们知道时钟周期数和指令计数,就可以计算每条指令的平均时钟周期数(CPI)。由于CPI更易于操作,并且我们在本章中将处理简单的处理器,因此使用CPI。设计师有时也使用每时钟周期指令数(IPC),它是CPI的倒数。CPI的计算公式为:

![]()

这个处理器性能指标提供了对不同指令集和实现风格的洞察,我们将在接下来的四章中广泛使用它。

通过转置前述公式中的指令计数,可以将时钟周期定义为 IC × CPI。这使我们可以在执行时间公式中使用CPI:

![]()

将第一个公式展开成测量单位的形式,可以展示各部分是如何组合在一起的:

![]()

正如这个公式所示,处理器性能依赖于三个特性:时钟周期(或频率)、每条指令的时钟周期数和指令计数。此外,CPU时间同样依赖于这三个特性;例如,任何一个特性的10%改善会导致CPU时间的10%改善。

不幸的是,由于改变每个特性的基本技术是相互依赖的,因此很难在完全隔离的情况下改变一个参数:

- 时钟周期时间——硬件技术和组织

- CPI——组织和指令集架构

- 指令计数——指令集架构和编译器技术

幸运的是,许多潜在的性能改进技术主要增强处理器性能的一个组件,同时对其他两个组件的影响较小或可预测。

在设计处理器时,有时计算总处理器时钟周期数是很有用的:

![]()

其中 ICi 代表指令 i 在程序中执行的次数,而 CPIi 代表指令 i 的平均每条指令时钟周期数。这个形式可以用来表示 CPU 时间为:

CPI 计算的后一种形式使用每个 CPIi 以及该指令在程序中出现的比例(即 ICi)。由于它必须包括流水线效应、缓存缺失以及其他内存系统的低效,CPIi 应该通过测量获得,而不仅仅是从参考手册的表格中计算得出。

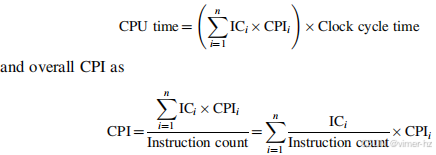

考虑我们在第 52 页的性能示例,这里修改为使用指令频率和指令 CPI 值的测量值,这些测量值实际上是通过模拟或硬件仪器获得的。

示例

假设我们进行了以下测量:

- 浮点运算的频率 = 25%

- 浮点运算的平均 CPI = 4.0

- 其他指令的平均 CPI = 1.33

- FSQRT 的频率 = 2%

- FSQRT 的 CPI = 20

答案

假设两种设计方案是将 FSQRT 的 CPI 降低到 2,或者将所有浮点运算的平均 CPI 降低到 2.5。使用处理器性能方程比较这两种设计方案。

首先,注意到只有 CPI 改变,时钟频率和指令计数保持不变。我们开始通过计算没有任何增强的原始 CPI。

通常可以测量处理器性能方程的组成部分。这些独立的测量是使用处理器性能方程相较于前述 Amdahl 定律的关键优势。特别是,测量一组指令负责的执行时间比例可能很困难。在实践中,这通常通过将每个指令的指令计数和 CPI 的乘积求和来计算。由于起点通常是单独的指令计数和 CPI 测量,因此处理器性能方程非常有用。

要将处理器性能方程作为设计工具使用,我们需要能够测量各种因素。对于现有处理器,通过测量获取执行时间很简单,而时钟速度是已知的。挑战在于发现指令计数或 CPI。大多数处理器包括执行的指令和时钟周期的计数器。通过定期监控这些计数器,还可以将执行时间和指令计数附加到代码的片段上,这对试图理解和优化应用程序性能的程序员非常有帮助。设计师或程序员通常会希望在比硬件计数器提供的更精细的级别上理解性能。例如,他们可能想知道 CPI 的具体原因。在这种情况下,使用的模拟技术类似于设计中的处理器。

有助于能源效率的技术,如动态电压频率调整和超频(参见第 1.5 节),使得使用这个方程变得更难,因为在测量程序时时钟速度可能会变化。一个简单的方法是关闭这些功能以使结果可重复。幸运的是,由于性能和能源效率通常高度相关——运行程序所需的时间更少通常会节省能源——因此考虑性能时通常可以不必担心 DVFS 或超频对结果的影响。

1.10 Putting It All Together: Performance, Price, and Power

在每章末尾出现的“综合应用”部分,我们提供了实际示例,这些示例使用了本章中的原则。在本节中,我们将使用SPECpower基准测试来观察小型服务器的性能和功耗性能指标。

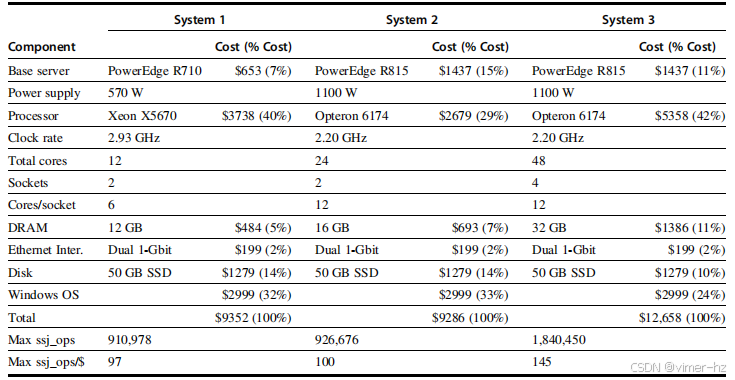

图1.20展示了我们正在评估的三款多处理器服务器及其价格。为了保持价格比较的公平性,所有服务器都是戴尔PowerEdge系列。第一款是PowerEdge R710,它基于Intel Xeon #85670微处理器,时钟频率为2.93 GHz。与第2–5章中的Intel Core i7-6700(具有20个核心和40 MB L3缓存)不同,这款Intel芯片具有22个核心和55 MB L3缓存,尽管核心本身是相同的。我们选择了一个双插槽系统(总共44个核心),配备128 GB的ECC保护2400 MHz DDR4 DRAM。下一款服务器是PowerEdge C630,拥有相同的处理器、插槽数量和DRAM。主要的区别在于它的机架安装包更小:730的高度为“2U”(3.5英寸),而630为“1U”(1.75英寸)。

图1.20 显示了三台戴尔PowerEdge服务器的测量情况及其2016年7月的价格。我们通过减去第二个处理器的成本来计算处理器的费用。类似地,我们通过查看额外内存的成本来计算整体内存的费用。因此,服务器的基本成本通过去除默认处理器和内存的估算成本进行调整。第5章描述了这些多插槽系统是如何连接在一起的,第6章则描述了集群是如何连接在一起的。

第三款服务器是由16台PowerEdge 630组成的集群,通过1 Gbit/s以太网交换机连接。所有服务器都运行Oracle Java HotSpot版本1.7的Java虚拟机(JVM)和Microsoft Windows Server 2012 R2 Datacenter版本6.3操作系统。

注意,由于基准测试的影响(见第1.11节),这些服务器配置异常。图1.20中的系统相对于计算量拥有较少的内存,并且仅有一个120 GB的固态硬盘。如果不需要相应增加内存和存储,增加核心的成本较低!

SPECpower使用了基于SPECjbb的现代Java软件栈,测量的性能指标是每秒事务数,称为ssj_ops。它不仅测试服务器的处理器,还测试缓存、内存系统以及多处理器互连系统。此外,它还测试JVM,包括JIT运行时编译器和垃圾回收器,以及底层操作系统的部分功能。

如图1.20的最后两行所示,性能赢家是16台R630服务器的集群,这并不令人意外,因为它是最昂贵的。性价比最高的是PowerEdge R630,但它在213和211 ssj-ops/$之间略微领先于集群。令人惊讶的是,尽管16节点集群比单节点大16倍,但其性价比与单节点差距不到1%。

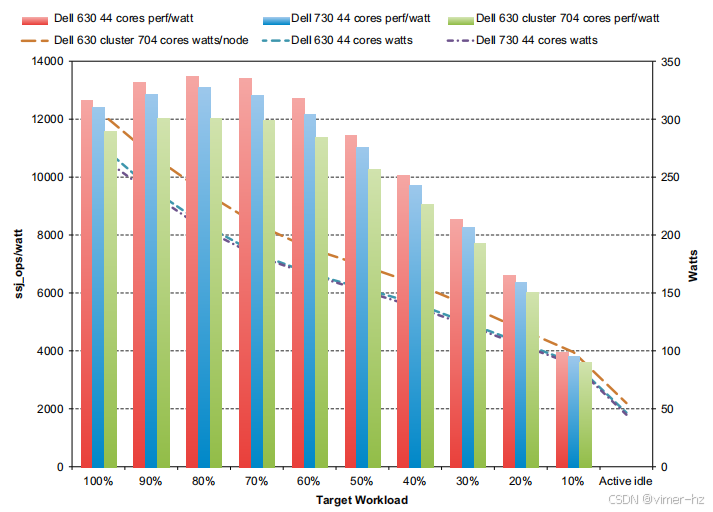

虽然大多数基准测试(和计算机架构师)只关注系统在峰值负载下的性能,但计算机很少在峰值负载下运行。事实上,第6章的图6.2显示了在Google对数万台服务器进行的6个月利用率测量结果,其中不到1%的服务器的平均利用率达到100%。大多数服务器的平均利用率在10%到50%之间。因此,SPECpower基准测试通过在10%到0%的负载范围内变化,捕捉到目标工作负载的功耗情况,其中0%称为活动空闲。

图1.21绘制了每瓦特ssj_ops(SSJ操作/秒)和目标负载从100%到0%变化时的平均功耗。Intel R730始终具有最低功耗,而单节点R630在每个目标负载水平下的ssj_ops每瓦特最佳。由于瓦特等于焦耳/秒,这个指标与每焦耳SSJ操作成正比。

![]()

图1.21显示了图1.20中三台服务器的功耗性能。ssj_ops/watt值在左侧轴上,与三个柱状图相关;瓦特值在右侧轴上,与三条折线相关。横轴显示目标工作负载,从100%到活动空闲变化。每个负载水平下,单节点R630的ssj_ops/watt表现最佳,但R730在每个负载水平下的功耗最低。

为了计算一个单一的数值用于比较系统的功耗效率,SPECpower使用了

三台服务器的整体ssj_ops/watt分别为:R730为10,802,R630为11,157,16台R630集群为10,062。因此,单节点R630具有最佳的功耗性能。将这些数据除以服务器价格,ssj_ops/watt/$1,000分别为:R730为879,R630为899,16节点R630集群(每节点)为789。因此,考虑到功耗后,单节点R630在性能/价格比方面仍然排名第一,但单节点R730的效率显著高于16节点集群。

1.11 Fallacies and Pitfalls

本节的目的是解释一些常见的误解或错误观念,你应该避免这些误解。我们称这些误解为谬论。在讨论一个谬论时,我们尝试提供一个反例。我们还讨论了一些陷阱——这些是容易犯的错误。陷阱通常是原则的普遍化,这些原则在有限的背景下是正确的。这些部分的目的是帮助你在设计计算机时避免这些错误。

**陷阱:所有的指数规律最终都将结束。**

第一个结束的是Dennard缩放。Dennard在1974年观察到,随着晶体管尺寸的减小,功率密度保持不变。如果晶体管的线性区域缩小了一倍,则电流和电压也减少了一倍,因此功耗下降了四倍。因此,芯片可以设计得更快,同时消耗更少的电力。Dennard缩放在观察到后的30年结束了,这并不是因为晶体管没有继续变小,而是因为集成电路的可靠性限制了电流和电压的进一步下降。阈值电压被压得非常低,以至于静态功耗成为整体功耗的重要部分。

接下来的是硬盘驱动器的减速。虽然没有硬盘的规律,但在过去30年里,硬盘的最大面积密度——决定了硬盘容量——每年提高了30%–100%。近年来,这一增长率已降至不到5%每年。增加每个硬盘的密度主要是通过增加更多的盘片来实现的。

接下来的是久负盛名的摩尔定律。已经有一段时间,芯片上的晶体管数量不再每一到两年翻一番。例如,2014年推出的DRAM芯片包含80亿个晶体管,而我们在2019年之前不会有16亿晶体管的DRAM芯片投入大规模生产,但摩尔定律预测64亿晶体管的DRAM芯片。

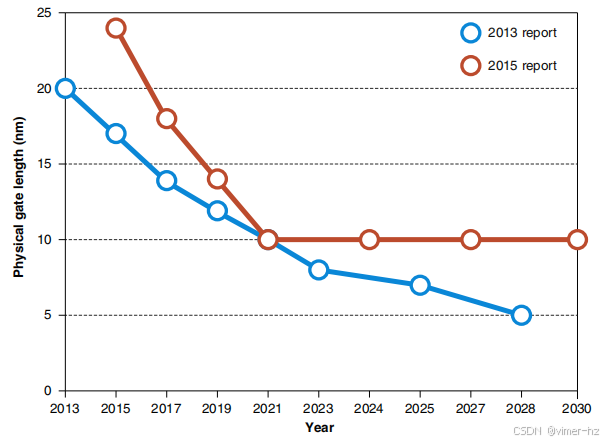

此外,平面逻辑晶体管缩放的实际终点甚至被预测在2021年到来。图1.22展示了来自国际半导体技术路线图(ITRS)两版报告的逻辑晶体管物理栅极长度预测。与2013年报告预测的2028年栅极长度达到5纳米不同,2015年报告预测栅极长度在2021年停留在10纳米。之后的密度提升将不得不通过其他方式实现,而不是通过缩小晶体管的尺寸。虽然ITRS的预测有些悲观,但像英特尔和台积电这样的公司计划将栅极长度缩小到3纳米,但变化的速度在减缓。

图1.22 展示了来自ITRS报告两个版本的逻辑晶体管尺寸预测。这些报告始于2001年,但2015年将是最后一个版本,因为该小组因兴趣减退而解散。目前只有GlobalFoundries、Intel、Samsung和TSMC能够生产最先进的逻辑芯片,而在首份ITRS报告发布时,有19家公司参与。只剩下四家公司,计划的共享变得难以维持。摘自IEEE Spectrum,2016年7月,Rachel Courtland撰文《晶体管将于2021年停止缩小,摩尔定律路线图预测》。

图1.23显示了微处理器和DRAM在带宽增加上的变化,这些变化受到Dennard缩放和摩尔定律终结的影响,以及磁盘的变化。技术改进的减缓在逐渐下降的曲线中显而易见。持续的网络改进归功于光纤技术的进步和计划中的脉冲振幅调制(PAM-4)变化,该技术允许双位编码,从而实现以400 Gbit/s的速度传输信息。

谬误:多处理器是一种灵丹妙药。

在2005年左右转向每芯片多个处理器并不是因为出现了某种突破,能够显著简化并行编程或使多核计算机更易于构建。这一变化发生是因为由于ILP壁垒和功耗壁垒,没有其他选择。每芯片多个处理器并不保证降低功耗;确实有可能设计出功耗更高的多核芯片。其潜力在于可以通过用几个低时钟频率、高效率的核心替换一个高时钟频率、低效率的核心,从而继续提高性能。随着缩小晶体管技术的进步,可以略微缩小电容和供电电压,从而在每一代中获得适度的核心数增加。例如,近年来,Intel在其高端芯片中每代增加两个核心。

正如我们在第4章和第5章中将看到的,性能现在成为了程序员的负担。程序员们依赖硬件设计师使他们的程序在不费吹灰之力的情况下更快的时代正式结束了。如果程序员希望他们的程序在每一代中变得更快,他们必须使程序更具并行性。

摩尔定律的流行版本——每一代技术的性能提升——现在取决于程序员。

陷阱:陷入阿姆达尔定律的悲剧性误区。

几乎每位计算机架构师都知道阿姆达尔定律。尽管如此,我们几乎总是偶尔在测量某个特性使用情况之前,就投入大量精力进行优化。只有当整体加速效果令人失望时,我们才会意识到我们应该先进行测量,再投入这么多精力来提升它!

陷阱:单点故障。

使用阿姆达尔定律计算的可靠性提升(见第53页)表明,可靠性并不比链条中最弱的环节更强。无论我们如何提高电源的可靠性,就像我们在示例中所做的那样,单个风扇仍然会限制磁盘子系统的可靠性。这一阿姆达尔定律的观察促成了容错系统的一个经验法则:确保每个组件都是冗余的,以防单个组件的故障导致整个系统崩溃。第6章展示了如何通过软件层在WSCs(大规模数据中心)内部避免单点故障。

谬误:提高性能的硬件增强也会改善能源效率,或者在最坏的情况下,能源效率保持中性。

Esmaeilzadeh等人(2011年)测量了在2.67 GHz的Intel Core i7上,仅使用一个核心的SPEC2006(见第1.5节)。当时钟频率增加到2.94 GHz(即提高了1.10倍)时,性能提高了1.07倍,但i7所需的能量却增加了1.37倍的焦耳和1.47倍的瓦时!

谬误:基准测试的有效性是无限的。

影响基准测试作为实际性能预测工具的因素有很多,其中一些会随时间变化。一个重要因素是基准测试抵抗“基准测试工程”或“基准测试营销”的能力。一旦基准测试成为标准化和流行的工具,就会有巨大的压力通过有针对性的优化或对基准测试规则的激进解释来提升性能。短小的内核或程序,特别是那些在少量代码中运行的程序,尤其容易受到影响。

例如,尽管出于良好意图,最初的SPEC89基准套件包括一个小内核,叫做matrix300,它包含了八个不同的300x300矩阵乘法。在这个内核中,99%的执行时间集中在一行代码上(见SPEC,1989)。当IBM编译器优化了这个内循环(使用了一种叫做分块的好方法,在第2章和第4章讨论),性能提高了9倍!这个基准测试测试了编译器的调优,当然并不是整体性能的良好指示,也不是这种特定优化的典型价值。

图1.19显示,如果忽视历史,我们可能会被迫重复历史。SPEC Cint2006已经十年未更新,给编译器开发者大量时间来优化他们的优化器。注意,除了libquantum之外,所有基准测试在AMD计算机上的SPEC比率都在16-52范围内,在Intel上从22到78。Libquantum在AMD上运行快约250倍,在Intel上快7300倍!这种“奇迹”是Intel编译器的优化结果,该编译器自动将代码并行化到22个核心,并通过使用位打包来优化内存,这种方法将多个狭窄范围的整数打包在一起,从而节省内存空间,减少内存带宽。如果我们去掉这个基准测试并重新计算几何平均值,AMD的SPEC Cint2006从31.9降到26.5,Intel从63.7降到41.4。Intel计算机现在大约是AMD计算机的1.5倍,而不是包含libquantum时的2.0倍,这更接近它们的真实相对性能。SPECCPU2017去掉了libquantum。

为了说明基准测试的短暂寿命,图1.17列出了所有82个SPEC版本的基准测试状态;Gcc是SPEC89中的唯一幸存者。令人惊讶的是,大约70%的SPEC2000或更早版本的所有程序在下一个版本中被淘汰。

谬误:磁盘的额定平均故障时间(MTTF)为1,200,000小时,或将近140年,因此磁盘几乎不会失败。

磁盘制造商的当前营销实践可能会误导用户。MTTF是如何计算的?在早期,制造商会将数千个磁盘放在一个房间里,运行几个月,然后统计失败的数量。他们将MTTF计算为磁盘总共工作小时数除以失败的数量。

一个问题是,这个数字远远超过磁盘的实际寿命,通常假设磁盘的使用寿命为五年或43,800小时。为了让这个大的MTTF有意义,磁盘制造商辩称,这个模型对应于用户购买磁盘后每五年更换一次磁盘——即磁盘的计划使用寿命。声称如果很多客户(及其曾孙)在下一个世纪这样做,平均每个磁盘在故障前会被更换27次,或大约140年。

一个更有用的度量是失败的磁盘百分比,称为年失败率。假设有1000个磁盘,MTTF为1,000,000小时,并且这些磁盘每天24小时使用。如果你用具有相同可靠性特征的新磁盘替换失败的磁盘,那么在一年(8,760小时)内会失败的磁盘数量是

此外,这些高数字是在假设温度和振动范围有限的情况下引用的;如果超出这些范围,那么结果就不再可靠。对实际环境中磁盘驱动器的调查(Gray和van Ingen,2005年)发现,每年有3%到7%的驱动器发生故障,对应的MTTF约为125,000到300,000小时。另一项更大规模的研究发现,年磁盘故障率为2%到10%(Pinheiro等,2007年)。因此,实际环境中的MTTF大约比制造商提供的MTTF差2到10倍。

谬误:峰值性能跟踪观察到的性能。

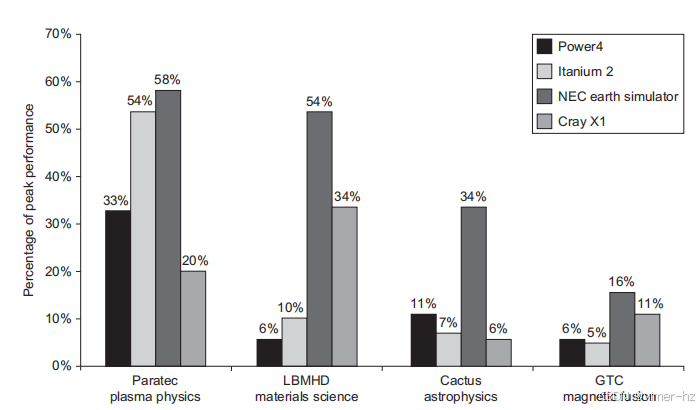

峰值性能唯一普遍正确的定义是“计算机保证不会超过的性能水平。” 图1.24显示了四个程序在四个多处理器上的峰值性能百分比,范围从5%到58%。由于差距如此之

大,并且可能因基准测试而显著变化,峰值性能通常无法有效预测观察到的性能。

图1.24 显示了四个程序在四个多处理器系统上,相对于64个处理器的峰值性能百分比。地球模拟器和X1是向量处理器(参见第4章和附录G)。它们不仅提供了更高的峰值性能百分比,还具有最高的峰值性能和最低的时钟频率。除了Paratec程序外,Power 4和Itanium 2系统的性能介于峰值的5%到10%之间。数据来源:Oliker, L., Canning, A., Carter, J., Shalf, J., Ethier, S., 2004. 现代并行向量系统上的科学计算. 见:ACM/IEEE超级计算会议论文集,2004年11月6-12日,匹兹堡,宾夕法尼亚州,第10页。

陷阱

故障检测可能会降低系统的可用性。这种看似讽刺的陷阱是因为计算机硬件有相当一部分状态可能并非始终对正确操作至关重要。例如,分支预测器发生错误并不是致命的,因为只会影响性能。

在那些积极利用指令级并行(ILP)的处理器中,并非所有操作都是程序正确执行所必需的。Mukherjee 等(2003年)发现,SPEC2000基准测试中,少于30%的操作可能在关键路径上。

程序也是如此。如果程序中的一个寄存器是“死”的——即程序在再次读取之前会写入该寄存器——那么错误并不重要。如果在检测到死寄存器中的瞬态故障时让程序崩溃,这会不必要地降低可用性。

Oracle的Sun Microsystems部门在2000年经历了这一陷阱,他们在Sun E3000到Sun E10000系统的L2缓存中包括了奇偶校验,但没有错误纠正。用于构建缓存的SRAM存在间歇性故障,这些故障被奇偶校验检测出来。如果缓存中的数据没有被修改,处理器会简单地从缓存中重新读取数据。由于设计师没有使用ECC(错误更正码)保护缓存,操作系统只能报告数据损坏错误并崩溃程序。现场工程师在超过90%的情况下检查没有发现问题。

为了减少这种错误的频率,Sun修改了Solaris操作系统,通过一个进程主动将脏数据写入内存来“清理”缓存。由于处理器芯片没有足够的引脚添加ECC,唯一的硬件选项是复制外部缓存,使用没有奇偶错误的副本来纠正错误。

这个陷阱在于检测故障而没有提供纠正机制。这些工程师不太可能设计另一个没有ECC的外部缓存计算机。

1.12 Concluding Remarks

本章介绍了一些概念,并提供了一个定量框架,我们将在整本书中扩展这个框架。从上一版开始,能源效率成为了性能的永恒伴侣。

在第2章中,我们从内存系统设计这一至关重要的领域开始。我们将研究一系列技术,这些技术共同作用,使内存看起来几乎无限大,同时尽可能快。(附录B为那些对缓存不太了解的读者提供了基础材料。)与后续章节一样,我们将看到硬件和软件的合作已成为高性能内存系统的关键,就像它对高性能流水线系统的重要性一样。本章还涵盖了虚拟机,这是一种越来越重要的保护技术。

在第3章中,我们探讨了指令级并行(ILP),其中流水线是最简单和最常见的形式。利用ILP是构建高速单处理器的最重要技术之一。第3章开始于对基本概念的广泛讨论,这将为你准备后续章节中讨论的各种思想。第3章的例子涵盖了大约40年,涉及从最早的超级计算机(IBM 360/91)到2017年市场上最快的处理器。它强调了动态或运行时的ILP利用方法。它还讨论了ILP思想的限制,并介绍了多线程,这在第4章和第5章中有进一步的发展。附录C为那些对流水线不太了解的读者提供了基础材料。(我们期望它对许多读者,包括我们介绍性文本《计算机组织与设计:硬件/软件接口》的读者来说是一个复习。)

第4章解释了利用数据级并行的三种方法。最经典且最古老的方法是向量架构,我们从这里开始,阐明SIMD设计的原则。(附录G对向量架构进行了更深入的探讨。)接下来,我们解释了今天大多数桌面微处理器中发现的SIMD指令集扩展。第三部分是对现代图形处理单元(GPU)工作原理的深入解释。大多数GPU描述都是从程序员的角度编写的,这通常掩盖了计算机的真实工作方式。本节从内部人员的角度解释了GPU,包括GPU术语与传统架构术语之间的映射。

第5章重点讨论了通过使用多个处理器或多处理器系统来实现更高性能的问题。与通过并行性重叠单独指令不同,多处理器利用并行性允许多个指令流在不同处理器上同时执行。我们主要关注共享内存多处理器这一主要形式,同时也介绍了其他类型,并讨论了任何多处理器系统中出现的广泛问题。我们将探讨各种技术,重点是1980年代和1990年代首次提出的重要思想。

第6章介绍了集群,并深入探讨了计算机架构师参与设计的WSC(Web服务器集群)。WSC的设计者是超级计算机先驱(如Seymour Cray)的专业后代,他们设计的是极端计算机。WSC包含数万台服务器,其设备和建筑的总成本接近2亿美元。前几章中价格性能和能源效率的关注点也适用于WSC,并且使用量化方法做决策。

第7章是本版新增的内容。它介绍了领域特定架构作为在摩尔定律和Dennard缩放结束后的性能和能源效率提升的唯一途径。它提供了如何构建有效的领域特定架构的指导,介绍了深度神经网络这一令人兴奋的领域,描述了四个采用不同方法加速神经网络的最新例子,并比较了它们的成本效益。

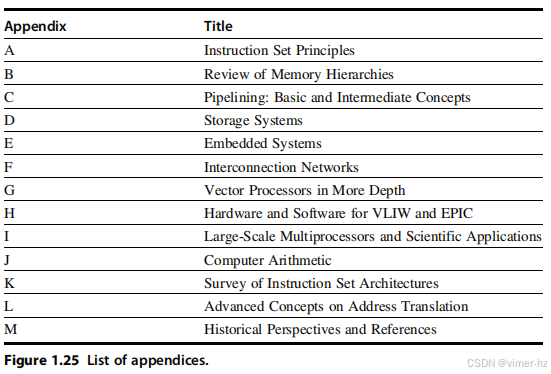

本书附带了大量在线资料(详见前言),以减少成本并向读者介绍各种先进主题。图1.25展示了所有这些内容。书中的附录A–C将为许多读者提供复习。

在附录D中,我们将重点从处理器中心的视角转向存储系统,并讨论存储系统中的问题。我们采用类似的定量方法,但基于系统行为的观察,使用端到端的性能分析方法。该附录主要解决如何使用低成本的磁性存储技术高效地存储和检索数据的问题。我们专注于检查磁盘存储系统在典型的I/O密集型工作负载(如本章提到的OLTP基准测试)中的性能。我们详细探讨了基于RAID的高级主题,这些系统使用冗余磁盘来实现高性能和高可用性。最后,附录D介绍了排队理论,为权衡利用率和延迟提供了基础。

附录E从嵌入式计算的角度应用了各章和早期附录中的理念。

附录F广泛探讨了系统互连的话题,包括允许计算机通信的广域网和系统区域网。

附录H回顾了VLIW(非常长指令字)硬件和软件,这些在EPIC(扩展指令集计算)出现时的流行程度较低。

附录I描述了用于高性能计算的大规模多处理器系统。

附录J是从第一版中保留下来的唯一附录,涵盖了计算机算术。

附录K提供了指令架构的概述,包括80x86、IBM 360、VAX及许多RISC架构,如ARM、MIPS、Power、RISC-V和SPARC。

附录L是新增的,讨论了内存管理的高级技术,重点支持虚拟机和设计用于非常大地址空间的地址转换。随着云处理器的发展,这些架构增强变得越来越重要。

接下来,我们将描述附录M。

1.13 Historical Perspectives and References

附录M(在线提供)包括了对本书各章中关键思想的历史视角。这些历史视角部分允许我们追踪一个思想通过一系列机器的发展,或描述重要的项目。如果你对某个思想或处理器的初期发展感兴趣,或者想要进一步阅读,参考文献在每段历史末尾提供。有关数字计算机和性能测量方法初期发展的讨论,请参阅本章的M.2节“计算机的早期发展”。

在阅读这些历史材料时,你会很快意识到,与许多其他工程领域相比,计算机领域的一个重要好处是一些先驱者仍然在世——我们可以通过直接询问他们来学习历史!

案例研究和练习 由 Diana Franklin 编写

### 案例研究 1: 芯片制造成本

#### 本案例研究所展示的概念

- 制造成本

- 制造良率

- 通过冗余的缺陷容忍

计算机芯片的价格涉及许多因素。英特尔正在花费70亿美元来完成其 Fab 42 制造设施,以实现 7 纳米技术。在本案例研究中,我们探讨一个假设的公司面临的类似情况,以及涉及制造技术、面积和冗余的不同设计决策如何影响芯片的成本。

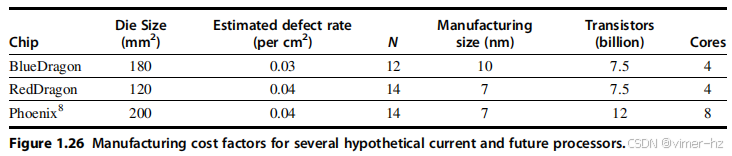

1.1 [10/10] <1.6> 图 1.26 给出了影响多个当前芯片成本的假设相关芯片统计数据。在接下来的几个练习中,你将探讨不同设计决策对英特尔芯片的影响。

a. [10] <1.6> Phoenix 芯片的良率是多少?

b. [10] <1.6> 为什么 Phoenix 的缺陷率比 BlueDragon 高?

#### 1.2 [20/20/20/20] <1.6>

他们将从那个工厂销售一系列芯片,需要决定将多少产能分配给每种芯片。假设他们将销售两种芯片。Phoenix 是一种完全新的架构,设计时考虑了 7 纳米技术,而 RedDragon 则与他们的 10 纳米 BlueDragon 具有相同的架构。假设 RedDragon 每个无缺陷芯片的利润为 15 美元,而 Phoenix 每个无缺陷芯片的利润为 30 美元。每片晶圆的直径为 450 毫米。

a. [20] <1.6> 每片 Phoenix 芯片的利润是多少?

b. [20] <1.6> 每片 RedDragon 芯片的利润是多少?

c. [20] <1.6> 如果你的需求是每月 50,000 个 RedDragon 芯片和每月 25,000 个 Phoenix 芯片,而你的工厂每月可以制造 70 片晶圆,你应该生产多少片每种芯片的晶圆?

#### 1.3 [20/20] <1.6>

你在 AMD 的同事建议,由于良率很低,你可能通过推出多个版本的相同芯片(只是核心数量不同)来降低芯片生产成本。例如,你可以销售 Phoenix8、Phoenix4、Phoenix2 和 Phoenix1,它们分别包含 8、4、2 和 1 个核心。如果所有八个核心都是无缺陷的,那么它将作为 Phoenix8 销售。具有四到七个无缺陷核心的芯片将作为 Phoenix4 销售,具有两个或三个无缺陷核心的芯片将作为 Phoenix2 销售。为了简化计算,将单个核心的良率视为与原始 Phoenix 芯片面积为 1/8 的芯片的良率相同。然后将该良率视为单个核心无缺陷的独立概率。计算每种配置的良率,即对应数量核心无缺陷的概率。

a. [20] <1.6> 单个核心无缺陷的良率是多少?Phoenix4、Phoenix2 和 Phoenix1 的良率是多少?

b. [5] <1.6> 根据第 a 部分的结果,确定哪些芯片值得打包和销售,以及原因。

c. [10] <1.6> 如果生产 Phoenix8 芯片的成本之前是 20 美元,那么新 Phoenix 芯片的成本是多少,假设没有与从垃圾中救回芯片相关的额外成本?

d. [20] <1.6> 你目前每个无缺陷的 Phoenix8 芯片的利润为 30 美元,每个 Phoenix4 芯片的售价为 25 美元。如果考虑到 (i) Phoenix4 芯片的购买价格完全作为利润,以及 (ii) 将 Phoenix4 芯片的利润按生产比例分配到每个 Phoenix8 芯片中,你每个 Phoenix8 芯片的利润是多少?请使用第 1.3a 部分计算的良率,而不是第 1.1a 部分的结果。

### 案例研究 2: 计算机系统中的功耗

#### 相关概念

- 阿姆达尔定律(Amdahl’s Law)

- 冗余(Redundancy)

- 平均故障前时间(MTTF)

- 功耗(Power Consumption)

现代系统的功耗受多种因素影响,包括芯片时钟频率、效率和电压。以下练习探讨了不同设计决策和使用场景对功耗和能量的影响。

#### 1.4 [10/10/10/10] <1.5>

手机执行非常不同的任务,包括音乐流媒体、视频流媒体和阅读电子邮件。这些任务涉及非常不同的计算操作。电池寿命和过热是手机常见的问题,因此减少功耗和能量消耗至关重要。在这个问题中,我们考虑当用户没有充分使用手机计算能力时应该怎么办。我们将评估一个不切实际的场景,其中手机没有专用处理单元。相反,它有一个四核的通用处理单元。每个核心在满负荷时使用0.5瓦特。在处理电子邮件任务时,这个四核的速度是必要速度的1/8。

a. [10] <1.5> 与满功率运行相比,需要多少动态能量和功率?首先,假设四核在1/8的时间内运行,其他时间处于空闲状态。也就是说,时钟在7/8的时间内被禁用,在这段时间内没有漏电。比较总动态能量和动态功率。

b. [10] <1.5> 使用频率和电压缩放需要多少动态能量和功率?假设频率和电压都降低到原来的1/8。

c. [10] <1.6, 1.9> 现在假设电压不能低于原始电压的50%。这个电压被称为电压下限,低于这个电压将丢失状态。因此,虽然频率可以继续降低,但电压不能。此情况下的动态能量和功率节省是多少?

d. [10] <1.5> 使用“暗硅”(dark silicon)方法的能量消耗是多少?这涉及为每个主要任务创建专用的ASIC硬件,并在不使用时对这些元素进行功率门控。只提供一个通用核心,芯片的其余部分将填充专用单元。对于电子邮件,这一个核心将运行25%的时间,并在其他75%的时间内完全关闭。其余75%的时间,将运行一个需要核心能量20%的专用ASIC单元。

1.5 [10/10/10] <1.5> 如练习1.4中所述,手机运行各种不同的应用程序。在本练习中,我们将做出与上一个练习相同的假设,即每个核心功耗为0.5瓦特,并且四核在处理电子邮件时的速度是单核的3倍。

a. [10] <1.5> 假设80%的代码是可并行化的。为了使单核在与四核并行代码相同的速度下运行,单核的频率和电压需要增加多少?

b. [10] <1.5> 使用频率和电压缩放在部分a中带来了多少动态能量的减少?

c. [10] <1.5> 使用“暗硅”(dark silicon)方法时消耗了多少能量?在这种方法中,所有硬件单元都被断电,以使它们完全关闭(不会产生泄漏)。提供的专用ASIC的功耗是通用处理器的20%。假设每个核心都被断电。视频游戏需要两个ASIC和两个核心。与在四核上并行处理的基线相比,这种方法需要多少动态能量?

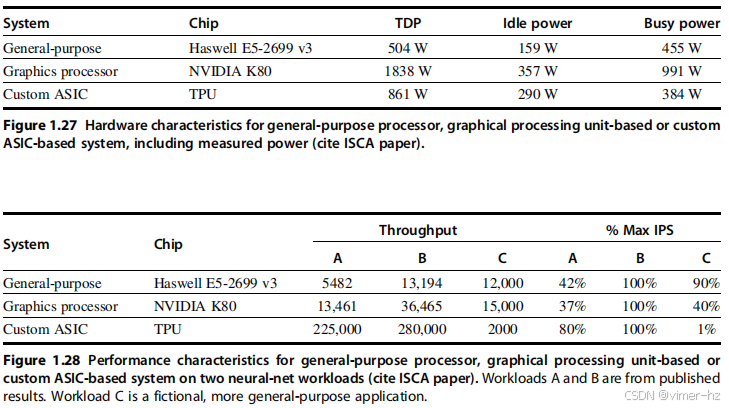

1.6 [10/10/10/10/10/20] <1.5,1.9> 通用处理器经过优化以适应广泛的计算需求,即它们针对大量应用程序中普遍存在的行为进行了优化。然而,一旦将领域有所限制,目标应用程序中大多数行为可能与通用应用程序不同。深度学习或神经网络就是一个例子。尽管深度学习可以应用于许多不同的应用程序,但推断的基本构建块——使用学习到的信息做决策——在所有应用中都是相同的。推断操作大多是并行的,因此它们目前在图形处理单元(GPU)上执行,GPU更倾向于这种类型的计算,但并不是专门针对推断。为了提高每瓦特的性能,谷歌创造了一种使用张量处理单元(TPU)的定制芯片,以加速深度学习中的推断操作。这个方法可以用于语音识别和图像识别等应用。这个问题探讨了这种处理方式与通用处理器(Haswell E5-2699 v3)和GPU(NVIDIA K80)在性能和冷却方面的权衡。如果计算机中的热量没有有效去除,风扇将把热空气吹回计算机,而不是冷空气。注意:差异不仅在于处理器,芯片内存和DRAM也会影响结果。因此统计数据是系统级别的,而不是芯片级别的。

a. [10] <1.9> 如果谷歌的数据中心在运行GPU时,70%的时间用于负载A,30%的时间用于负载B,那么TPU系统相对于GPU系统的加速比是多少?

b. [10] <1.9> 如果谷歌的数据中心在运行GPU时,70%的时间用于负载A,30%的时间用于负载B,那么每个系统的最大IPS百分比是多少?

c. [15] <1.5, 1.9> 基于(b),假设功率随着IPS从0%增长到100%而线性缩放,那么TPU系统相对于GPU系统的每瓦特性能是多少?

d. [10] <1.9> 如果另一个数据中心将40%的时间用于负载A,10%的时间用于负载B,50%的时间用于负载C,那么GPU和TPU系统相对于通用处理系统的加速比是多少?

e. [10] <1.5> 一个机架冷却门的成本是4000美元,能散发14 kW的热量(进入房间;还需要额外的费用将其排出房间)。根据图1.27和1.28中的TDP,一个冷却门可以冷却多少台Haswell、NVIDIA或Tensor基服务器?

f. [20] <1.5> 典型的服务器机房每平方英尺的最大散热量为200 W。假设一个服务器机架需要11平方英尺(包括前后清理空间),那么一个机架上可以放置多少台第(e)部分中的服务器,并且需要多少个冷却门?

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?