第一步 编译Xilinx的IP核

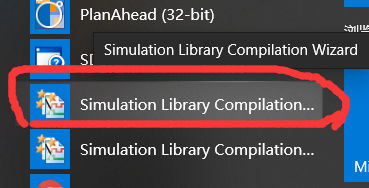

在开始菜单Xilinx文件夹中选择Simulation Library Compilation这个工具:仿真器编译工具,如下图1所示,

图1:

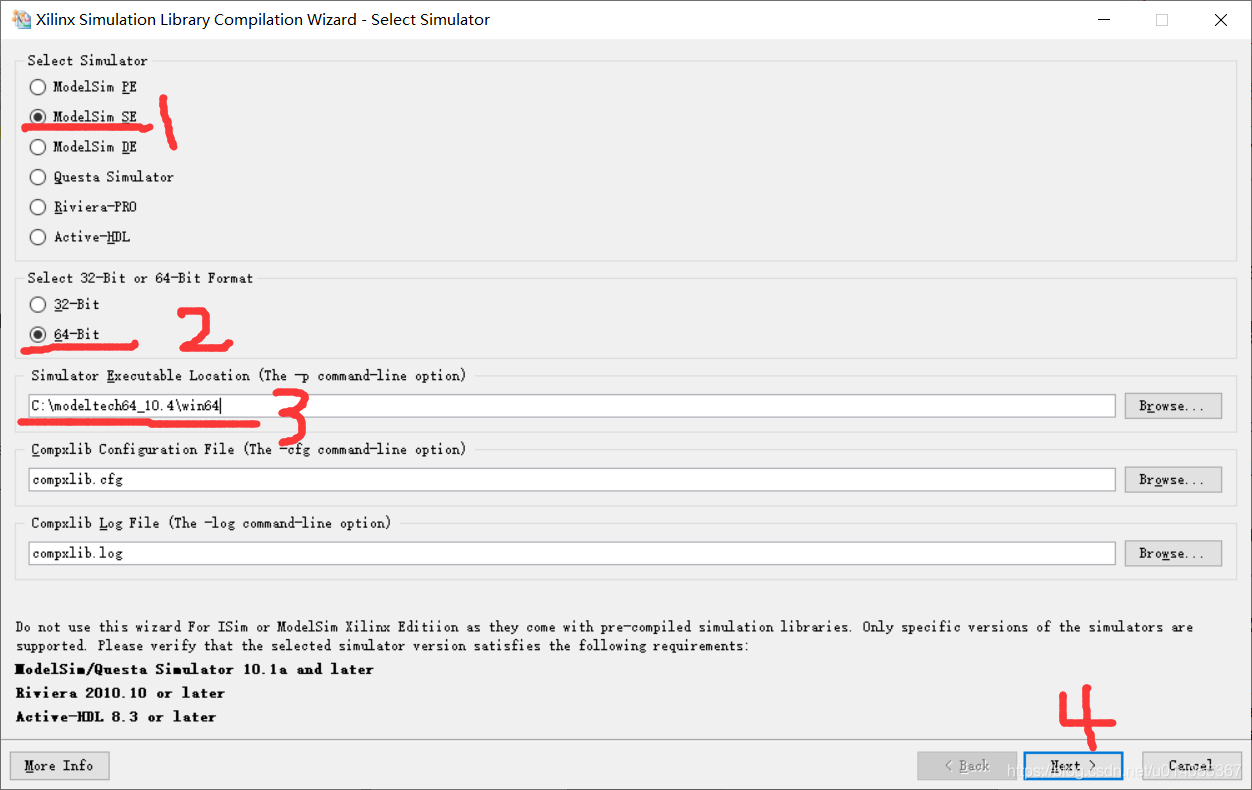

打开仿真器编译工具后,进行如下图2所示的配置,操作步骤按图进行配置

图2:

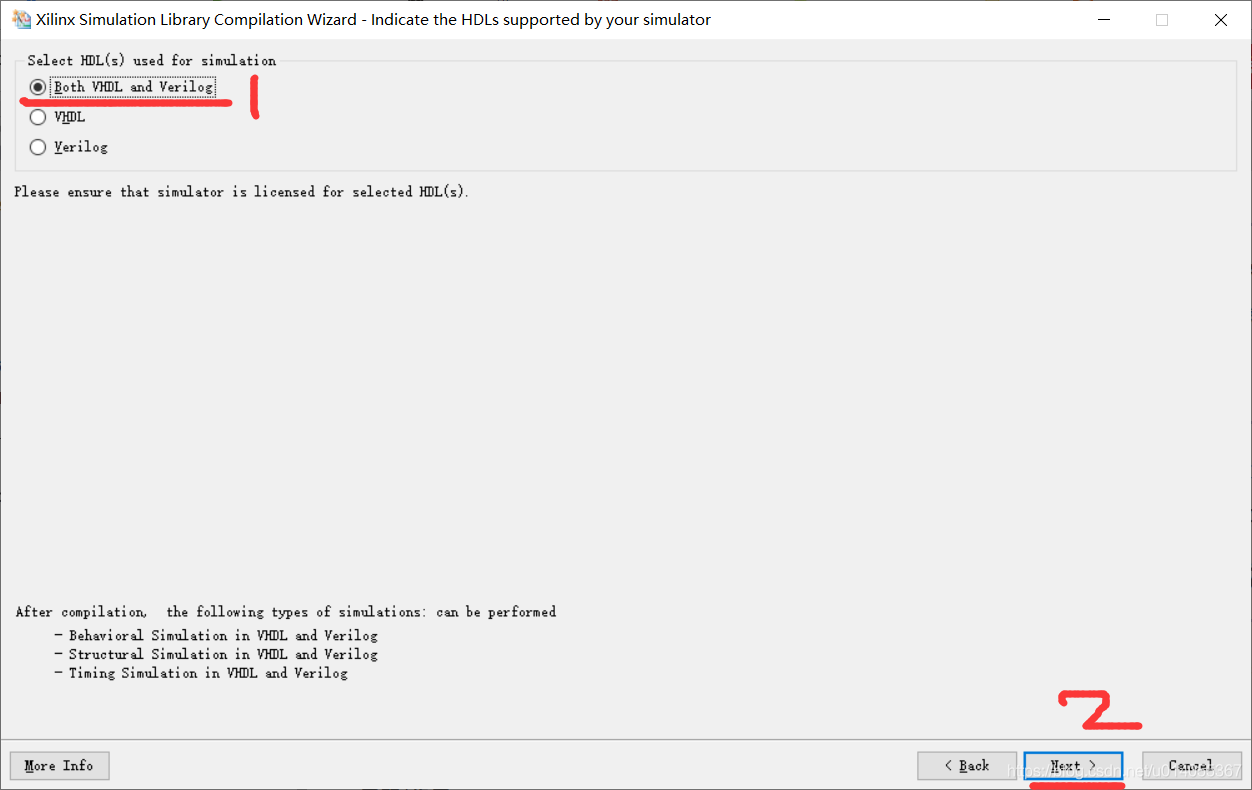

第2步中看自己系统选择,一般都选64位,第3步是modelsim软件的启动路径,然后第4步后,紧接着在下图3中选择第一项:Both VHDL and Verilog,

图3:

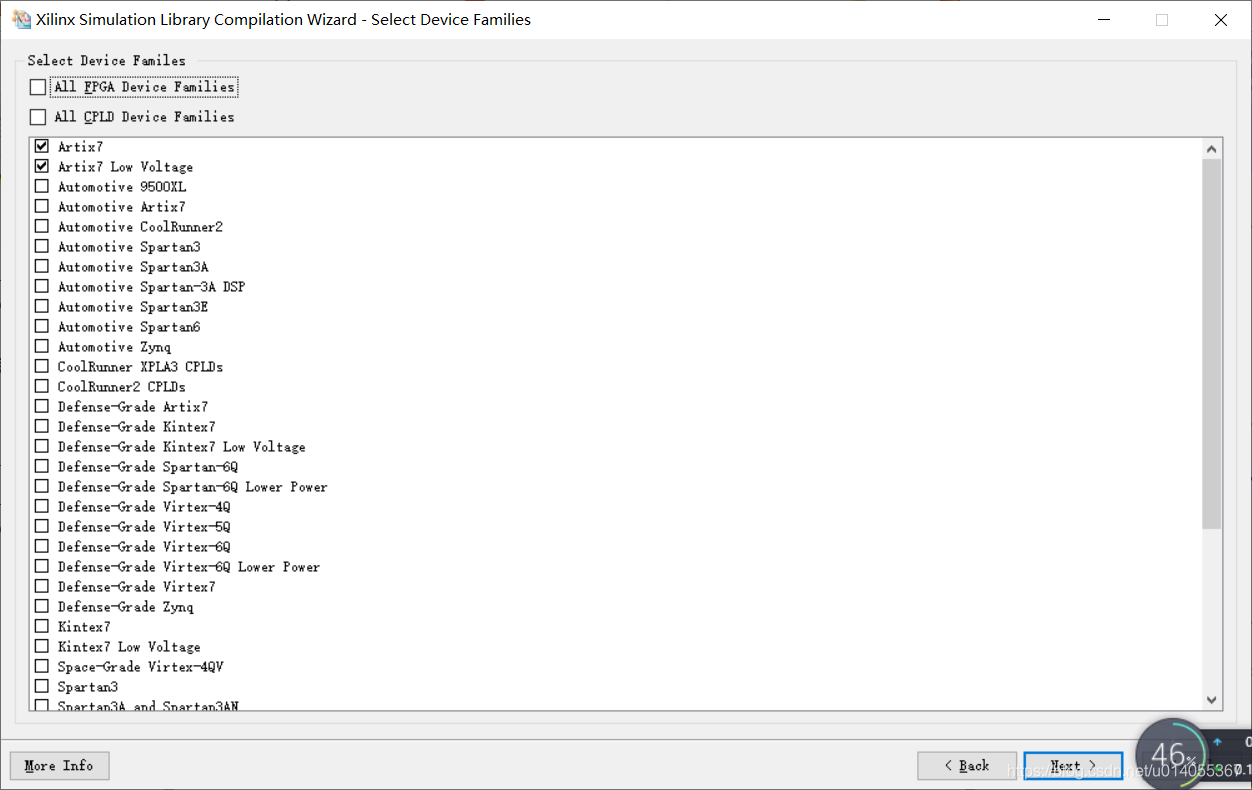

继续Next:这里根据自己具体情况而定,全选的话,编译需要很长时间,我这里需要Artix7和Spartan6,就只选这两个,如下图4所示。

图4:

然后继续Next:

图5:

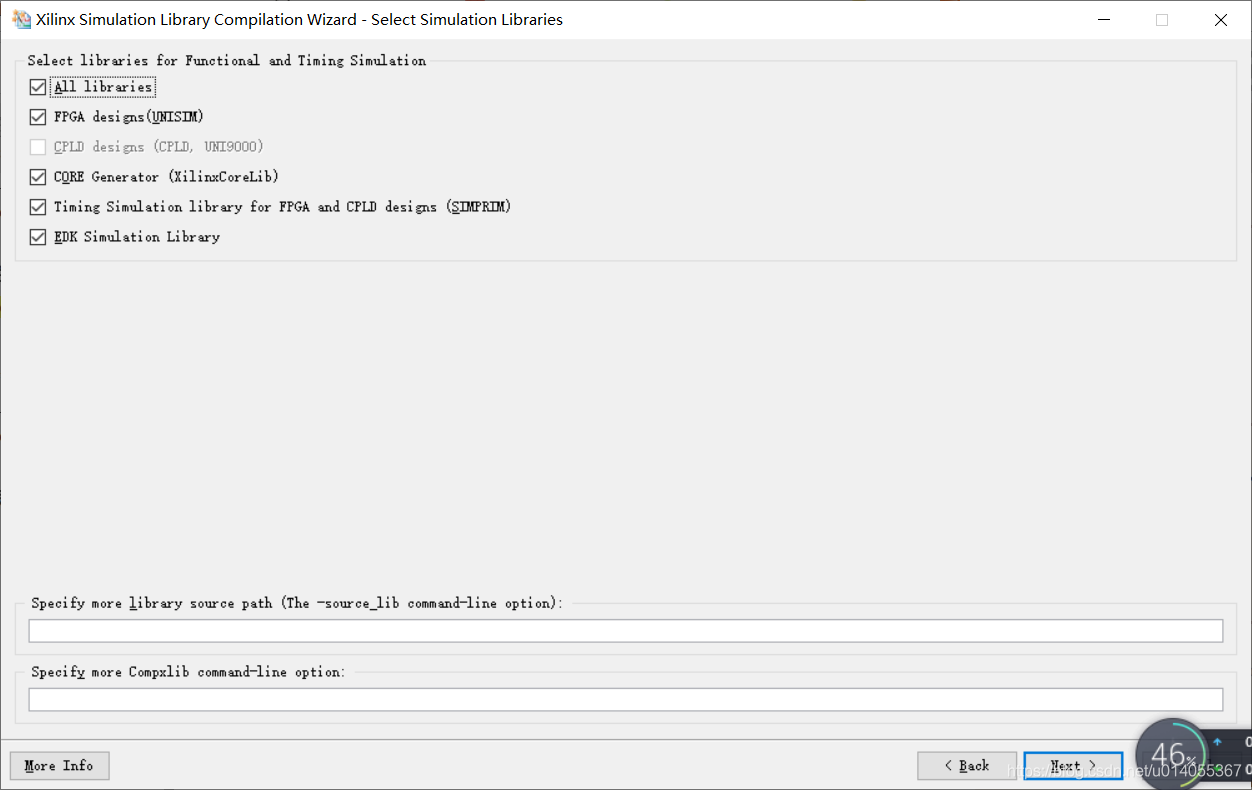

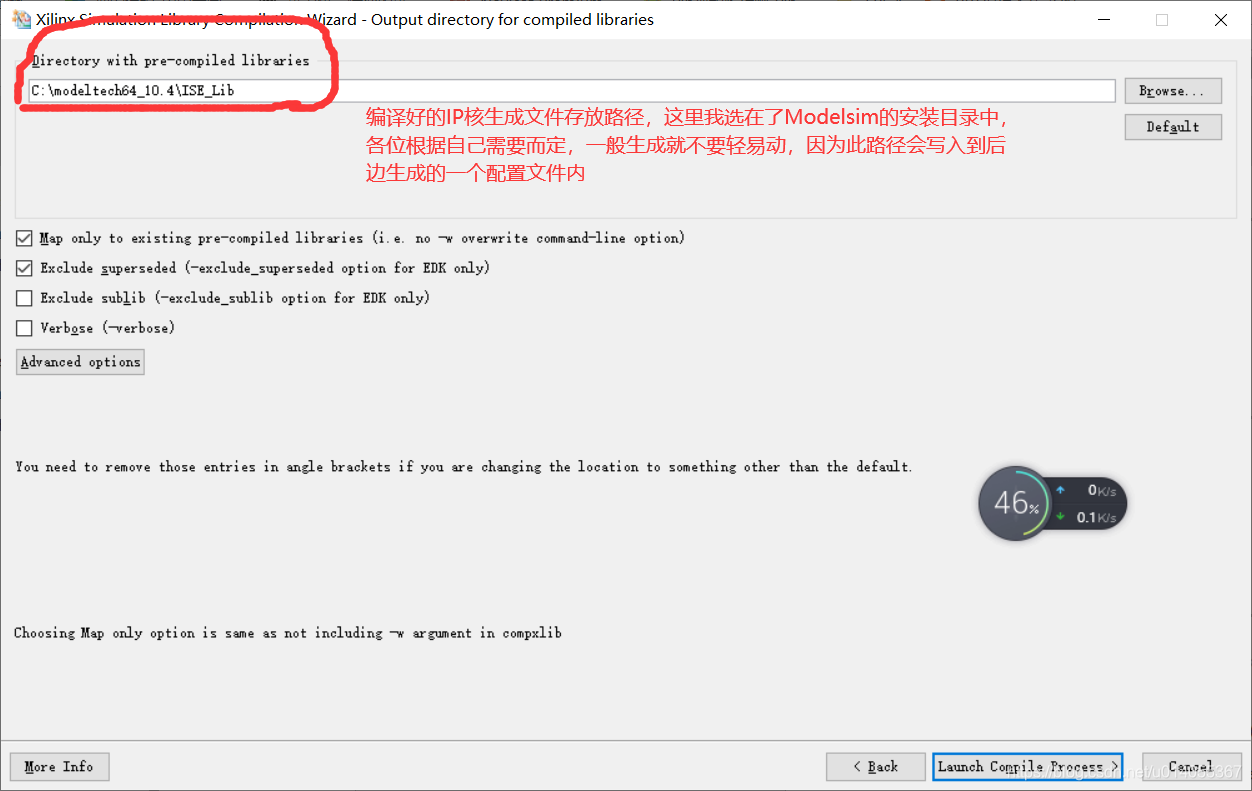

这里默认,继续Next,来到此界面,如图6所示。

图6:

点击Launch Compile Process开始编译,等待大概十几分钟的样子。。。。

十多分钟过去后,会报一些编译错误,不过没关系不影响使用,直接完成即可。编译IP核到此结束。

第二步 更新modelsim配置文件

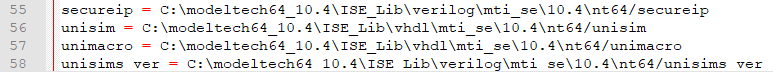

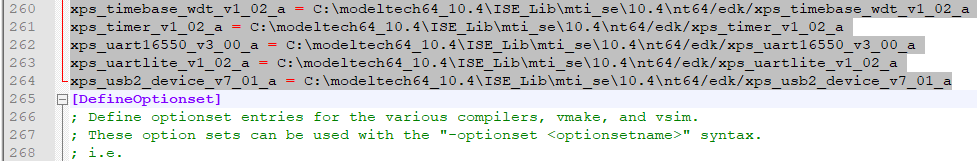

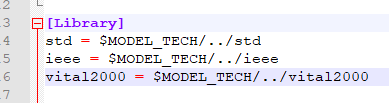

进入到刚才在图6中设置的IP核编译文件路径,找到文件名为modelsim.ini的文件,打开选中如图7所示,从secureip这一行开始,到[DefineOptionset]之前这一段的内容,复制Ctrl+C。

图7:

然后在modelsim安装的根目录录下找到同样文件名的modelsim.ini的文件,右键文件属性去掉只读属性,然后打开它,找到vital2000 = $MODEL_TECH/…/vital2000这一行,在它下面另起一行,将刚才复制的内容粘贴到这里,如图8所示。

图8:

保存并关闭该文件,把modelsim.ini属性文件恢复为只读属性。

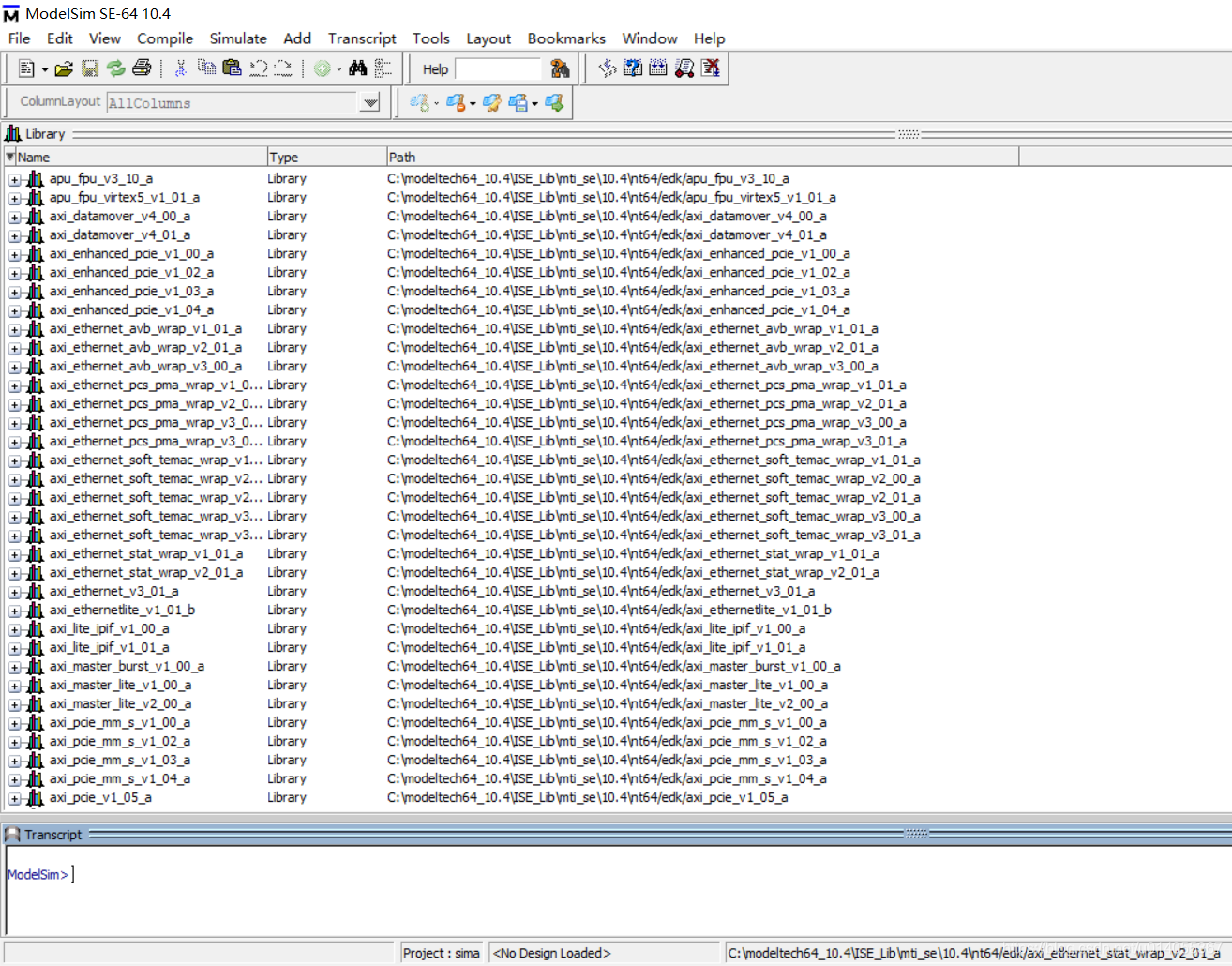

打开modelsim软件,如果如下图9所示的样子,那恭喜你,配置已经成功了。

图9:

到此modelsim的配置完毕了。

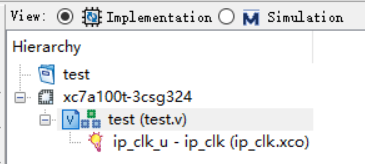

第三步 ISE新建含IP核的工程

这里以我新建的一个利用IP核进行倍频工程为例,芯片A7系列。具体工程创建步骤挺简单就省略了。

我的工程目录结构如图10所示

图10:

顶层文件test.v代码很简单,如下:

module test(

input clk_in,

input rst_n,

output clkout

);

ip_clk ip_clk_u(

.CLK_IN1(clk_in),

.CLK_OUT1(clkout),

.RESET(rst_n)

);

endmodule

仿真文件test_tb.v代码如下:

`timescale 1ns / 1ps

module test_tb;

// Inputs

reg clk_in;

reg rst_n;

// Outputs

wire clkout;

// Instantiate the Unit Under Test (UUT)

test uut (

.clk_in(clk_in),

.rst_n(rst_n),

.clkout(clkout)

);

initial begin

// Initialize Inputs

clk_in = 0;

rst_n = 0;

// Wait 100 ns for global reset to finish

#100;

rst_n = 1;

// Add stimulus here

end

always #20 clk_in=~clk_in;

endmodule

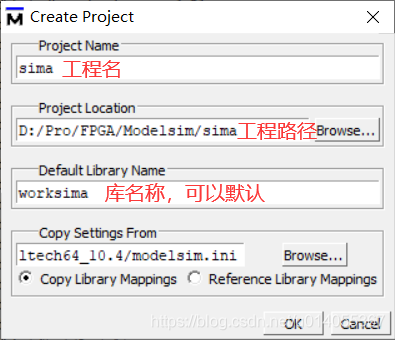

第四步 modelsim新建仿真工程

1、新建工程

打开modelsim,依次选择菜单栏file=>new=>project,新建一个工程,如图11所示,其他默认,点击OK。

图11:

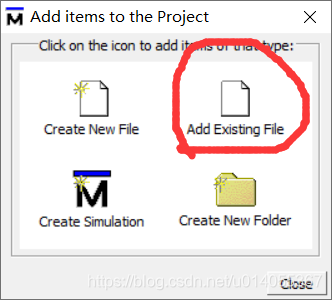

2、添加仿真需要文件

然后选择添加文件

图12:

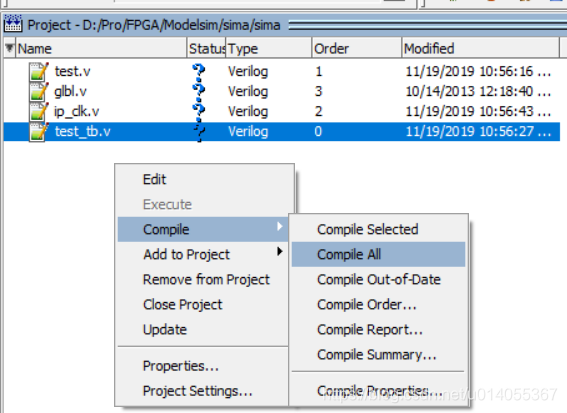

将工程中的顶层文件test.v和IP核生成的文件(路径:当前工程下有个名叫ipcore_dir的文件夹,找到跟生成的IP核名相同的后缀.v的文件)ip_clk.v,以及一个必须添加的文件glbl.v(该文件在编译生成的IP核库文件夹下:…\IP核库\verilog\src下),直接把glbl.v文件拷贝到仿真工程下即可,把它们都添加进来,然后在工程窗口右键,选择Complie All,如图13所示:

图13:

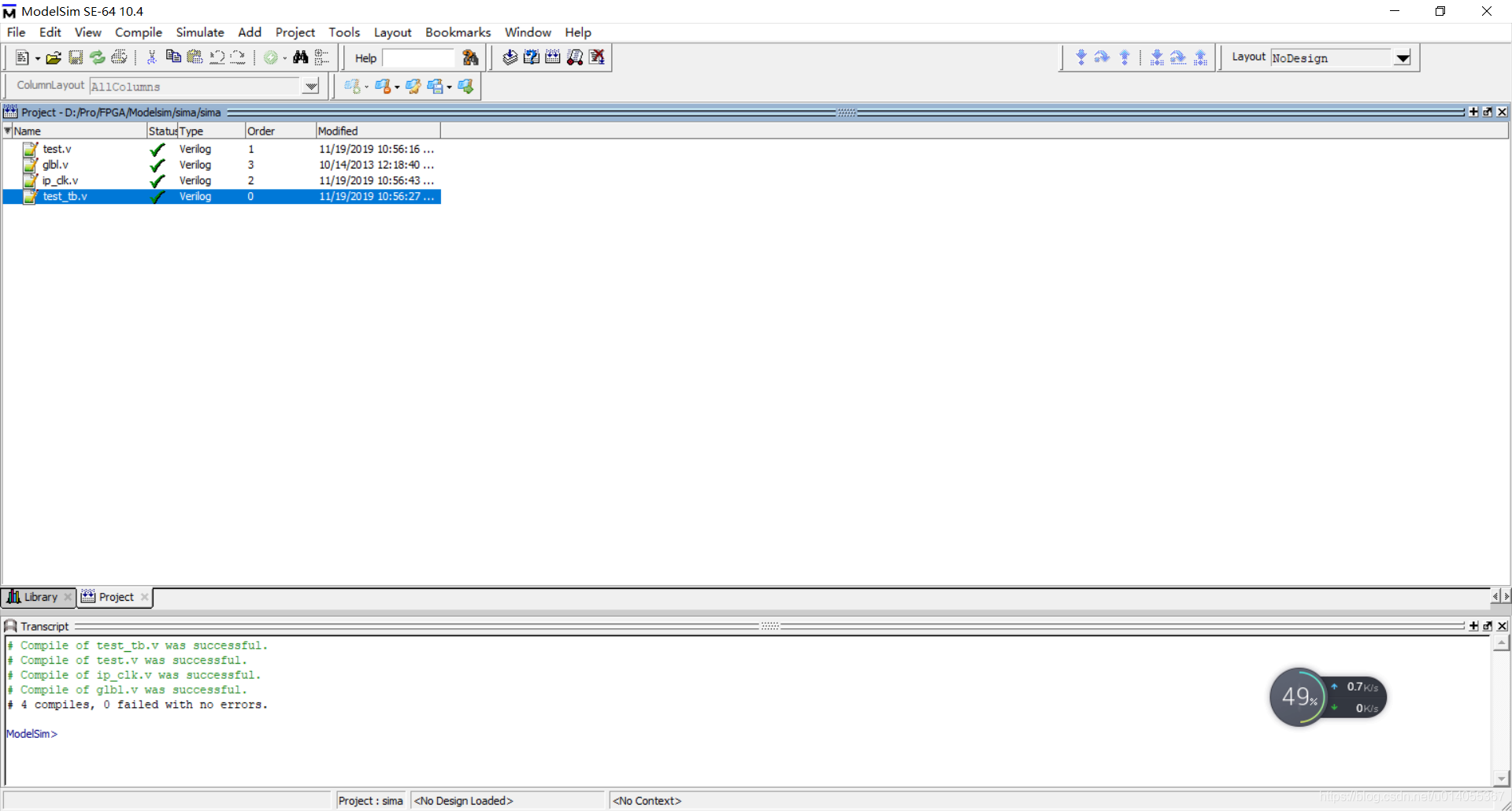

3、编译文件

编译如果没有错,则文件后的问号变为对勾,如图14所示:

图14

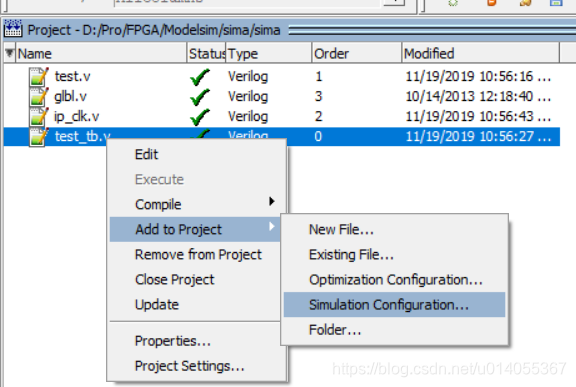

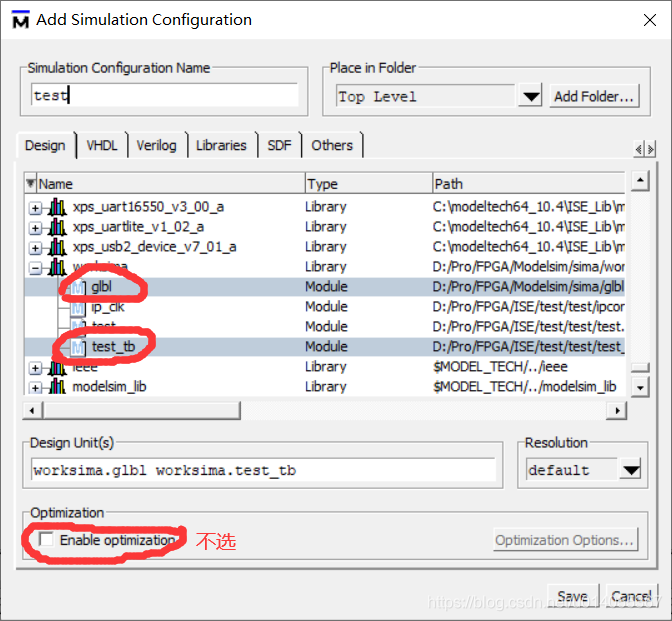

4、添加仿真配置文件

然后在工程窗口右键,选择Add toProject=>Simulation Conofiguration

图15

打开如下图16界面所示,在列表中找到刚才自己命名的worksima的库,打开通过Ctrl+鼠标左键同时选中test_tb和glbl这两个名字,Enable optimization这个也要取消,这样仿真时界面只会显示端口信号,不然一会儿仿真时可能会报错,同时在仿真界面也会把所有内部和外部的信号全都列出来,不容易查找需要观察的信号。

图16

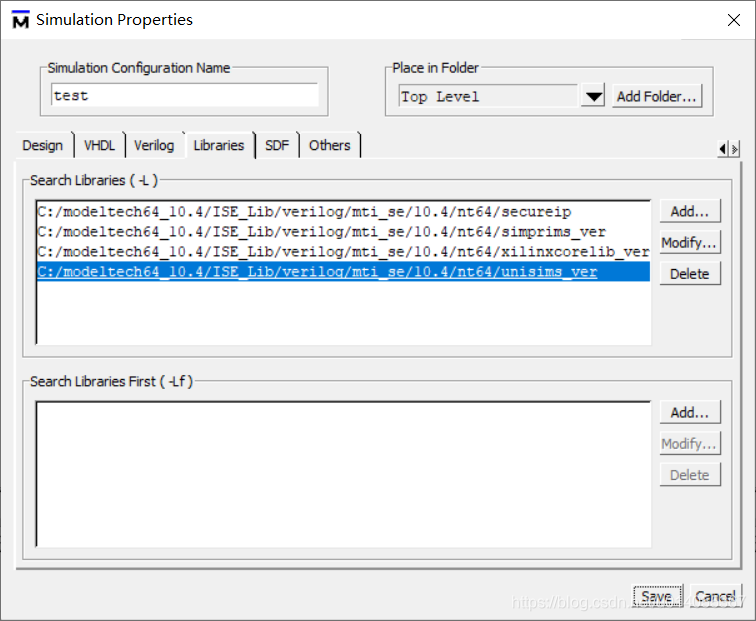

然后切换到Libraries一栏,添加仿真时需要用到的IP库,一般添加如下几个库:

…/IP库/verilog/mti_se/10.4/nt64/secureip

…/IP库/verilog/mti_se/10.4/nt64/simprims_ver

…/IP库/verilog/mti_se/10.4/nt64/xilinxcorelib_ver

…/IP库/verilog/mti_se/10.4/nt64/unisims_ver

我的库路径如图17所示的这几个,一般仿真不会出问题。具体为啥modelsim配置文件IP库路径已经设置好了,为啥这里非得再添加一遍IP核库路径,具体我也不知道,当时我在这费了两三天的功夫,后来添加这几个IP核库路径后才迈过这个坎。。。。。。

图17

到此IP库路径设置完毕,点击save即可。

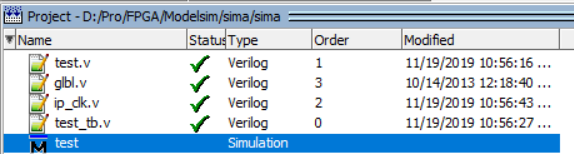

到此仿真工程就建完了。接下来开始仿真了。

第五步 开始仿真

1、运行仿真

回到工程窗口后,双击test这个配置文件,如图18所示,

图18

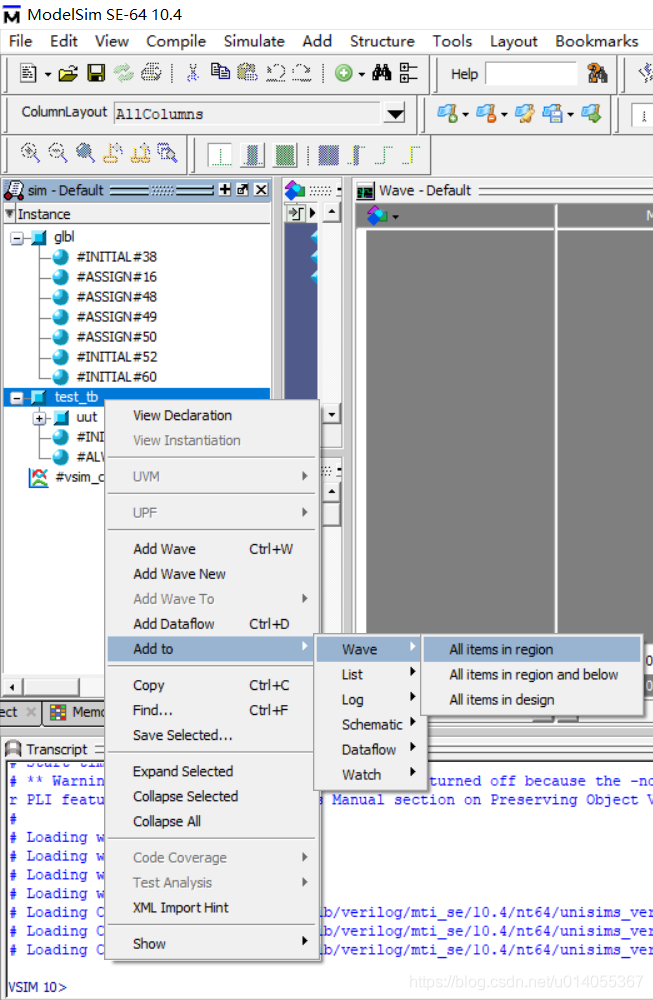

2、添加观察信号

双击test后打开仿真窗口,此时先添加要观察的信号,添加方法如下图19所示:

图19

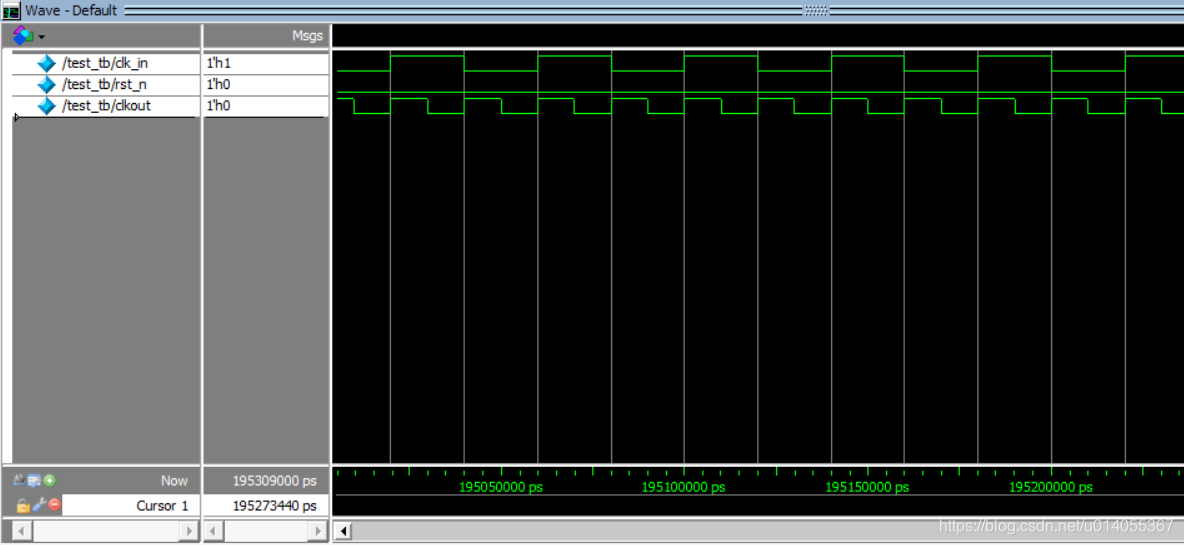

3、查看仿真结果

添加信号后,点击运行仿真,然后观察信号波形,仿真结果如图20所示:

图20

从波形中可以看出,输入时钟clk_in周期是输出时钟clkout周期的两倍,实现了倍频,仿真结果完美。

1544

1544

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?