Modelsim与ISE联合仿真方法

准备

1、下载安装Modelsim-SE10.4

本人使用的仿真软件版本,Win7和Win10都试过了可正常使用

Modelsim-SE10.4安装包下载链接:modelsim_SE下载地址

具体安装步骤安装包里面有,此处略去一万个字。。。。。。

2、配置Modelsim

使用ISE的IP核编译工具编译使用的IP核,使Modelsim支持IP核仿真,具体详见本人其他博客

3、ISE14.7也已准备就绪,下面开始表演

第一步 ISE与Modelsim仿真相关配置

这里假设已经有一个综合无问题的基于Verilog的工程。

1、设置Modelsim软件启动路径

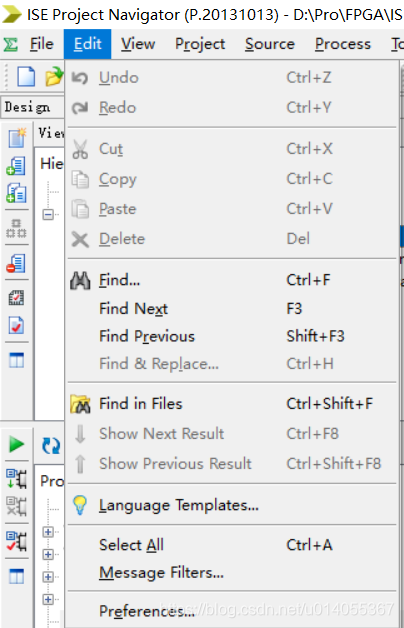

首先打开ISE主菜单栏中的Edit,在列表中选择Preference如下图所示的选项

图1

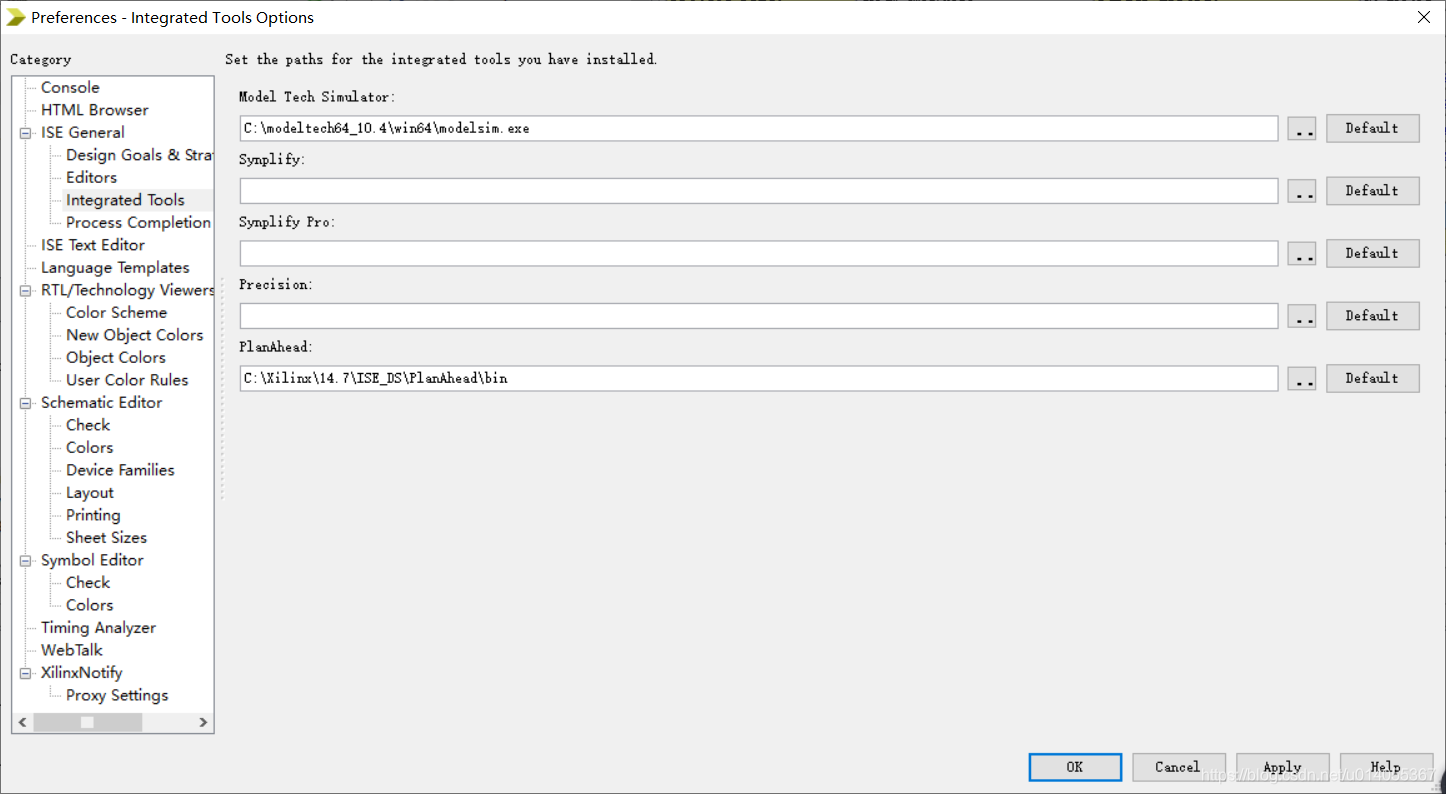

然后打开如下图所示的窗口,

图2

选择ISE Genernal中的Integrated Tools,设置Model Tech Simulator选项,该选项设置的是Modelsim的安装目录,比如我安装在了C盘根目录下,选择OK关闭窗口。

2、更改ISE的仿真工具

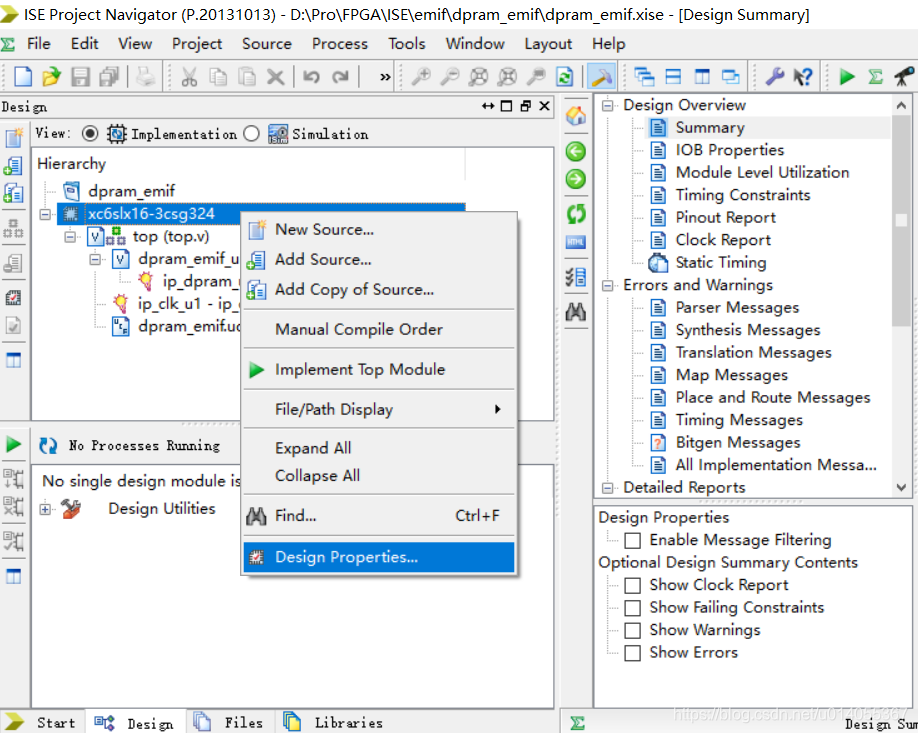

在Design工具窗口中,选中工程中的器件,然后右键选择Design Properties选项,如下图:图3

打开如下图的设置窗口:图4

将Simulator选项由默认的ISim更改为Modelsim-SE Verilog。好了所有设置都已经准备好了

第二步 仿真文件添加

这里以我新建的IP核进行倍频为例

1、新建工程,太简单就略去。。。

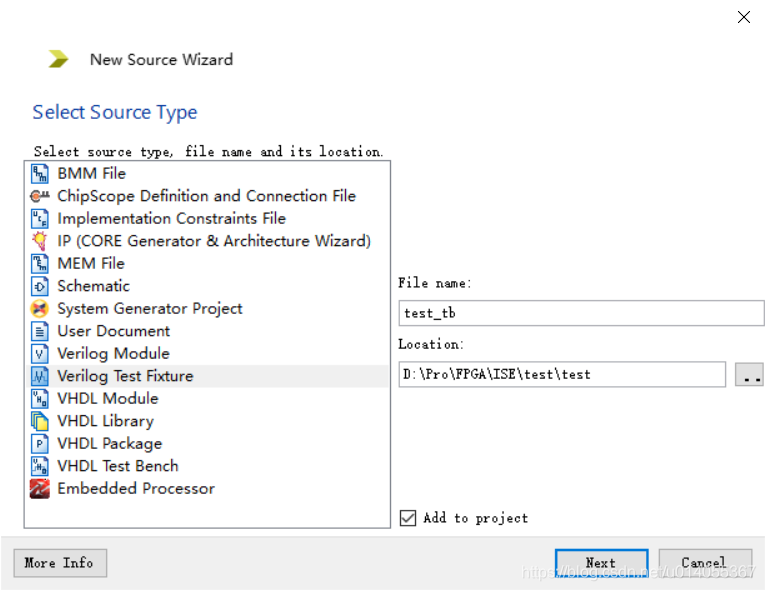

2、然后新添加仿真文件,在工程目录器件上选中,右键,选择New Source,如上图3中所示,然后打开如下图,图5:

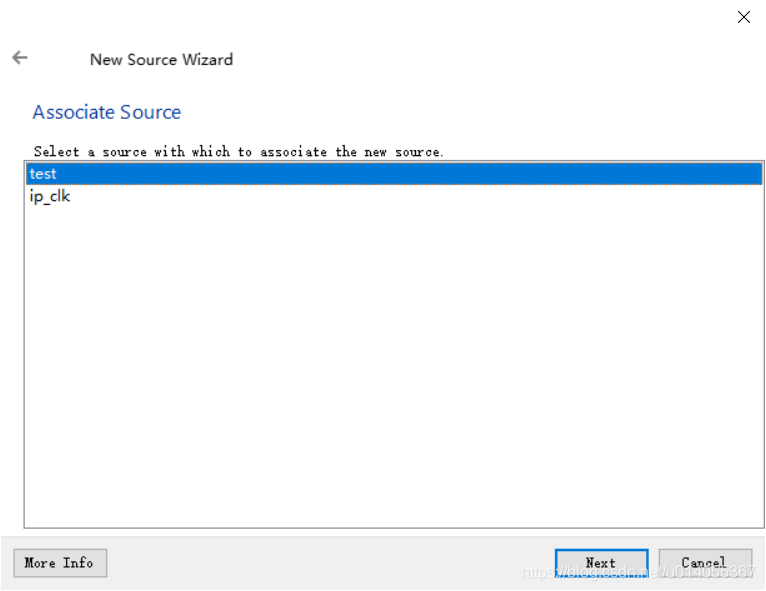

点击Next,出现如下图,图6所示的窗口:

这里例表中是你的工程中的文件目录,选择你工程的顶层文件,这里我的顶层文件时test,我选test,点击下一步,选择Finish,然后就把仿真文件添加完毕,里面添加自己的仿真代码,这里添加上我自己的仿真代码:

`timescale 1ns / 1ps

module test_tb;

// Inputs

reg clk_in;

reg rst_n;

// Outputs

wire clkout;

// Instantiate the Unit Under Test (UUT)

test uut (

.clk_in(clk_in),

.rst_n(rst_n),

.clkout(clkout)

);

initial begin

// Initialize Inputs

clk_in = 0;

rst_n = 0;

// Wait 100 ns for global reset to finish

#100;

end

always #20 clk_in=~clk_in;

endmodule

第三步 运行仿真

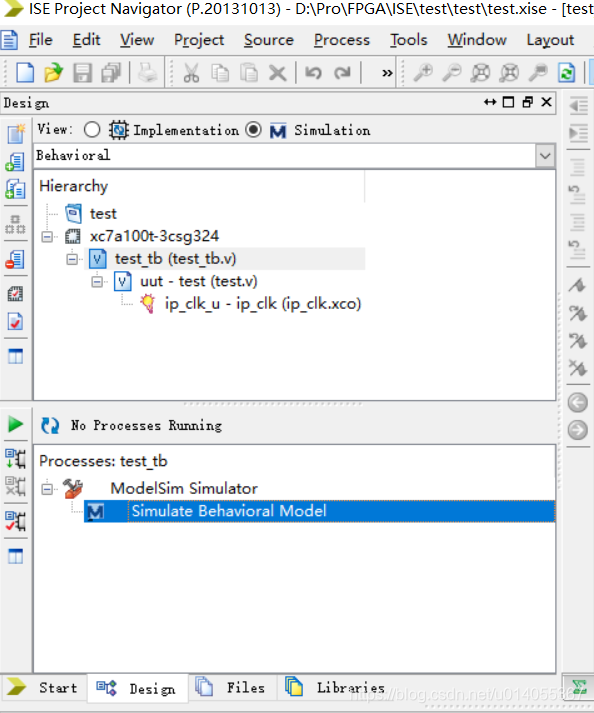

1、在Design工程窗口View项由Implementation更改为Simulation,则Design工程窗口中的顶层文件变为仿真文件名,我的仿真文件名是:test_tb,所以就变为如下图所示:图7

然后选中test_tb,双击下方的窗口中的Simulate Behavioral Model,然后就启动了Modelsim进行仿真了。

2、查看仿真结果

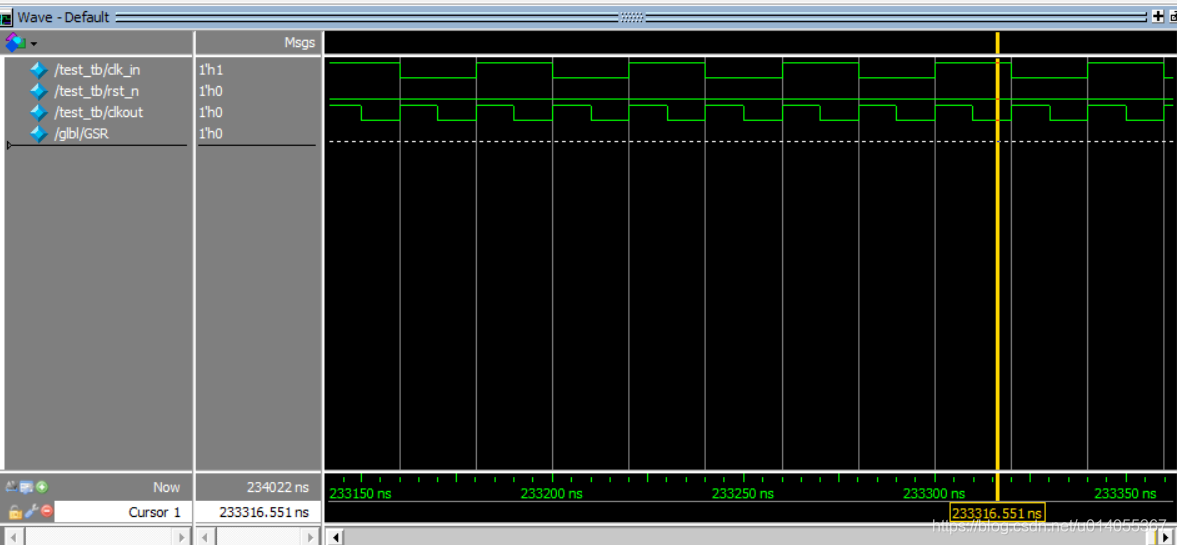

如下图所示:图8

可见输入时钟clk_in经过IP和倍频后,时钟输出clkout变为输入的两倍,实现了倍频。

1202

1202

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?