1. 引言

某客户使用 STM8AL 时,由于设计限制需使用 HSI 作为系统时钟。为减小 HSI 偏差,使用 LSE 对其进行校准。小批量试产发现 3%左右产品校准后频率和 16MHz 偏差较大。

2. 调研

检查客户代码,和 ST 官方提供的演示代码 STM8L15x_AN3101_FW_V1.1.0 一致,跟踪代码执行,未发现异常,初步排除代码移植问题。

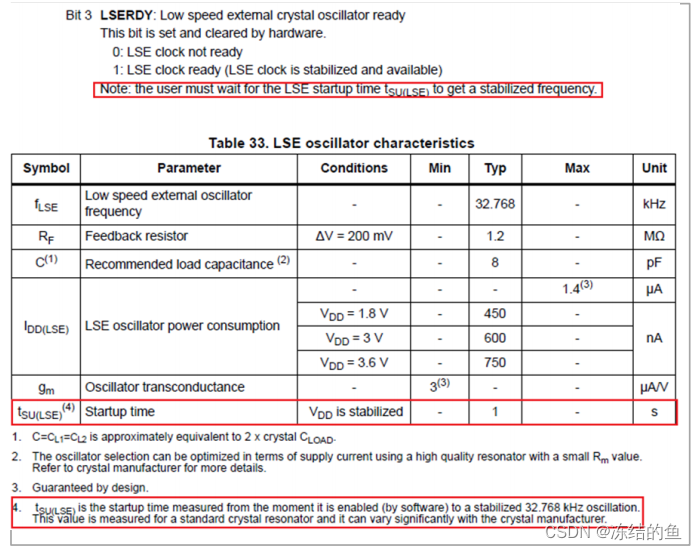

由于校验结果直接受 LSE 影响,查阅参考手册和数据手册可知,LSERDY 置位仅表示 LSE起振成功,LSE 震荡频率需要额外等待一段时间 tSU(LSE)才会稳定;不同晶振这个时间会有很大差异,详见图 1。

图1. 官方手册对 LSERDY 置位和 LSE 稳定的描述

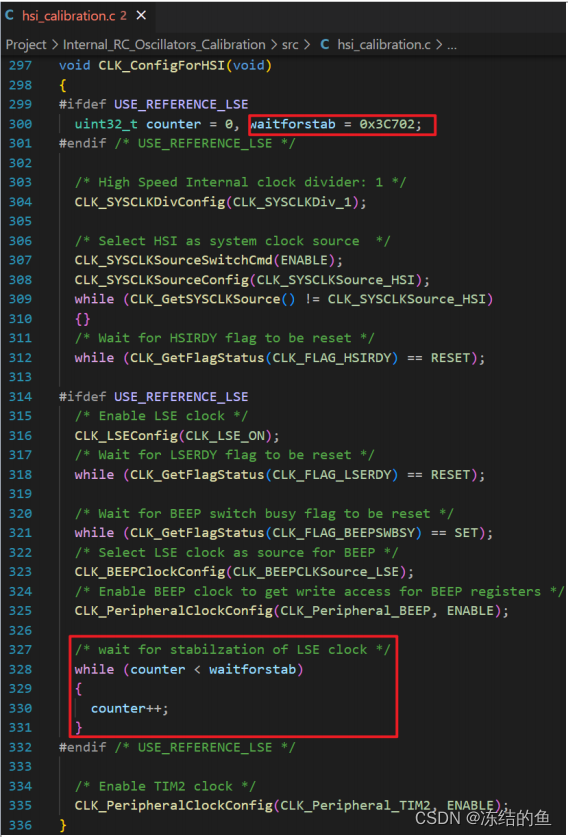

检查 ST 代码,发现这个延迟大约是 60ms,见图 2(循环一圈 4 条指令,CPU 频率按16MHz 计算,时间约 61.89ms)。经确认,ST 官方工程这个延迟是根据 ST 官方的开发板上安装的晶振设定的。由于客户使用的晶振型号不同,初步怀疑这个稳定时间需要调整。

图2. ST 官方代码里的延迟

3. 处理

将此延迟逐步增加到 90ms,保证 LSE 稳定下来。这样操作后,发现所有之前异常的板子校准结果都是好的。按此延迟再次加工一批板子,校准结果也是正常的。

4. 小结

当我们在应用中碰到跟时序相关问题时,最好先仔细阅读 MCU 数据手册、参考手册对相关模块特性的描述,并结合代码进行分析。

参考文献

本文档参考ST官方的《【应用笔记】LAT1407+通过LSE校准HSI偏差大的问题解决》文档。

参考下载地址:https://download.csdn.net/download/u014319604/89139817

8902

8902

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?