数字设计 FPGA 应用,第三章组合逻辑设计和 VIVADO 进阶,课程设计性质的作业题1

第一题:构建工程,实现 8 选 1 的数据选择器 74HC151,编写仿真代码进行测试,将该工程并生成 IP 核。(必须)

使用软件: Vivado

开发板: EGO1采用Xilinx Artix-7系列XC7A35T-1CSG324C FPGA

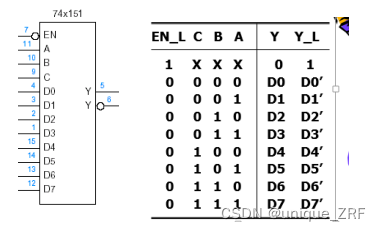

74HC151

151及其功能真值表

代码实现

1. verilog 代码

`timescale 1ns / 1ps

//

// Module Name: v_74hc151

// Revision 0.01 - File Created

// Additional Comments:

//

//

//文章有用的话记得给靓仔点个赞表示鼓励哟~

module v_74hc151(E_,S,D,Y,Y_);

/*

E_:使能

S[2]:选择

D[7]:输入

Y、Y_:输出

*/

input E_;

input[2:0] S;

input[7:0] D;

output Y,Y_;

reg Y=0;

reg Y_=1;

always @(E_ or S or D)

begin

if(E_ == 1)

begin

Y=0;

Y_=1;

end

else

begin

case (S)

0:Y=D[0];

1

本文详细介绍了如何使用Vivado设计8选1数据选择器74HC151,包括Verilog代码实现、仿真验证以及约束文件设置。在设计中,通过拨码开关控制使能E_、选择信号S和输入D,并用LED灯显示输出Y和Y_。最后,指导了如何在Vivado中创建并打包IP核。

本文详细介绍了如何使用Vivado设计8选1数据选择器74HC151,包括Verilog代码实现、仿真验证以及约束文件设置。在设计中,通过拨码开关控制使能E_、选择信号S和输入D,并用LED灯显示输出Y和Y_。最后,指导了如何在Vivado中创建并打包IP核。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6万+

6万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?